КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры, тактируемые фронтом

|

|

|

|

В цифровых микросхемах широко используются JK - и D - триггеры, синхронизируемые фронтом. Их структуру можно представить как последовательное соединение двух триггерных ячеек, управляемых уровнями напряжения. На рис. 6.13 в качестве примера представлены два варианта построения синхронизируемых фронтом D - триггеров, а на рис. 6.14 – временная диаграмма их работы.

а б

Рис. 6.13. Синхронизируемые фронтом D -триггеры:

а – на синхронизируемых уровнем 2-х D -триггерах,

б – на D - и RS -триггерах

Рис. 6.14. Временная диаграмма синхронизуемого фронтом D -триггера

Как видно из приведенной диаграммы рассмотренные D -триггеры синхронизируются отрицательным перепадом напряжения.

7. Цифровые ФУНКЦИОНАЛЬНЫЕ УЗЛЫ

ПОСЛЕДОВАТЕЛЬНОСТНОГО ТИПА

7.1. ИНТЕГРАЛЬНЫЕ СЧЕТЧИКИ

Счетчиком называется устройство, предназначенное для подсчета числа входных сигналов и хранения в определенном двоичном коде этого числа.

Счетчики – это цифровые автоматы, внутренние состояния которых определяются только количеством сигналов “1”, пришедших на вход. Сигналы “0” не изменяют их внутренние состояния.

Триггер Т -типа является простейшим счетчиком, который считает до двух. Счетчик, образованный цепочкой из m триггеров, сможет подсчитывать в двоичном коде 2 m входных импульсов. Каждый из триггеров в этой цепочке называют разрядом счетчика.

Основная характеристика счетчика – модуль счета, или емкость счетчика K сч .. Это количество поступивших входных сигналов, которое возвращает счетчик в исходное состояние.

Количество триггеров, необходимое для реализации счетчика, равно m =log2 K сч., где m – ближайшее большее целое число.

Классификация счетчиков

|

|

|

Цифровые счетчики классифицируются следующим образом:

· по модулю счета: двоичные, двоично-десятичные или с другим основанием счета, недвоичные с постоянным модулем счета, с переменным модулем счета;

· по направлению счета: суммирующие, вычитающие, реверсивные;

· по способу организации внутренних связей: с последовательным переносом, с параллельным переносом, с комбинированным переносом, кольцевые.

Классификационные признаки независимы и могут встречаться в различных сочетаниях: например, суммирующие счетчики бывают как с последовательным, так и с параллельным переносом и могут иметь двоичный, десятичный и иной модуль счета.

В суммирующем счетчике каждый входной импульс увеличивает число, записанное в счетчик, на единицу (для счетчиков с естественным порядком счета) и на единицу и более для счетчиков с произвольным порядком счета.

Вычитающий счетчик действует обратным образом: двоичное число, хранящееся в счетчике, с каждым поступающим импульсом уменьшается. Переполнение счетчика наступает при поступлении на его вход количества импульсов большего K сч..

Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Эти счетчики имеют дополнительные входы для задания направления счета.

Счетчики могут быть как асинхронными, так и синхронными.

Последовательные счетчики

Рассмотрим работу суммирующего двоичного счетчика (K сч. = 2 m) с естественным порядком счета и с K сч. = 8. Для его построения необходимо m =log28 = 3 триггера, что соответствует трем разрядам двоичного числа.

Таблица состояний такого счетчика имеет вид (табл. 7.1), причем входной сигнал xn обозначим через 1, Q 3 n – старший разряд, Q 1 n – младший разряд.

Таблица 7.1

| xn | Q 3 n | Q 2 n | Q 1 n | Q 3 n +1 | Q 2 n +1 | Q 1 n +1 |

Из анализа таблицы видно:

· триггер младшего разряда Q 1 переключается от каждого входного сигнала;

|

|

|

· второй разряд Q 2 переключается через два входных сигнала;

· третий разряд Q 3 переключается через четыре входных сигнала.

Таким образом, частота переключения каждого следующего триггера уменьшается вдвое. Следовательно, последовательный счетчик можно построить как цепочку последовательно включенных счетных триггеров.

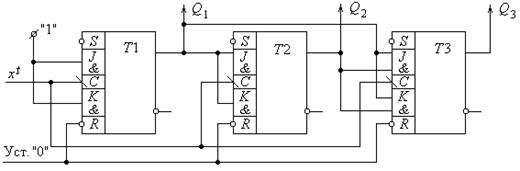

Построим такой счетчик на JK -триггерах, работающих в счетном режиме (рис. 7.1).

а

б

Рис. 7.1. Последовательный суммирующий счетчик на JK -триггерах – а;

временная диаграмма его работы – б

Данный счетчик может работать как вычитающий. Для этого необходимо сигналы на входы последующих разрядов подавать с инверсных выходов триггеров предыдущих разрядов.

Так как полученный счетчик – асинхронный, то каждый его триггер переключается с задержкой относительно входного сигнала. Поэтому по мере продвижения сигнала от младшего разряда к старшему эта задержка суммируется и может произойти искажение информации, в виде несоответствия числа уже поступивших в счетчик импульсов и кода на его выходах. В общем случае суммарная задержка пропорциональна числу триггеров и для устранения ее влияния на работоспособность счетчика приходится снижать частоту поступления входных импульсов, что снижает, в целом, быстродействие счетчика.

Счетчики с параллельным переносом

Для повышения быстродействия счетчики выполняются с параллельным (сквозным) переносом.

Их особенность заключается в том, что выходы всех предшествующих разрядов счетчика соединяются с входами триггера последующего разряда, поэтому длительность переходного процесса определяется только длительностью переходного процесса одного разряда и не зависит от количества триггеров.

Отсюда следует, что параллельные счетчики – синхронные.

Структура параллельного счетчика не столь очевидна, как структура последовательного счетчика, и для ее выявления необходима определенная процедура синтеза.

В качестве примера синтезируем двоичный параллельный счетчик с K сч. = 8.

Суммирующий счетчик. Процедура синтеза включает следующие операции:

1. Определяется необходимое количество разрядов m. В данном случае m = log2 8 = 3.

2. Строится таблица состояний счетчика. Для рассматриваемого примера возьмем таблицу 7.1.

|

|

|

3. Составляются карты переходов триггеров каждого разряда. Карта переходов размечается также как карта Карно, строится по таблице состояний и отображает переход триггера Qin → Qin +1 в каждом такте в зависимости от состояний остальных триггеров в такте n (рис. 7.2).

Для

| Для

| Для

| |||||||||||||||||

|

|

| |||||||||||||||||

|

|

| |||||||||||||||||

|

|

| |||||||||||||||||

Рис. 7.2. Карты переходов триггеров счетчика

Например, первой строке табл. 7.1  соответствует левая верхняя клетка карт переходов. Так как при поступлении первой единицы в счетчик Q 1 должен перейти из нулевого состояния в единичное, а Q 2 и Q 3 должны сохранить состояние нуля, в указанную клетку карты переходов для Q 1 следует поставить 01, а в картах для Q 2 и Q 3 поставить 00 и т.д.

соответствует левая верхняя клетка карт переходов. Так как при поступлении первой единицы в счетчик Q 1 должен перейти из нулевого состояния в единичное, а Q 2 и Q 3 должны сохранить состояние нуля, в указанную клетку карты переходов для Q 1 следует поставить 01, а в картах для Q 2 и Q 3 поставить 00 и т.д.

4. Выбирается тип триггера, например, JK -триггер, для построения счетчика. Используя матрицу переходов JK -триггера, для каждого входа триггера составляются карты Карно, в клетках которых проставляются сигналы, необходимые для обеспечения переходов триггеров, указанных в одноименных клетках карт переходов (рис. 7.3).

Рис. 7.3. Карты Карно функций входов триггеров счетчика

Например, для переходов 01 JK -триггера согласно его матрице переходов необходимо подать сигнал J = 1, а сигнал на входе K может быть любым (* – звездочка), поэтому в верхнюю левую клетку карты Карно для J 1 проставляют единицу, а для K 1 – звездочку и т.д.

5. Проводится минимизация логических функций входов в картах Карно с целью получения их аналитических представлений, показывающих связи между входами и выходами всех триггеров, составляющих счетчик.

В процессе минимизации производится доопределение функций там, где это целесообразно, единицами в клетках со звездочками.

|

|

|

В результате получаются следующие функции входов триггеров счетчика:

| J 1 = 1 J 2 = Q 1 J 3 = Q 1 Q 2 | K 1 = 1 K 2 = Q 1 K 3 = Q 1 Q 2 |

6. Строится электрическая схема счетчика, реализуя функции входов (рис. 7.4).

Рис. 7.4. Параллельный суммирующий двоичный счетчик с K сч. = 8

В качестве триггеров выбраны универсальные JK -триггеры (микросхема К155ТВ1), особенностью которых является наличие логики типа ЗИ на входах J и K и дополнительных R S входов с инверсным асинхронным управлением.

Вычитающий счетчик. Синтез вычитающего счетчика, работающего в соответствии с таблицей переходов обратной таблице 7.1, включает все рассмотренные выше процедуры и дает следующие функции входов:

J 1 = K 1 =1

J 2 = K 2 =

J 3 = K 3 =

.

.

Таким образом, вычитающий счетчик отличается от суммирующего тем, что сигналы на входы J и K последующих триггеров необходимо подавать с инверсных выходов триггеров предшествующих разрядов. Так как исходное состояние вычитающего счетчика – единицы во всех разрядах, то организуется общая шина установки по -входам.

-входам.

Реверсивный счетчик. Такой счетчик должен, в зависимости от сигналов управления, обеспечивать или режим суммирования, или режим вычитания входных сигналов.

Из сравнения функций входов, полученных ранее для суммирующего и вычитающего параллельных счетчиков с K сч. = 8, следует, что сами функции имеют один и тот же вид, только в случае вычитающего счетчика берутся инверсные значения переменных. Следовательно, реверсивный счетчик должен содержать схему управления, обеспечивающую подключение либо прямых, либо инверсных выходов ко входам последующих разрядов, в зависимости от сигналов управления направлением счета T.

Функция входов для реверсивного счетчика будет иметь вид:

K 1 = J 1 = 1,

J 2 = K 2 = TQ 1  ,

,

J 3 = K 3 = TQ 1 Q 2 ,

,

а его схема представлена на рис. 7.5.

Рис. 7.5. Реверсивный двоичный параллельный счетчик с K сч. = 8

Счетчик работает в режиме суммирования при T = 1 и в режиме вычитания при T = 0.

Недвоичные счетчики. Счетчик, имеющий K сч. ¹ 2 m, называется недвоичным. Состояния (2 m – K сч.) являются избыточными и исключаются внутри счетчика с помощью обратных связей. Задача синтеза таких счетчиков сводится к определению вида необходимых обратных связей и минимизации их числа.

Рассмотрим пример синтеза суммирующего счетчика с K сч. = 3.

1. Определяем необходимое количество триггеров:

.

.

Округляем m до двух.

2. Находим число избыточных состояний:

22 – 3 = 1.

3. Из числа возможных состояний счетчика исключим, например, состояние Q 1 = Q 2 = 1.

4. Строим таблицу переходов счетчика:

| x |

|

|

|

|

5. Составляем карты переходов триггеров счетчика, проставляя в клетках, соответствующим исключенным наборам, прочерк:

| Для Q 1 n ® Q 1 n +1 | Для Q 2 n ® Q 2 n +1 | |||||

| Q 2 | Q 2 | |||||

| Q 1 | – | Q 1 | – | |||

6. Выбираем тип триггеров (D -триггер). Используя матрицу переходов D -триггера и построенные карты переходов триггеров счетчика, строим карты функций входов триггеров:

Находим функции входов триггеров счетчика:

.

.

7. Строим схему счетчика (рис. 7.6):

Рис. 7.6. Параллельный недвоичный счетчик

с K сч. = 3 на D -триггерах

Как видно из схемы, исключение из состояний счетчика двоичного числа 11 достигается подачей сигналов с инверсных выходов первого и второго разрядов на вход первого разряда.

При использовании в счетчике триггеров JK -типа функции входов имеют вид:

J 1 = , J 2 = Q 1, K 1 = K 2 = 1,

, J 2 = Q 1, K 1 = K 2 = 1,

а его схема приведена на рис. 7.7:

Рис. 7.7. Параллельный недвоичный счетчик

с K сч. = 3 на JK -триггерах

Двоично-десятичные счетчики. Двоично-десятичные счетчики имеют K сч. = 10. Их синтезируют на основе четырехразрядного счетчика, исключая N = 2 m – K сч. = 24 – 10 = 6 избыточных состояний. Так как исключить можно любые 6 из 16 состояний, то общее число возможных схем построения таких счетчиков достигает приблизительно 76 × 106. В разных вариантах схем одному и тому же десятичному числу могут соответствовать различные кодовые комбинации, т. е. различные варианты счетчиков работают в различных двоично-десятичных кодах.

Особую форму составляют двоично-десятичные счетчики, работающие в самодополняющихся кодах, особенностью которых является соответствие обратных двоичных чисел обратным десятичным числам. Целесообразность такого соответствия очевидна, так как в ЭВМ операция вычитания заменяется операцией сложения кода уменьшаемого с обратным кодом вычитаемого. Примером самодополняющегося кода может быть следующий код (табл. 7.4):

Таблица 7.4

| Десятичное число | Двоичный код | Несамодпол- няющийся код | Самодопол- няющийся код |

| Q1 Q2 Q3 Q4 | |||

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | - - - - - - | - - - - - - |

Примечание: Обратный код числа x определяется по формуле (s -1) – x, где s – основание системы счисления.

Рассмотрим кодовую комбинацию 0110. В несамодополняю-

щемся коде ей соответствует десятичное число 6 (см. вторую и третью колонки табл. 7.4). Обратный код числа 6 равен 3, обратный код числа 0110 равен 1001. Коду числа 1001 в третьей колонке таблицы соответствует десятичное число 9, а не 3, т.е. самодополнения нет.

Для самодополняющегося кода комбинации 0110 соответствует десятичное число 4, обратный код которого равен 5 (вторая и четвертая колонки). Коду 1001 (т.е. обратному двоичному числу 0110) соответствует десятичное число 5 (т.е. обратное десятичному числу 4) в четвертой колонке, Таким образом, самодополняемость кодов выполняется.

Последовательность синтеза двоично-десятичных счетчиков не отличается от синтеза недвоичных счетчиков.

7.2. ЦИФРОВЫЕ РЕГИСТРЫ

Цифровыми регистрами называют устройства, функцией которых является хранение и преобразование многоразрядных двоичных чисел. Запоминающими элементами регистра являются триггеры, число которых равно разрядности хранимых чисел. Кроме триггеров регистры содержат также комбинационные схемы, предназначенные для ввода и вывода хранимых чисел, преобразования их кодов, сдвига кодов на то или иное число разрядов. Информация в регистрах хранится, как правило, в течение некоторого количества тактов.

Различают параллельные регистры (регистры памяти), последовательные регистры (регистры сдвига), параллельно-последовательные регистры (например, ввод в параллельном коде, вывод – в последовательном и наоборот).

В регистрах памяти число вводится (выводится) за один такт, а в регистрах сдвига – за m тактов, где m – разрядность чисел.

По способу ввода-вывода информации регистры подразделяются на однофазные и парафазные. В однофазных ввод (и вывод) производится только в прямом или только в обратном коде, в парафазных возможен ввод и вывод как в прямом, так и в обратном кодах.

В параллельных регистрах можно производить поразрядные логические операции с хранимым числом и вновь вводимым. Вид логических операций зависит от типа триггеров, составляющих регистр, и комбинации сигналов управления.

Регистры сдвига применяются для преобразования последова-

тельного кода в параллельный (и обратно), для умножения и деления многоразрядных чисел и т. д.

|

|

|

|

Дата добавления: 2014-01-15; Просмотров: 1667; Нарушение авторских прав?; Мы поможем в написании вашей работы!