КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Сложные команды начали выполняться с использованием аппаратных средств. Первые опыты применения арифметических микропроцессоров

Неудобная система прерываний. С учетом сказанного микропроцессоры от микроконтроллеров значительно продвинулись в своем развитии, прежде всего, по возможности увеличения адресуемого пространства.

Сложные арифметические операции выполнялись программно, т.е. нужно время.

При необходимости можно было увеличить в 2-4 раза, но это увеличение приводило к большим временным затратам.

Разрядность адреса не высока, разрядность данных (8,16).

1) Первый шаг был сделан за счет введения адресного сумматора, позволяющего формировать адрес на ША очень гибким способом. Адрес формировался как сумма содержимого нескольких внутренних регистров процессора: непосредственно адресного, смещения и сегментного и базового регистров. Причем последние складываются в сумматоре после сдвига в сторону старших на 4. За счет чего старшие разряды адреса идут, минуя сумматор. Адрес в ОЗУ может быть изменен содержанием любого из указанных регистров, т.е косвенная адресация позволяла легко перемещаться в адресном поле за счет только одной команды.

1) Первый шаг был сделан за счет введения адресного сумматора, позволяющего формировать адрес на ША очень гибким способом. Адрес формировался как сумма содержимого нескольких внутренних регистров процессора: непосредственно адресного, смещения и сегментного и базового регистров. Причем последние складываются в сумматоре после сдвига в сторону старших на 4. За счет чего старшие разряды адреса идут, минуя сумматор. Адрес в ОЗУ может быть изменен содержанием любого из указанных регистров, т.е косвенная адресация позволяла легко перемещаться в адресном поле за счет только одной команды.

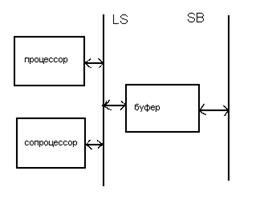

Примеры: К1810ВМ87 процессор заменяет основной при выполнении команд деления, умножения, требующих большого времени. Такие схемы назывались сопроцессорными. Локальная шина объединяет ША и ШД двух схем и

Примеры: К1810ВМ87 процессор заменяет основной при выполнении команд деления, умножения, требующих большого времени. Такие схемы назывались сопроцессорными. Локальная шина объединяет ША и ШД двух схем и  общие сигналы управления при получении кода длинной команды. Основной процессор блокируется, операция выполняется сопроцессором. Это направление получило распространение в системах требующих реализации длинных операций. Специализированные схемы, как правило, сочетали программную и аппаратную реализацию, что позволяло выполнять также операции за несколько тактов (5-6). Но это направление было оправдано, если в задачах постоянно встречались эти операции. В универсальных ВМ они встречались не столь часто, поэтому в них арифметический сопроцессор. Увеличение интеграции позволило разместить на кристалле большее число элементов и интегрировать сопроцессор в основной кристалл, либо сделать кристалл сопроцессора рядом с основным кристаллом. Это направление привело также к введению буферной памяти команд и данных в структурах микропроцессора.

общие сигналы управления при получении кода длинной команды. Основной процессор блокируется, операция выполняется сопроцессором. Это направление получило распространение в системах требующих реализации длинных операций. Специализированные схемы, как правило, сочетали программную и аппаратную реализацию, что позволяло выполнять также операции за несколько тактов (5-6). Но это направление было оправдано, если в задачах постоянно встречались эти операции. В универсальных ВМ они встречались не столь часто, поэтому в них арифметический сопроцессор. Увеличение интеграции позволило разместить на кристалле большее число элементов и интегрировать сопроцессор в основной кристалл, либо сделать кристалл сопроцессора рядом с основным кристаллом. Это направление привело также к введению буферной памяти команд и данных в структурах микропроцессора.

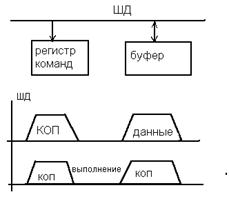

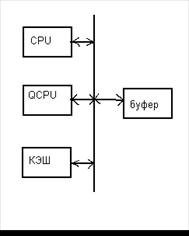

При передаче по ШД КОП и данных немало ситуаций, когда по шине ничего не передается, т.к. процессор выполняет текущую команду. Чтобы повысить производительность, предложено в «свободные окна» на ШД передавать коды следующих команд, расположенных по нарастанию адресов. Но для их хранения на кристалле нужна память, поэтому начали выполнять отдельный третий кристалл «кэш» память. Таким образом, микропроцессор стал состоять минимум из 3 частей. Такая конструкция размещается на посадочном месте в корпусе ИМС и коммутируется между собой локальной шиной в корпусе. Это же идея развита на кристалле основного, где дополнительно РОН выполняется буферная память данных с тем, чтобы снизить число обращений процессора во внешнюю память данных. Т.о. введение в буферной памяти команд и данных позволило заметно повысить производительность схемы. Команды загрузки выполняются традиционно, а процедуры преобразования – данные не выходят на ШД. Буферная память приводит к тому, что программа располагается сегментами. Переход внутри сегментов не проводит к смене содержимого буферной памяти. Выход за пределы сегмента – перезапись нового сегмента в буферную память команд. Разработаны схемы с коротким набором команд RISC микропроцессор. В них введет конвейерный подход к преобразованию. Одновременно несколько команд выполняются в различных фазах. Самая первая команда заканчивается –последняя, начинается. Те же команды разбиты на простые фрагменты.

Первые применения RISC архитектуры совмещались с традиционной. Структура RISC микропроцессоров более регулярна, но устройствам управления – сложнее.

6.5. Вычислитель на ОМП

|

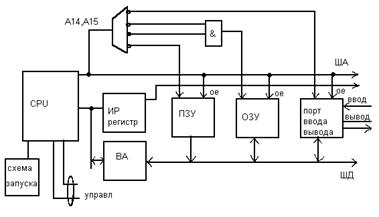

Вариации в структуре вычислителя возможны в организации ША и ШД. Так, например, ША формируется из старших разрядов по ША и младших по ШД. Чтобы адрес сохранялся, дополнительно введен регистр адреса, содержимое которого фиксируется по сигналу синхронизации. ШД сформирована через буфер данных (ВА) и двунаправлена. Управление буфером данных – сигналом запись/чтение процессора. Схемы ОЗУ, ПЗУ, порт In /Out выбираются адресными дешифраторами, поэтому при проектировании структуры все адресное пространство делят на области. Как правило самая большая – ОЗУ. Например: она занимает32К. Это половина из имеющегося адресного пространства. Рекомендуют размещать ее в верхней части карты памяти. При использовании микросхемы ОЗУ с информационной емкостью 16К, чтобы разделить дешифратором, необходимо определить число частей. В простейшем варианте всю область памяти делим на 4 равных части: 16К-ПЗУ, 16К- ПОРТ, 32К – ОЗУ. С этой целью используем дешифратор 2 в 4. На вход дешифратора подаем адресные сигналы А15,А14 – два старших разряда.

| А14 | А15 | |

| ПЗУ | ||

| Порт в/выв | ||

| ОЗУ | ||

| ОЗУ |

С соответствующих выходов дешифратора согласно таблице подаем сигналы на входы разрешение выборки кристалла. Для ОЗУ необходима схема И объединяющая два выхода дешифратора. Управляющие сигналы r/w берутся с выхода процессора либо с системного контроллера и подаются на соответствующие входы блоков. Возможна ситуация, когда объем ОЗУ ПЗУ превышает 64К. в этом случае рассматривается два адресных пространства: первое для ОЗУи ПЗУ, второе порты ввода/вывода. Переключение адресных пространств – сигналами контроллера – фаза выборки, чтение/запись и т.д.

В реальных схемах число порто I/Out может быть значительно, поэтому число областей в адресном пространстве 6-10.поэтому можно применить двойной дешифратор. Первый «грубый», у которого один выход обращения к ВУ, второй включается этим выходом и обеспечивает разделение с помощью младших разрядов адреса.

Для ОМП с общей шиной (К1801) необходимо сформировать адресные дешифраторы и адресные регистры на каждом функциональном блоке. Каждый блок имеет на входе адресный регистр с дешифрацией. Если адресное пространство его в регистр записывается – адрес и блок становится активными. Все остальные блоки не выбраны. Однокристальные микроЭВМ имеют в своем составе порты и некоторую память, поэтому структура контроллера отличается лишь блоком процессора. Способы подключения ВУ аналогичны. Контроллер на основе ОМП используют в промышленных системах управления, отображения информации ввода вывода. Их относительная черта – невысокая производительность, при несложных аппаратных затратах.

6.6. Структура на СМП

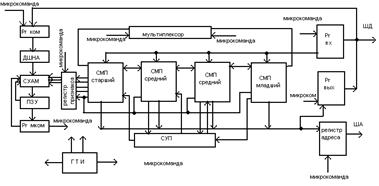

Основное отличие этой структуры в том, что процессор имеет более сложное построение чем в первом варианте. Это связано с тем, что необходимо обеспечить работоспособность секций и связь их между собой. Кроме этого блок микропрограммного управления также имеет

немалые аппаратные затраты. Четыре секции включены параллельно: младшая, старшая – по краям, на входе каждой секции поступает часть разрядов, например по четыре. Выходные разряды секций также комплексируются, обеспечивая выходную разрядность равную входной. ШД формируется двумя регистрами, входным и выходым. Причем, выходной регистр должен иметь третье состояние по выходу. ША формируется отдельным регистром, причем разрядность ее зависит от задания и может отличаться от разрядности шины данных.. Если разрядность ША<ШД используются младшие выходные разряды секции, если разрядность ША>ШД – он выводится из внутренних регистров секций за два такта, младшие и старшие части. В секциях нет отдельно выделенных регистров адреса, поэтому в качестве адресного применяют один из РОН-ов каждой секции. Между собою секции объединяются через выходы сдвиговых разрядов. Крайние выводы этих разрядов коммутируются через мультиплексор. С помощью отдельных разрядов микрокоманды мультиплексор настаивается на соответствующий тип сдвига: сдвиг влево или сдвиг вправо, логический, циклический или арифметический сдвиги, сдвиги операндов двойной длины.

Для организации ускоренного переноса используют блок ускоренного переноса (СУП). На ее выходы подключают сигналы распространения и генерации переноса. Выходы СУП – на входной перенос следующей секции. Одна такая схема работает с 4 секциями. Со старшей секцией снимают признаки, причем, признак Z объединяется со всеми секциями. Признаки хранятся в регистре.

Блок микропрограммного управления имеет типовую структуру. Управляющая часть – форматы микрокоманд распределяется между регистрами, мультиплексорными ключами, обеспечивая синхронизацию во времени. Непосредственно микрокоманды поступают на каждую секции параллельно. Одни и те же разряды на каждую секцию. Это схема позволяет выполнять операции как над одинарной длины так и над операндами.

|

|

Дата добавления: 2014-01-11; Просмотров: 309; Нарушение авторских прав?; Мы поможем в написании вашей работы!