КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Особенности архитектуры персональных электронных вычислительных машин типа IBM PC

|

|

|

|

Некоторые особенности мы рассмотрели по ходу изложения общих вопросов архитектуры ЭВМ. Другие особенности рассмотрим здесь, в этом параграфе.

Способы адресации информации. Всё множество способов адресации (способов вычисления эффективного адреса ЕА) можно представить в виде таблицы 2.1.

|

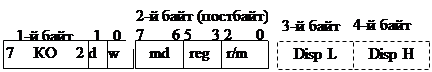

В качестве пояснения к таблице– формат первых 2–х байтов команды:

Бит d - указывает направление обмена (засылки результата операции) с регистром, номер которого указан в поле reg, т. е. задает схему выполнения команды:

[reg]:=[reg]*([EA]или[r/m]), если d=1 – запись результата в регистр,

[EA]:=[reg]*([EA]или[r/m]), если d=0 - из регистра в ячейку ОП.

Бит w - указывает длину операнда: w=0 - байт, w=1 - слово.

Второй байт (постбайт) - адресует участвующие в операции регистры (прямая адресация) или ячейки ОП при косвенной адресации.

Таблица 2.1

| R/m | Поле md | ||||

| W=0 | W=1 | ||||

| BX+SI+0 BX+DI BP+SI BP+DI | BX+SI+D8 BX+DI+D8 BP+SI+D8 BP+DI+D8 | BX+SI+D16 BX+DI+D16 BP+SI+D16 BP+DI+D16 | AL CL DL BL | BX CX DX BX | |

| SI+0 DI D16 BX | SI+D8 DI+D8 BP +D8 BX +D8 | SI+D16 DI+D16 BP +D16 BX +D16 | AH CH DH BH | SP BP SI DI | |

Поле md - задаёт режим адресации в соответствии с таблицей 2.1. Поле r/m задаёт режим адресации: 0,1,2,3 – индексно-относительная, 4,5 - индексная, 6,7 - относительная.

Формирование эффективного адреса ЕА представлено на рисунке 2.26.

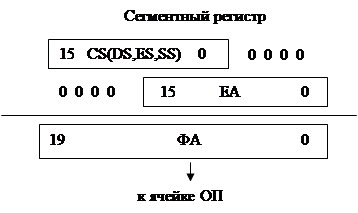

Эта схема (и таблица 2.1) действует в процессоре i8086 и обеспечивает формирование16-разрядного ЕА, т.е. адресацию только части ОП емкостью 216=64КВ. Однако фактическая (физическая) ёмкость ОП много больше. Как быть? Как её адресовать? В IBM PC на базе процессора i8086 для расширения адресного пространства ОП используют второй уровень относительной адресации - на базе так называемых сегментных регистров (16-разрядных): CS, DS, ES, SS. При этом вычисление ФА производится по схеме (рисунок 2.27). Этот 20-разрядный ФА обеспечивает адресацию ОП ёмкостью 1МВ=220В. Таким образом, в PC относительная адресация используется дважды: на пользовательском уровне (при формировании ЕА можно использовать базовые регистры ВХ, ВР) и на физическом уровне (можно использовать сегментные регистры CS, DS, ES, SS в качестве базовых регистров).

|

|

|

|

Рисунок 2.26

Память емкостью в 1МВ - это не много. Как увеличить ещё? В принципе для этого достаточно увеличить длину базового адреса, т.е. разрядность сегментных регистров. Как? В 1982 году появился МП i80286 - второе поколение 16-разрядных микропроцессоров (МП).

|

Рисунок 2.27

Этот МП обеспечивает возможность адресовать ОП ёмкостью 16МВ=224В. Этот процессор, а точнее, компьютер на его основе - т.е. ПЭВМ типа РС АТ, имеет возможность работы в двух режимах: в режиме реальной адресации, в котором он работает как i8086, и в т.н. защищённом режиме виртуальной адресации, в котором он обеспечивает адресацию 16МВ ОП, т.е. формирует адрес длиной m=24 разряда.

Как это делается, если сегментные регистры остались 16- разрядными? Путём использования виртуальной организации памяти, но не только с целью автоматизации свопинга, но и с целью расширения адресного пространства ОП и с целью защиты ОП.

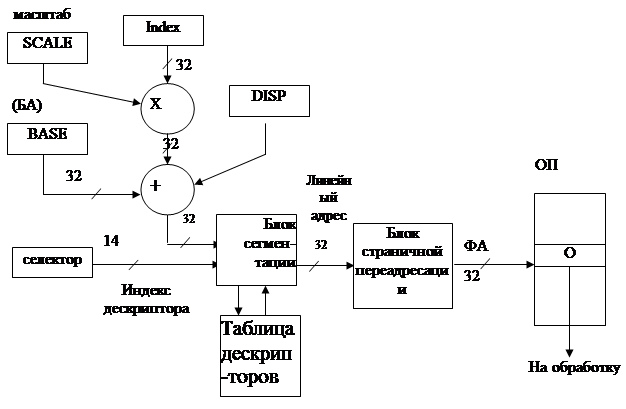

В защищённом режиме виртуальной адресации сегментные регистры CS и др. используются не для хранения базовых адресов сегментов, а для хранения т.н. селекторов сегментов (т.е. селекторов виртуальных страниц). По селекторам производится обращение к т.н. таблицам дескрипторов (которые фактически являются таблицей страниц - т.е. отображают состояние виртуальной памяти). В таблице дескрипторов каждой виртуальной странице (каждому сегменту) ставится в соответствие строка – дескриптор сегмента длиной 8 байтов, в котором и указывается более длинный физический базовый адрес сегмента (три байта), а также размер этого сегмента (в байтах) длиной 16 разрядов (2 байта). Таким образом, размер сегмента в защищённом режиме становится переменным: от 1В до 216В. В дескрипторе, в частности, указывают и уровень привилегий DPL сегмента и другие атрибуты сегмента, обеспечивающие защиту информации.

|

|

|

Схема вычисления ФА в этом случае имеет вид (рисунок 2.28):

Рисунок 2.28

Короткий эффективный адрес ЕА сохранился и в МП 80286. Это основной недостаток 16-разрядных МП (и компьютеров). Как быть? Переходить на 32-разрядные МП. Класс 32-разрядных процессоров (и компьютеров) был открыт в 1985 году МП i80386, в котором разрядность регистров, АЛУ, ША, ШД была увеличена скачком до 32. Адресное пространство ОП достигло 4ГВ=232В. В частности, схема вычисления ФА приобрела вид, представленный на рисунке 2.29. Как видно из рисунка, смещение DISP может достигать 4В и, следовательно, пользователь получил возможность выбирать размер сегмента в широких пределах - от 1В до 4ГВ, а не 64КВ, как было в 16- разрядных процессорах. Размер виртуального адресного пространства составляет 246В=64ТВ (32+14=46).

Рисунок 2.29

В IBM PC виртуальная организация памяти осуществляется за счёт использования таблиц дескрипторов. Использование дескрипторов позволяет решать следующие задачи: автоматизировать свопинг, т.е. собственно виртуальную организацию памяти, и расширить адресное пространство ЦП, увеличив длину базового адреса при длине сегментных регистров CS, DS,... в 16 разрядов, а также ввести гибкий механизм защиты информации, хранимой в сегментах, и других распределяемых ресурсов ЭВМ.

|

|

|

|

|

Дата добавления: 2014-01-11; Просмотров: 332; Нарушение авторских прав?; Мы поможем в написании вашей работы!