КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Послідовні лічильники

|

|

|

|

У лічильниках цього типу імпульси, що підраховуються, подаються тільки на вхід тригера молодшого розряду. Для кожного з наступних розрядів сигнали перемикання надходять з виходу попередніх розрядів. У результаті відбувається послідовне перемикання розрядів лічильника.

а

Q0

б Мал.15.4 Послідовний лічильник на Т-тригерах і його часові діаграми. |

Послідовні лічильники з модулем К = 2m звичайно реалізуються послідовним з’єднанням m Т-тригерів, кожний з яких працює як лічильник з К = 2. Структурна схема і часова діаграма послідовного підсумовуючого лічильника з К = 8 показані на мал. 15.4. При надходженні сигналу R = 1 відбувається скидання лічильника у початковий стан Q2Q1Q0 = 000. Подана схема буде працювати як віднімаючий лічильник, якщо вхід Тk кожного наступного (k-го) тригера підключити до прямого виходу Qk-1 попереднього тригера, а асинхронні входи Sа застосувати для установлення початкового числа. Реверсивний лічильник можна реалізувати, підключивши до лічильного входу кожного тригера елемент І-АБО-НІ, виконуючий функцію

Послідовні лічильники з модулем К = 2m звичайно реалізуються послідовним з’єднанням m Т-тригерів, кожний з яких працює як лічильник з К = 2. Структурна схема і часова діаграма послідовного підсумовуючого лічильника з К = 8 показані на мал. 15.4. При надходженні сигналу R = 1 відбувається скидання лічильника у початковий стан Q2Q1Q0 = 000. Подана схема буде працювати як віднімаючий лічильник, якщо вхід Тk кожного наступного (k-го) тригера підключити до прямого виходу Qk-1 попереднього тригера, а асинхронні входи Sа застосувати для установлення початкового числа. Реверсивний лічильник можна реалізувати, підключивши до лічильного входу кожного тригера елемент І-АБО-НІ, виконуючий функцію

Тk = МQk-1 MQk-1,

Тk = МQk-1 MQk-1,

де М – керуючий сигнал: М = 1 - додавання, М = 0 - віднімання.

Недоліком послідовних лічильників є відносно низька швидкодія, оскільки для встановлення відповідного числа на виходах потрібне послідовне перемикання усіх m тригерів. Тому максимальна робоча частота лічильника у m разів менше максимальної частоти перемикання тригера.

Для підвищення швидкодії послідовних лічильників використовується прискорене формування сигналів переносу між розрядами. Як можна бачити з діаграм на мал.15.4,б, сигнал переносу Тk+1 = 1, перемикаючий (k+1)-й тригер, утворюється у попередньому k-му тригері при QkТk = 1. Тому якщо у внутрішній структурі k-го тригера є точка, де функція QkТk утворюється раніше, ніж змінюється стан його виходу, цю точку можна використати для отримання сигналу Тk+1. Приклад застосування цього принципу ілюструється на мал.15.5, де показаний один розряд, реалізований на тригері, що побудований за схемою із забороняючими зв’язками. Відокремлення кіл переносу Тk від вихідних кіл Qk підвищує також стійкість роботи таких лічильників завдяки вилученню впливу завад, виникаючих у вихідних колах.

|

|

|

4 8 Tk+1 4 8 Tk+1

Мал.15.5. Формування прискореного переносу. |

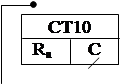

Якщо є лічильник з модулем К, то отримати лічильник з будь-яким потрібним модулем К’ < К можна, вилучивши К – К’ робочих станів. Для цього зручно використати асинхронні входи Rа тригерів для встановлення початкового стану лічильника. Наприклад, якщо у чотирьохрозрядному лічильнику з К = 16 вилучити стани S10 – S15, то утворюється декадний лічильник. Стани S10 – S15 стають нештатними, якщо при установленні будь-якого з них на входи Rа усіх тригерів надходить сигнал R = 1, що скидає лічильник у S0. Після мінімізації функції R(Q3, Q2, Q1, Q0) можна переконатися, що R = Q3 (Q2 Q1) = Q3 Q2Q1. Ця функція реалізується елементом І-АБО-НІ, після вмикання якого між виходами Q3, Q2, Q1 тригерів і спільним входом їх асинхронного скидання R утворюється декадний лічильник.

Аналогічним чином можна побудувати лічильники і зі змінним модулем перерахування, коли значення модуля визначається зовнішньою змінною.

Аналогічним чином можна побудувати лічильники і зі змінним модулем перерахування, коли значення модуля визначається зовнішньою змінною.

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

2-а декада 1-а декада

Мал.15.6. Каскадне з’єднання декадних лічильників. |

Для отримання великих значень К найчастіше використовують каскадне з’єднання лічильників. На мал.15.6 показаний приклад каскадування декадних лічильників. Якщо кожна з декад являє собою паралельний лічильник, що перемикається від’ємним фронтом сигналу, то подана схема є паралельно-послідовним лічильником з К = 100. Такі лічильники мають вищу швидкодію, ніж послідовні, і не вимагають вмикання додаткових логічних елементів, як паралельні лічильники.

Генератори кодів

Генератором кодів (числових послідовностей) називається вузел, утворюючий на виходах подану послідовність кодів (двійкових чисел).

Послідовносні вузли цього типу називають також розподільниками сигналів (імпульсів), оскільки утворена на їх виходах послідовність двійкових чисел часто використовується як послідовність сигналів, керуючих роботою інших вузлів. Кількість станів генератора називається довжиною послідовності чисел Lп, яка визначається як кількість тактів машинного часу (періодів синхросигналів), після якої послідовність чисел на виході генератора повторюється. За своєю структурою генератори кодів близькі або до лічильників, або до регістрів.

Генератори на основі лічильників

Будь-який лічильник можна розглядати як генератор послідовності чисел, довжина якої дорівнює модулю перерахування Lп = К. Наприклад, лічильник з модулем К = 8 є генератором послідовності чисел 0, 1, …, 7.

При розробці структури генератора треба враховувати, що потрібна кількість розрядів (тригерів) генератора дорівнює кількості двійкових розрядів m у числах, що генеруються. Якщо m > log2Lп, для зменшення кількості тригерів структура генератора дещо змінюється. У цьому випадку генератор доцільно будувати у вигляді лічильника з модулем К = Lп і підключати до його виходів комбінаційну схему, реалізуючу потрібні значення двійкових чисел.

а б Мал.15.7. Генератор кодів на основі лічильника (а) та його часові діаграми (б). |

Приклад генератора послідовності чисел 3, 2, 12, 8 і часова діаграма його роботи подані на мал.15.7. Оскільки Lп = 4, то за основу генератора обрано двохрозрядний паралельний лічильник з модулем К = 4, на виходах Q0, Q1 якого утворюється послідовність 0, 1, 2, 3. Підключення до виходів лічильника вихідної комбінаційної схеми забезпечує отримання потрібної послідовності кодів.

Генератори на основі зсувних регістрів

Такі генератори (їх ще називають кільцевими) застосовуються для отримання циклічних послідовностей чисел, у яких кожне наступне число утворюється шляхом зсуву попереднього числа, записаного у регістрі, на один розряд і уведенням у звільнений перший розряд 0 чи 1. Для цього до входу першого розряду регістра підключається комбінаційна схема, утворююча необхідний керуючий сигнал. Прикладом кільцевого генератора, на виході якого утворюється послідовність 0, 1, 3, 7, 6, 4, є лічильник Джонсона на мал.7.

Якщо є m-розрядний зсувний регістр, то можна генерувати циклічні послідовності довжиною Lп 2m. На мал.15.8,а показаний граф станів трьохрозрядного регістра із зсувом ліворуч, де відображені усі можливі переходи при уводі у перший розряд значень Z0 = 0 i Z0 = 1. Як можна бачити з мал.15.8,а існує багато послідовностей чисел, що реалізуються за допомогою регістру. Одній з таких послідовностей 0, 1, 3, 7, 6, 5, 2, 4 відповідає граф станів, показаний на мал.15.8,б, відповідною таблицею станів є табл.15.1. Склавши карту Карно для функції Z0, після мінімізації можна отримати

Якщо є m-розрядний зсувний регістр, то можна генерувати циклічні послідовності довжиною Lп 2m. На мал.15.8,а показаний граф станів трьохрозрядного регістра із зсувом ліворуч, де відображені усі можливі переходи при уводі у перший розряд значень Z0 = 0 i Z0 = 1. Як можна бачити з мал.15.8,а існує багато послідовностей чисел, що реалізуються за допомогою регістру. Одній з таких послідовностей 0, 1, 3, 7, 6, 5, 2, 4 відповідає граф станів, показаний на мал.15.8,б, відповідною таблицею станів є табл.15.1. Склавши карту Карно для функції Z0, після мінімізації можна отримати

Z0 = Q0Q2 Q1Q2 Q0Q1Q2.

Z0 = Q0Q2 Q1Q2 Q0Q1Q2.

Застосувавши D-тригери для побудови регістру і логічний елемент І-АБО-НІ, отримуємо схему генератора (мал.15.9).

На основі зсувних регістрів відносно просто будуються керовані генератори, утворюючі різні послідовності кодів залежно від комбінації зовнішніх керуючих сигналів. Іншою перевагою циклічних генераторів є використання зсувного регістра, побудованого на однотипних тригерах, завдяки чому суттєво спрощується топологічне проектування генератора і зменшується потрібна площа кристалу.

|

|

|

Однак генератори на основі регістрів утворюють тільки циклічні послідовності чисел. У такій послідовності кожний наступний елемент утворюється шляхом зсуву попереднього і довільним вибором значення одного розряду. Для реалізації довільних нециклічних послідовностей потрібно застосовувати додатковий комбінаційний перетворювач кодів, що вмикається на виході генератора. При цьому основні параметри генератора (швидкодія, потужність, площа кристалу) дещо погіршуються.

1 0

б

Мал.15.8 Графи переходів: трьохрозрядного регістру із зсувом праворуч (а) та генератора кодів (б). |

Q0 Q1 Q2 Q0 Q1 Q2

С Мал.15.9. Логічна схема генератора кодів. |

Генератори кодів широко застосовуються у пристроях керування, де вони формують послідовності сигналів, керуючі роботою різних вузлів та блоків. При цьому кожний з генерованих кодів являє собою мікрокоманду, що викликає виконання певної мікрооперації вузлами та блоками системи. Послідовність кодів забезпечує виконання послідовності мікрооперацій, які у сукупності виконують певну процедуру перетворення двійкової інформації. Керовані генератори кодів (КГК) забезпечують реалізацію певного набора процедур, кожна з яких виконується при подаванні певних керуючих сигналів, утворюючих відповідну команду. Таким чином, на базі КГК можна реалізувати пристрій керування (ПК) цифрової системи. Такі ПК називають апаратно реалізованими. Вони забезпечують почергове виконання послідовності команд – програми, що надходить із запам’ятовуючого пристрою або від зовнішнього пристрою.

Якщо алгоритм функціонування системи уявити у вигляді послідовності виконання мікрооперацій, то її ПК можна побудувати на базі звичайного генератора кодів – мікрокоманд. Такий ПК, реалізуючий фіксований алгоритм керування, називається контролером (чи мікроконтролером) із жорсткою логікою керування. Ці контролери використовуються для реалізації відносно нескладних алгоритмів керування. Для виконання складніших алгоритмів частіше використовують програмне керування, що можна забезпечити за допомогою апаратно реалізованого ПК на базі КГК.

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 1375; Нарушение авторских прав?; Мы поможем в написании вашей работы!

R

R

1 2 3 4 5 6 7 8 9

1 2 3 4 5 6 7 8 9

Т

Т

Q0 t

Q0 t

Q1 t

Q1 t

Q1 t

Q1 t

Q2 t

Q2 t

t

t

&

&

& & Qk

& & Qk

1 &

1 &

Тk 3 7

Тk 3 7

5

5

& & Qk

& & Qk

& &

& &

2 6

2 6

9

9

Т

Т

R

R

C0

C0

C t

C t

C2 C1

C2 C1

C C2 t

C C2 t

0 1

0 1

0

0

0 1 0 1

0 1 0 1

0 1

0 1

0 1 1 1

0 1 1 1

0 0 1 0 1

0 0 1 0 1

1 0

1 0

а

а