КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Сумматоры

|

|

|

|

Сумматорами называются логические устройства, выполняющие операцию сложения двух чисел. В зависимости от способа обработки чисел различают последовательные и параллельные сумматоры. Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В таких устройствах сложение двух чисел производится поразрядно последовательно во времени. Параллельные сумматоры строят, как правило, на основе композиции одноразрядных суммирующих схем, причем обработка чисел в таких устройствах производится одновременно во всех разрядах. Логическое проектирование в этом случае сводится к синтезу одноразрядных сумматоров и организации цепей переноса в соответствии с заданными требованиями на быстродействие [5].

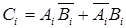

Одноразрядные суммирующие схемы различают по числу входов. Рассмотрим синтез одноразрядных суммирующих схем на два входа аi и Bi: эти схемы часто называются полусумматорами или сумматорами по модулю 2. Выходными сигналами такого устройства являются сумма Сi и перенос Пi, который при суммировании по модулю 2 не используется. Работа полусумматора может быть задана таблицей истинности (таблица 2.6), в соответствии с которой функции выходов Сi и Пi могут быть записаны в виде:

; Пi = AiВi. (2.15)

; Пi = AiВi. (2.15)

Таблица 2.6 – Таблица истинности полусумматора

| Аi | Bi | Ci | Пi | |

При построении сумматоров на ИС обычно ставится задача оптимального проектирования для удовлетворения требования максимального быстродействия и обеспечения минимального количества однотипных логических элементов. Быстродействие устройств на ИС в основном определяется задержкой логических элементов НЕ. Поэтому для получения максимального быстродействия сумматоров необходимо проектировать схему с минимальным числом последовательно соединенных элементов НЕ. Отсюда предпочтительным при построении комбинационных схем с максимальным быстродействием является функционально избыточный базис И-ИЛИ-НЕ.

|

|

|

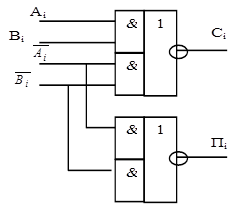

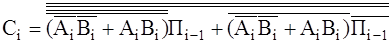

Рассмотрим реализацию полусумматора на логических элементах И-ИЛИ-НЕ. Для этого представим выражение для переключательной функции в виде структурного уравнения:

Сi =  ;

;  . (2.16)

. (2.16)

Схемное решение для этой функции с учетом цепи образования переноса показано на рисунке 2.31.

Поскольку коэффициент разветвления по выходу логического элемента И внутри интегральных схем, как правило, не превышает единицы, то при реализации переключательной функции Пi для однотипности применяется элемент И-ИЛИ-НЕ, в котором в силу использования только одного входа элементов И выполняется функция ИЛИ-НЕ. Тогда функция Пi может быть представлена структурным уравнением:

Пi =  . (2.17)

. (2.17)

Рисунок 2.31 – Полусумматор на элементах И-ИЛИ-НЕ

Одноразрядные полные суммирующие схемы (сумматоры на три входа) предназначены для образования выходных сигналов суммы С i и переносаПi по сигналам на входеAi, Bi, Пi-1. Закон функционирования такого полного сумматора определяется таблицей истинности (таблица 2.7).

Таблица 2.7 – Таблица истинности полного сумматора

| Аi | Bi | Пi-1 | Ci | Пi | |

| 0 | |||||

| 0 | |||||

| 0 | |||||

| 1 | |||||

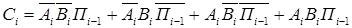

По этой таблице может быть составлено выражение для переключательных функций Сi и Пi в СДНФ:

; (2.18)

; (2.18)

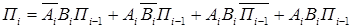

. (2.19)

. (2.19)

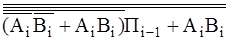

Эти уравнения можно представить в виде структурных формул, удобных для реализации на логических элементах И-ИЛИ-НЕ. Для удовлетворения требования минимальных аппаратурных затрат используют метод минимизации схем. С этой целью преобразуют выражения так, чтобы обеспечить максимально возможное число общих членов. Структурное уравнение суммы представляется в следующем виде:

|

|

|

; (2.20)

; (2.20)

Пi =  . (2.21)

. (2.21)

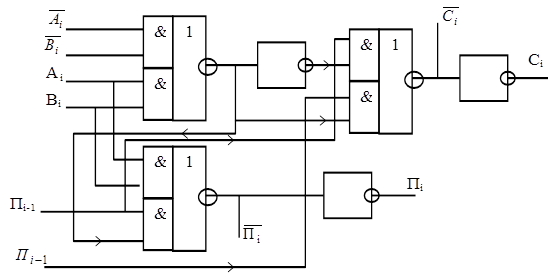

Схема, реализующая данные функции, представлена на рисунке 2.32. Быстродействие сумматора определяется временем задержки трех элементов НЕ.

Методы построения параллельных сумматоров на основе каскадного соединения одноразрядных полных сумматоров: р азличают параллельные комбинационные сумматоры с последовательным, одновременным и комбинированным переносом. Выбор типа переноса между разрядами суммирующего устройства определяется требованиями к его быстродействию.

Рисунок 2.32 – Схема полного сумматора в базисе И-ИЛИ-НЕ

Сумматоры с последовательным переносом имеют сравнительно низкое быстродействие, определяемое временем суммирования при сложении двух n -разрядных чисел. На входы каждой одноразрядной схемы сумматора поступают два слагаемых и перенос из предыдущего разряда. Каждый одноразрядный сумматор вырабатывает сумму и перенос в следующий разряд. Сигнал переноса, образованный в младшем разряде, распространяется последовательно по цепям переноса к старшим разрядам. Поэтому время распространения переноса определяется суммарной задержкой этих цепей.

С целью повышения быстродействия применяют сумматоры с одновременным переносом. У них время распространения переноса не зависит от числа разрядов и определяется только временем задержки схемы переноса. В качестве недостатка сумматоров с одновременным переносом следует отметить значительный рост аппаратурных затрат при построении схем межразрядных переносов, что практически ограничивает возможность такого метода реализации сумматоров. Сложность цепей переноса определяет допустимое число разрядов в таких сумматорах.

В сумматорах с комбинированным переносом полные одноразрядные сумматоры объединяются в группы. Внутри группы, как правило, осуществляется одновременный перенос. Между группами перенос может быть как последовательный, так и одновременный. Организация переноса в комбинационных n -разрядных сумматорах с комбинированным переносом позволяет проектировать схемы, отвечающие предъявляемым требованиям к быстродействию и приемлемые в отношении аппаратурных затрат.

|

|

|

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 2235; Нарушение авторских прав?; Мы поможем в написании вашей работы!