КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Постоянные запоминающие устройства

|

|

|

|

Постоянные ЗУ (ПЗУ) осуществляют хранение и выдачу постоянно записанной информации, содержание которой не изменяется во время работы системы. Это используемые в процессе работы стандартные подпрограммы и микропрограммы, табличные значения различных функций, константы и др.

Микросхемы ПЗУ принято делить на три класса: ПЗУ маcочные, программируемые изготовителем по способу заказного фотошаблона (маски); ПЗУ, программируемые пользователем по способу пережигания плавких перемычек (ППЗУ), и репрограммируемые ПЗУ, допускающие многократное перепрограммирование их пользователем (РПЗУ). Между ними есть существенные различия в способе программирования, т.е. занесения в них информации, и обращения с ними при применении.

В ПЗУ запоминающие элементы объединяются в двухкоординатную матрицу п ´ N, образованную при пересечении N входных слов и n выходных (разрядов) информационных шин. В местах пересечения совокупностей п ´ N включены запоминающие элементы (ЗЭ), несущие информацию «1» или «0». В качестве ЗЭ используют диоды, биполярные транзисторы, МДП-структуры, аморфные полупроводники (АП) и др.

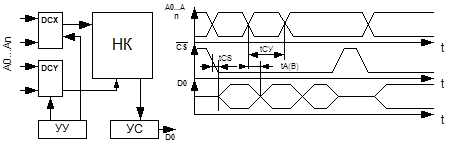

По структуре полупроводниковые ПЗУ состоят из следующих узлов: массива элементов памяти (накопитель), блока адресной выборки (дешифратор адреса: ДСХ – дешифратор строк, ДСУ – дешифратор столбцов) и устройства управления (УУ) (рис. 7.1)

Рис.7.1

В таблице 7.1 приведены основные сигналы ЗУ.

Таблица 7.1

| Наименование сигнала | Обозначение | ||

| Международное | Отечественное | МЭК* | |

| Адрес Тактовый сигнал Адрес столбца Строб адреса столбца Цикл Входные данные Данные вход-выход Сигнал разрешения Сигнал обнуления (стирания) Сигнал разрешения по выходу Выходные данные Сигнал информации Сигнал считывания Адрес строки Строб адреса строки Сигнал регенерации Сигнал запись-считывание Сигнал считывание-запись Выбор микросхемы Сигнал записи | А С СА CAS CY DI DIO (DI/DO) СЕ ЕР CEO DO D RD RA RAS REF WR/RD(W/R) RD/WR CS WR | A Т CA CAS Ц Uвх. и Uвх. и /Uвых. и Р УСТ0 - Uвых. и U СЧ RA RAS PЕГ ЗП/СЧ СЧ/ЗП ВМ ЗП | А С СА CAS С D DO Е ЕR G Q D R RA RAS RF WR RW S W |

* МЭК - международная электротехническая комиссия.

|

|

|

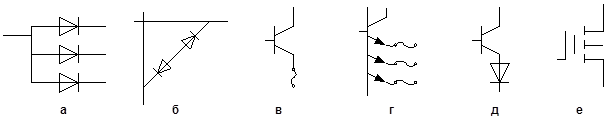

На рис. 7.2 изображены схемы основных ЗЭ на основе которых paзрабатываются ПЗУ, ППЗУ. Для ПЗУ с накопителем на ЗЭ (рис. 7.2, а, е) запись информации осуществляется двумя способами: изменением конфигурации металлизированной разводки (фотошаблоны) или селективным вскрытием контактных окон под металлизацию (лазерным лучом). Для ППЗУ ЗЭ (рис. 7.2, в, г) программируются пережиганием плавких перемычек, а ЗЭ - (рис. 7.2, б, д) программируются путем избирательного разрушения диодов. В РПЗУ возможна полная перезапись информации или же частичное селективное изменение хранимой информации в отдельных ЗЭ.

Рис. 7.2

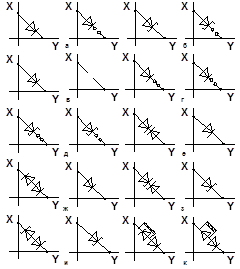

ЗЭ на диодах располагается в местах пересечения токоведущих шин (рис. 7.3). Информация в такой ЗЭ записывается в двоичном коде, причем логическая «1» соответствует наличию диодав пересечении матрицы, а логический «0» - отсутствию диода (или наоборот). В ПЗУ информация заносится изготовлением диодной Матрицы (ДМ) металлизацией с помощью фотошаблонов или контактных окон (рис. 7.3, б) и лазерным лучом (рис. 7.3,в). В ППЗУ информация заносится посредством пережигания плавких перемычек (рис. 7.3, г, д)и восстановлением связей в ЗЭ пробоем (рис. 7.3, е - и) или закорачиванием одного из взаимно (обратно) включенных диодов (рис. 7.3, к).

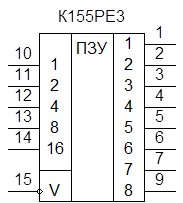

Рис. 7.3 Рис. 7.4

Структуру рассмотренного типа имеют ИС ПЗУ серий К155, K555, предназначенные для применения в генераторах символов русского алфавита (К155РЕ21), латинского алфавита (К155РЕ22), цифр и арифметических знаков (К155РЕ23), дополнительных знаков (К155РЕ24), алфавитно-цифровых символов (К155РЕ4). Условное обозначение ПЗУ на микросхеме К155РЕ3 приведено на рис. 7.4.

|

|

|

Программируемые постоянные запоминающие устройства

Микросхемы ППЗУ во многом похожи на ИС ПЗУ масочного типа, в частности имеют схожее устройство, но допускают программирование, тоже однократное, самим пользователем. Для реализации этой возможности в структуре ИС предусмотрены специальные устройства, включенные на выходах и обеспечивающие формирование тока программирования. Микросхема ППЗУ выпускается с целыми металло-пленочными перемычками из легкоплавкого материала, например нихрома, с низким сопротивлением. Наличие перемычки соответствует напряжению низкого (лог.0) или высокого (лог.1) уровня в зависимости от выходного усилителя: при инверсном выходе-лог.0, при прямом - лог.1.

Выходы усилителей считывания инверсные, поэтому наличие перемычек соответствует заполнению матрицы нулями. Программирование заключается в пережигании перемычек в тех местах, т.е. в тех “ элементах памяти”, где нужно записать 1.

На этапе подготовки следует проверить ИС на наличие нулей во всех ЭП, подавая на адресные входы последовательно все адресные наборы и контролируя состояния выходов устройством контроля.

После программирования следует проверить состояние всех ЭП и при необходимости повторить цикл программирования.Более надежным является программирование серий импульсов длительностью 25…50 мкс, скважностью 10 и фронтом 0,3…3 мкс. Для реализации этих условий требуется программатор с автоматическим формированием программирующих импульсов.

Для программирования ИС ППЗУ, у которых в исходном состоянии в матрице записаны 1 (при наличии у усилителей считывания прямы выходов), необходимо изменить режим на этапе подготовки: выходы такой ИС перед программированием должны быть подключены к источнику напряжения 5В.

Разновидностью ППЗУ являются программируемые выжиганием плавких перемычек логические матрицы (ПЛМ), выполненные по ТТЛШ-технологии, К556РТ1 иК556РТ2, имеющие идентичные характеристики и конструктивные параметры, но отличающиеся типом выхода: у первой ИС выход с открытым коллектором, у второй - на три состояния.

|

|

|

Программируемые логические матрицы (ПЛМ) как и ППЗУ относятся к программируемым ИС двухступенчатой структуры, состоящей из двух последовательных матриц «Матрица И - матрица ИЛИ». ПЛМ отличается от ППЗУ тем, что в ППЗУ матрица И жесткая, а матрица ИЛИ программируемая, а в ПЛМ oбe матрицы И и ИЛИ программируемые. Второе отличие, состоит в том, что на ПЛМ можно реализовать не любую систему переключательных функции, как на ППЗУ, а лишь удовлетворяющую дополнительному ограничению: длина дизъюнктивных нормальных форм воспроизводимых функцией не должна превышать числа переходных цепей между матрицами И и ИЛИ.

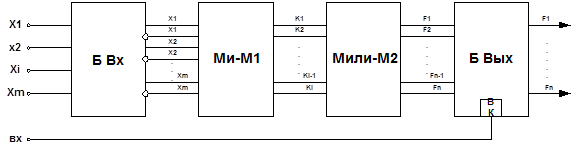

Структурная схема ПЛМ (рис. 7.5),состоит из входных и выходных буферных каскадов БВx., БВых.и матрицы элементов И и ИЛИ. (МИ - М1, МИЛИ - М2). Входные буферы разгружают входные цепи и преобразуют однофазные входные сигналы в парафазные. Выходные буферы обеспечивают необходимую нагрузочную способность ПЛМ и стробируют ее с помощью входа выборки кристалла ВК, сигнал на котором либо разрешает работу ПЛМ, либо переводит выходы в состояние «Отключено», Основными параметрами ПЛМ являются число входов m, число переходных ценой (термов) l и число выходов п. Структура матрицы И и ИЛИ состоит из горизонтальных и вертикальных шин, в узлах пересечения которых находятся элементы связи (ЭС), которые при программировании вводятся пли устраняются (рис. 7.6,а). В качестве ЭС могут служить рассмотренные ЗЭ, например, диоды в матрице Ми (рис. 7.6,б) и транзисторы в матрице Мили (рис. 7.6, в).

|

Рис. 7.5

Рис.7.6

ПЛМ широко используются как в ППЗУ для реализации переключательных функций Fn преобразования кодов, так и в качестве управляющей памяти ЭВМс микропрограммным управлением. Следует отметить, что ППЗУ реализует наиболее развернутые формы представления функций (СДНФ) и для них не используется минимизация функций. Для ПЛМ реализуемую систему функций следует минимизировать. Для построения автоматов с памятью к ПЛМ добавляют триггеры (регистры).

|

|

|

Оперативные запоминающие устройства

Оперативные ЗУ (ОЗУ) выполняют запись, хранение и считывание произвольной двоичной информации, обеспечивают хранение программ для текущей обработки информации и массивов обрабатываемых данных.

По способу хранения информации ОЗУ делят на статические и динамические. ЗЭ статических ЗУ представляют собой бистабильные элементы и обеспечивают считывание информации без ее разрушения. В динамических ЗУ для хранения информации используются инерционные свойства реактивных элементов (конденсаторов), что требует периодического постановления (регенерации) состояния ЗЭ памяти в процессе хранения информации. При регенерации производится перезапись каждого хранимого в ЗУ бита либо в тот же ЗЭ, либо в соседний, в последнем случае информация циклически сдвигается на один разряд с каждым циклом регенерации.

В накопителях статических ОЗУ применяются триггерные элементы памяти, в накопителях динамических ОЗУ - однотранзисторные ЗЭ, состоящие из ключевого транзистора и емкости хранения информации. Вследствие постоянного рассасывания заряда, хранящегося на емкости, такой ЗЭ требует периодической регенерации информации, которая выполняется с помощью устройства управления.

Типичный пример триггерного ОЗУ – параллельный регистр. Организация памяти в виде отдельных регистров применяется при создании ОЗУ малой емкости.

При увеличении емкости ОЗУ возникает проблема доступа к каждому элементу памяти при ограниченном числе выводов корпуса. Эта задача решается с помощью адресной организации ЗУ с использованием дешифратора кода адреса (тогда, например, при 4 входах можно организовать обращение к 24=16 элементам памяти, при 10 входах – к 1024 элементам и т.д.).

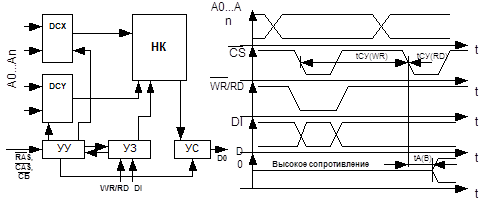

Запоминающие устройства адресного типа состоит из трех основных блоков: массива элементов памяти (накопитель), блока адресной выборки (дешифратор адреса: ДСХ – дешифратор строк, ДСУ – дешифратор столбцов) и устройства управления (УУ) (рис. 7.7)

Рис. 7.7

Рис. 7.7

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 786; Нарушение авторских прав?; Мы поможем в написании вашей работы!