КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Статическая и динамическая оперативная память. Оперативные запоминающие устройства

|

|

|

|

Оперативные запоминающие устройства

Режим удвоенной скорости

Пакетный режим

Пакетный режим (Burst Mode) — режим, при котором на запрос по конкретному

адресу память возвращает пакет данных, хранящихся не только по этому адресу,

но и по нескольким последующим адресам.

Разрядность ячейки памяти современных ВМ обычно равна одному байту, в то

время как ширина шины данных, как правило, составляет четыре байта. Следова-

тельно, одно обращение к памяти требует последовательного доступа к четырем смеж-

ным ячейкам — пакету1. С учетом этого обстоятельства в ИМС памяти часто использу-

ется модификация страничного режима, носящая название группового или пакетного

режима. При его реализации адрес столбца заносится в ИМС только для первой ячей-

ки пакета, а переход к очередному столбцу производится уже внутри микросхемы.

Это позволяет для каждого пакета исключить три из четырех операций занесения

в ИМС адреса столбца и тем самым еще более сократить среднее время доступа.

Важным этапом в дальнейшем развитии технологии микросхем памяти стал ре-

жим DDR (Double Data Rate) — удвоенная скорость передачи данных. Сущность

метода заключается в передаче данных по обоим фронтам импульса синхрониза-

ции, то есть дважды за период. Таким образом, пропускная способность увеличи-

вается в те же два раза.

Помимо упомянутых используются и другие приемы повышения быстродей-

ствия ИМС памяти, такие как включение в состав микросхемы вспомогательной

кэш-памяти и независимые тракты данных, позволяющие однов

Большинство из применяемых в настоящее время типов микросхем оперативной

памяти не в состоянии сохранять данные без внешнего источника энергии, то есть

|

|

|

являются энергозависимыми (volatile memory). Широкое распространение таких

устройств связано с рядом их достоинств по сравнению с энергонезависимыми

типами ОЗУ (non-volatile memory): большей емкостью, низким энергопотребле-

нием, более высоким быстродействием и невысокой себестоимостью хранения еди-

ницы информации.

Энергозависимые ОЗУ можно подразделить на две основные подгруппы: ди-

намическую память (DRAM — Dynamic Random, Access Memory) и статическую

память (SRAM — Static Random Access Memory).

В статических ОЗУ запоминающий элемент может хранить записанную инфор-

мацию неограниченно долго (при наличии питающего напряжения). Запоминаю-

щий элемент динамического ОЗУ способен хранить информацию только в течение

достаточно короткого промежутка времени, после которого информацию нужно

восстанавливать заново, иначе она будет потеряна. Динамические ЗУ, как и стати-

ческие, энергозависимы.

Роль запоминающего элемента в статическом ОЗУ исполняет триггер. Такой

триггер представляет собой схему с двумя устойчивыми состояниями, обычно со-

стоящую из четырех или шести транзисторов (рис. 5.7). Схема с четырьмя транзи-

сторами обеспечивает большую емкость микросхемы, а следовательно, меньшую

стоимость, однако у такой схемы большой ток утечки, когда информация просто

хранится. Также триггер на четырех транзисторах более чувствителен к воздей-

ствию внешних источников излучения, которые могут стать причиной потери ин-

формации. Наличие двух дополнительных транзисторов позволяет в какой-то мере

компенсировать упомянутые недостатки схемы на четырех транзисторах, но, глав-

ное — увеличить быстродействие памяти.

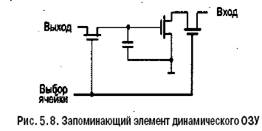

Запоминающий элемент динамической памяти значительно проще. Он состо-

ит из одного конденсатора и запирающего транзистора (рис. 5.8).

|

|

Наличие или отсутствие заряда в конденсаторе интерпретируется как 1 или О

|

|

|

соответственно. Простота схемы позволяет достичь высокой плотности размеще-

ния ЗЭ и, в итоге, снизить стоимость. Главный недостаток подобной технологии

связан с тем, что накапливаемый на конденсаторе заряд со временем теряется. Даже

при хорошем диэлектрике с электрическим сопротивлением в несколько тераом

(1012 Ом), используемом при изготовлении элементарных конденсаторов ЗЭ, за-

ряд теряется достаточно быстро. Размеры у такого конденсатора микроскопичес-

кие, а емкость имеет порядок 10-15 Ф. При такой емкости на одном конденсаторе

накапливается всего около 40 000 электронов. Среднее время утечки заряда ЗЭ

динамической памяти составляет сотни или даже десятки миллисекунд, поэтому

заряд необходимо успеть восстановить в течение данного отрезка времени, иначе

хранящаяся информация будет утеряна. Периодическое восстановление заряда ЗЭ

называется регенерацией и осуществляется каждые 2-8 мс.

В различных типах ИМС динамической памяти нашли применение три основ-

ных метода регенерации:

• одним сигналом RAS (RОR — RAS Only Refresh);

• сигналом CAS, предваряющим сигнал RAS(CBR — CAS Before RAS);

• автоматическая регенерация (SR — Self Refresh).

Регенерация одним RAS использовалась еще в первых микросхемах DRAM.

|

|

|

|

|

Дата добавления: 2014-01-14; Просмотров: 1146; Нарушение авторских прав?; Мы поможем в написании вашей работы!