КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Комп’ютери з довгим форматом команди

|

|

|

|

Раніше розглянуті суперскалярні процесори характеризуються високою продуктивністю при забезпеченні безконфліктного виконання команд. Але це вимагає значних додаткових затрат обладнання. На рис. 5. 25 показано кристал суперскалярного процесора МІРБ1110000, на якому позначені вузли процесора та виділено апаратні засоби пристрою керування, які забезпечують невпорядковане виконання команд. Видно, що ці засоби зайняли більше 30 відсотків площі кристала.

Рис. 5.25. Кристал суперскалярного процесора MIPS R10000, на якому позначені вузли процесора та виділено засоби керування невпорядковатш виконанням команд

Розглянемо далі архітектури комп’ютерів, у яких відсутні конфлікти команд. До них, зокрема, належать комп’ютери з довгим форматом команди

Архітектура комп’ютерів з довгим форматом команди (КДФК), англійський еквівалент VLIW (Very Long Instruction Word), бере свій початок від паралельного мікрокоду, що застосовувався в комп ютерах CDC6600 і IBM 360/91. У 70-х роках багато комп’ютерних систем оснащувалися додатковими векторними процесорами обробки сигналів, що використовували довгий формат команди. Зокрема, до таких процесорів належали процесори АР-120В, AP-190L та інші фірми FPS.

Першими універсальними комп’ютерами з архітектурою КДФК стали міні-супер- комп ютери, випущені на початку 1980-х років компаніями MultiFlow, Culler і Cydrome, але вони не мали комерційного успіху. Наприклад, комп’ютер компанії MultiFlow 7/300 використовував два арифметико-логічні пристрої для цілих чисел, два арифметико-логічні пристрої для чисел з рухомою комою і блок логічного галуження. Його 256-роз- рядний довгий формат команди містить поля для восьми 32-розрядних команд. В цих комп’ютерах були використані планувальник обчислень і програмна конвеєризація, які є основою технології компілятора КДФК

|

|

|

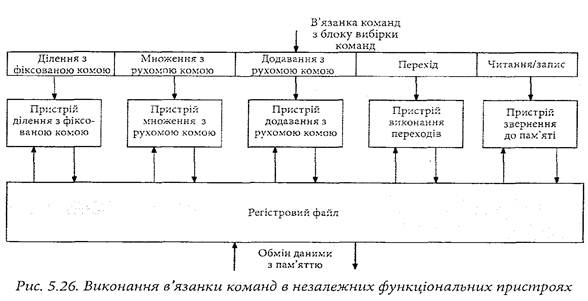

Архітектура КДФК передбачає наявність багатьох незалежних функціональних пристроїв. Для забезпечення паралельного виконання декілька команд пакуються в один пакет, який в подальшому будемо називати в язанкою команд, та поступають на виконання. В’язанка команд може включати, наприклад, команди над числами з фіксованою та рухомою комою, команду звернення до пам’яті та команду переходу, як це показано на рис. 5.26. Така в’язанка команд матиме набір полів команд для кожного функціонального пристрою, що призводить до кратного збільшення її довжини порівняно з однією командою. Як видно з рисунка, кожне з цих полів керує відповідним функціональним пристроєм, а обмін даними між пристроями здійснюється через інтегрований багатопортовий регістровий файл.

Завдання ефективного планування паралельного виконання команд в комп’ютері з довгим форматом команди повністю лягає на компілятор. Компілятор з послідовності команд початкової програми генерує в’язанку команд шляхом проглядання програми як в межах, так і за межами лінійних ділянок програми без галужень. Для забезпечення коректності виконання операцій компілятор має бути здатним визначати можливість появи конфліктів при виконанні команд. У певних ситуаціях, коли компілятор не може зробити заключення, що конфлікт не відбудеться, наприклад, у випадку звернення до масиву, коли індекс обчислюється під час виконання програми, операції не можуть плануватися для паралельного виконання. Відповідно це призводить до зниження продуктивності.

Компілятор визначає ділянку програми без циклів, яка стає кандидатом для формування в’язанки команд. Для збільшення розміру тіла циклу широко використовується методика розкручування циклів, що призводить до утворення великих фрагментів програми, що не містять зворотних дуг.

|

|

|

Якщо виконанню підлягає програма, що має тільки переходи вперед, компілятор робить евристичний прогноз вибору умовних гілок. Шлях, що має найбільшу вірогідність виконання (його називають трасою), використовується для оптимізації, що проводиться з врахуванням конфліктів за даними між командами і обмежень за апаратними ресурсами. Під час планування генерується в’язанка команд. Всі команди, які входять до в’язанки команд, видаються одночасно і виконуються паралельно. Після обробки першої траси планується наступний шлях, що має найбільшу вірогідність виконання (попередня траса більше не розглядається). Процес пакування команд послідовної програми у в’язанки команд продовжується до тих пір, поки не буде оптимізована вся програма.

Ключовою умовою досягнення ефективної роботи комп’ютера з довгим форматом команди є коректний прогноз вибору умовних гілок. Відмічено, наприклад, що прогноз умовних гілок для наукових програм часто виявляється точним. Повернення назад є у всіх ітераціях циклу, за винятком останньої. Таким чином, прогноз буде коректний в більшості випадків. Інші умовні гілки, наприклад, гілка обробки переповнення і перевірки граничних умов (вихід за межі масиву), також є надійно передбачуваними.

З погляду архітектурних ідей комп’ютер з довгим форматом команди можна розглядати як розширення архітектури комп’ютера з простою системою команд, оскільки тут також довжина команди є сталою, апаратні ресурси плануються статично, та віддається перевага програмному вирішенню конфліктів.

В архітектурі комп’ютера з довгим форматом команди, крім того, принцип заміни керування під час виконання програми на планування під час компіляції поширений і на систему пам’яті. Для забезпечення зайнятості конвеєрних функціональних пристроїв тут необхідна пам’ять з високою пропускною спроможністю. Одним із сучасних підходів до збільшення пропускної спроможності пам’яті є використання розшарування пам’яті, причому можливі конфлікти доступу до пам’яті визначає спеціальний модуль компілятора модуль запобігання конфліктам

Таким чином, розпаралелювання у комп’ютерах з довгим форматом команди виконується виключно на етапі компіляції під час формування в язанок команд, тобто статично. Так як неможливо наперед передбачити розв’язання усіх видів залежностей, відкомпільовані програми вимагають ретельного налагоджування. Негативно впливають також ефекти невпорядкованого завершення виконання команд. Саме тому надійність виконання програми тут зменшена порівняно з суперскалярним варіантом архітектури комп’ютера. Тобто, цей підхід дозволяє досягти максимуму продуктивності, але є прийнятним лише у певних застосуваннях комп’ютерних засобів. Перевага КДФК в потенційній продуктивності найбільш відчутна в серверних задачах, де паралельно опрацьовують декілька процесів (ниток), в наукових задачах, задачах тривимірної візуалізації та в задачах обробки сигналів (де, зокрема, застосовуються процесори ADSP21XX фірми Analog Devices та TMS320C6X фірми Texas Instruments, які належать до вказаної архітектури).

|

|

|

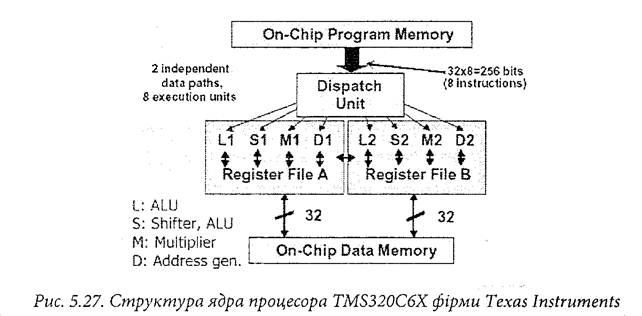

Архітектуру КДФК запроваджено у новітніх процесорах Alpha фірми DEC та LA-64 фірми Intel. Останній процесор оптимізовано для виконання серверних задач Як приклад на рис. 5.27 приведено структуру ядра процесора TMS320C6X фірми Texas Instruments, в якому використано довгий формат команди. В’язанка команд цього процесора складається з восьми 32-розрядних команд. Тут використано два тракти обробки даних А та В, кожний з яких має по 4 функціональні блоки та свій багатопортовий регістровий файл.

Тракти обробки даних А і В є однотипними та мають в своєму складі наступні функціональні пристрої: L - АЛП, S - пристрій зсуву та АЛП, М - перемножувач, D - формувач адрес пам’яті. В’язанка команд зчитується з пам’яті команд (On-Chip Program Memory) та поступає до блоку диспетчеризації (Dispatch Unit), який здійснює розподіл команд у відповідні функціональні пристрої.

|

|

|

|

|

Дата добавления: 2014-11-25; Просмотров: 648; Нарушение авторских прав?; Мы поможем в написании вашей работы!