КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры с D -управлением

|

|

|

|

Наиболее часто в цифровых интегральных микросхемах, а также в импульсных устройствах применяют триггеры с единственным входом данных D (data), так называемые D-триггеры.

Одна из причин их появления была в том, что число выводов у корпусов микросхем ранних разработок не превышало 14, а стоимость многовыводного корпуса составляла значительную часть от стоимости готовой микросхемы. Для D-триггера требуется всего четыре внешних вывода: вход данных D, тактовый вход С, два выхода Q и  (один из них может отсутствовать). Схема D-триггера (рис. 2.34, а) отличается от схемы RST-триггера (рис. 2.29, б) наличием инвертора DD1.1, добавленного между входами S и R. Теперь состояние неопределенности для входов R и S исключается, так как инвертор DD1.1 формирует на входе R сигнал

(один из них может отсутствовать). Схема D-триггера (рис. 2.34, а) отличается от схемы RST-триггера (рис. 2.29, б) наличием инвертора DD1.1, добавленного между входами S и R. Теперь состояние неопределенности для входов R и S исключается, так как инвертор DD1.1 формирует на входе R сигнал  .

.

Рис. 2.34 - Триггер со входом D

Согласно таблице логических состояний D-триггера (рис. 2.34, б) в некоторый момент времени tn на вход D можно подать напряжения низкого или высокого уровня. Если в последующий момент tn+1 придет положительный перепад тактового импульса, состояния на выходах Qn+1 и  будут соответствовать табл. 2.34, б.

будут соответствовать табл. 2.34, б.

На рис. 2.34, в показаны диаграммы записи в D-триггер напряжений высокого и низкого входных уровней и их считывание. Непременное условие правильной работы D-триггера — это наличие защитного интервала времени после прихода запускающего импульса UD перед тактовым UC (интервал времени tn+1-tn оговаривается справочными данными на D-триггер).

Рисунок 2.35 - Счетчик-делитель на 2: а - структурная схема; б - применение D-триггера для деления на 2

Если снабдить D-триггер цепью обратной связи, соединяющей выход  со входом D, он станет работать как Т-триггер, т. е. делитель частоты в 2 раза (счетчик). Действительно, нетрудно видеть, что делитель на рис. 2.35, а по фазировке сигналов соответствует Т-триггерному, рассмотренному на рис. 2.30, а. На рис. 2.35, б показаны осциллограммы работы делителя на два частоты тактовой последовательности UC.

со входом D, он станет работать как Т-триггер, т. е. делитель частоты в 2 раза (счетчик). Действительно, нетрудно видеть, что делитель на рис. 2.35, а по фазировке сигналов соответствует Т-триггерному, рассмотренному на рис. 2.30, а. На рис. 2.35, б показаны осциллограммы работы делителя на два частоты тактовой последовательности UC.

|

|

|

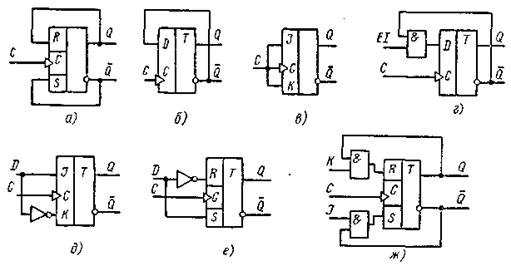

а - из RS в Т; б - из D в Т; е — из JK в Т; г — Т-триггер со входом разрешения Е1; д - JK в D; е - RST в D; ж - RST в JK

Рисунок 2.36 - Схемы взаимного преобразования триггеров

|

|

|

|

|

Дата добавления: 2014-11-18; Просмотров: 785; Нарушение авторских прав?; Мы поможем в написании вашей работы!