КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Дешифраторы

|

|

|

|

Линейный или одноступенчатый дешифратор. Дешифратор - это комбинационное устройство, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. Обычно, указанный в схеме номер вывода дешифратора соответствует десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в качестве входных переменных, вернее сказать, что при подаче на вход устройства параллельного двоичного кода на выходе дешифратора появится сигнал на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода. Отсюда следует то, что в любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора. В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического 0 (при этом на всех остальных выходах уровень логической 1). В дешифраторах каждой выходной функции соответствует только один минтерм, а количество функций определяется количеством разрядов двоичного числа. Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором (в качестве примера неполного дешифратора можно привести дешифратор двоично-десятичных чисел).

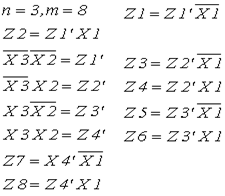

Рассмотрим пример синтеза дешифратора (полного) 3 ® 8, следовательно, количество разрядов двоичного числа - 3, количество выходов - 8.

Таблица состояний дешифратора

| Х3 Х2 Х1 | Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7 |

| 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 | 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 |

7Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции (рис. 2.9).

|

|

|

Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m)и m элементов отрицания.

Пирамидальные дешифраторы. Пирамидальные дешифраторы позволяют реализовать схему на базе только двухвходовых элементов логического умножения (конъюнкции). Рассмотрим пример реализации дешифратора 3®8

Для построения такого дешифратора потребуется 12 двухвходовых элементов 2И и три инвертора. Пирамидальные дешифраторы при больших количествах входных переменных позволяют несколько упростить конструкцию устройства, т.е. уменьшить количество интегральных микросхем.

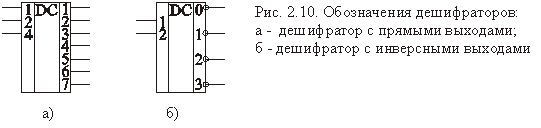

Промышленностью стран СНГ, в том числе и России, выпускаются различные модификации дешифраторов в интегральном исполнении. Обозначение дешифраторов на принципиальных схемах показано на рис. 2.10.

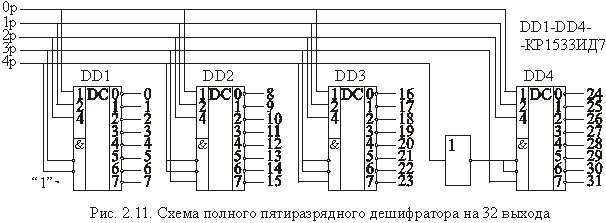

Двухступенчатые дешифраторы на интегральных микросхемах. Пример дешифратора для пятиразрядного двоичного кода. Каждый дешифратор выполнен с управляющими входами, объединенными конъюнктивно. При выполнении условия конъюнкции на выходе, номер которого соответствует десятичному эквиваленту двоичного кода, появится уровень логического “0”. В противном случае все выходы находятся в состоянии логической единицы (рис.2.11). Как следует из рис. 2.11, пятиразрядный дешифратор, имеющий 32 выхода, выполнен на базе четырех дешифраторов с использованием лишь одного дополнительного инвертора, что достигнуто благодаря наличию входной управляющей логики каждой интегральной микросхемы. Нетрудно заметить, что входная логика дешифраторов КР1533ИД7 позволяет реализовать функцию дешифратора 2®3 без дополнительных элементов, а полного дешифратора 2®4 с использованием одного инвертора.

|

|

|

|

|

Дата добавления: 2014-12-08; Просмотров: 674; Нарушение авторских прав?; Мы поможем в написании вашей работы!