КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Исследование основных логических элементов и комбинационных устройств

|

|

|

|

Лабораторная работа №2

Литература:

1. А.А. Коваленко, М.Д. Петропавловский. Основы микроэлектроники: Учебное пособие. ‑ Барнаул: Изд‑во БГПУ, 2005. – 222 с.

2. В.С. Ямпольский Основы автоматики и ЭВТ. – М.: Просвещение. - 1991. - §3.1 ‑3.4

3. Лекции

4. Руководство к выполнению виртуальных лабораторных работ с помощью программы моделирования электрических схем Electronic Workbench 5.12

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию.

- В каждом из 10 заданий выделить из приведенной схемы цифрового автомата узел, содержащий только логические элементы, и изобразить его принципиальную схему, используя УГО российского стандарта

- Смоделировать работу каждой схемы средствами Electronic Workbench и составить таблицу истинности исследуемого устройства

- Определить логическую функцию исследуемого устройства и привести его условное графическое изображение (УГО)

- В каждом задании составить дополнительно две схемы реализации той же логической функции на элементах 2И-НЕ (элемент Шеффера) и элементах 2ИЛИ-НЕ (элемент Пирса), используя минимальное количество вентилей

- В задании 11 по аналогии с предыдущими схемами дополнить приведенное устройство схемой узла, позволяющего подавать на входы Х1¸Х3 произвольную комбинацию логических сигналов и индицировать состояние каждого входа и выхода. Исследовать работу схемы аналогично предыдущим заданиям

Отчет к каждому заданию лабораторной работы оформлять по образцу, приведенному в ПРИЛОЖЕНИИ 1.

|

|

|

При защите работы уметь объяснить каждый из полученных результатов.

ПРИЛОЖЕНИЕ 1

Фрагмент отчета (на примере одного задания)

Задание 1.

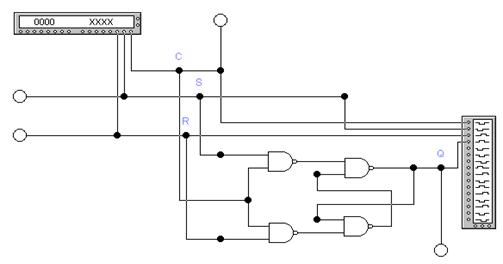

Пример схемы, приведенной в задании.

В таком виде перерисовывать её не нужно!

Фрагмент отчета по данному заданию приводится ниже.

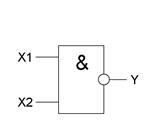

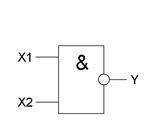

Задание 1: выполняемая схемой функция ‑ «2И-НЕ»

Схема: УГО: Таблица истинности:

«2И-НЕ» на элементах Шеффера. «2И-НЕ» на элементах Пирса.

ПРИЛОЖЕНИЕ 2

УГО и таблицы истинности некоторых логических элементов

1. Элемент «2И-НЕ»

2. Элемент «2ИЛИ-НЕ»

3. Элемент «исключающее ИЛИ»

ПРИЛОЖЕНИЕ 3

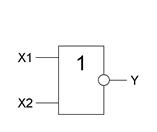

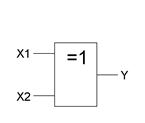

Примеры условных графических обозначений логических элементов по ГОСТ (российский стандарт) и ANSI (American National Standard Institute)

| УГО по ANSI | УГО по ГОСТ | Функциональное назначение |

|

| «2И» (2-Input AND Gate) |

|

| «3И» (3-Input AND Gate) |

|

| «2И-НЕ» (2-Input NAND Gate) |

|

| «2ИЛИ» (2-Input OR Gate) |

|

| «2ИЛИ-НЕ» (2-Input NOR Gate) |

|

| «3ИЛИ-НЕ» (3-Input NOR Gate) |

|

| «НЕ» (NOT Gate) |

|

| «исключающее ИЛИ» (2-Input XOR Gate) |

|

| «исключающее ИЛИ-НЕ» (2-Input XNOR Gate) |

|

| 6-входовый сумматор по модулю 2 (6-Input XOR Gate) |

Лабораторная работа № 3.

Исследование триггеров RS-, RST-, D- и JK-типов.

Литература:

1. А.А. Коваленко, М.Д. Петропавловский. Основы микроэлектроники: Учебное пособие. ‑ Барнаул: Изд‑во БГПУ, 2005. – 222 с.

2. В.С. Ямпольский. Основы автоматики и электронно-вычислительной техники. – М.: Просвещение. – 1991. – 223 с.

3. Лекции

4. Руководство к выполнению виртуальных лабораторных работ с помощью программы моделирования электрических схем Electronic Workbench 5.12

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию

- Исследуйте работу асинхронного RS-триггера с инверсными входами на логических элементах 2И-НЕ.

Пользуясь программой Electronics Workbench, соберите схему триггера, приведенную на рисунке.

|

|

|

Для управления триггером используйте переключатели (Switch), подсоединяющие входы к клемме плюса питания (Vcc) либо к клемме земли (Ground), а для индикации состояния входов и выходов – пробники (соответственно Green Probe и Red Probe).

Исследование провести в следующем порядке:

- установите на входах состояние

=0

=0  =1, что соответствует 1-ой комбинации в таблице состояний

=1, что соответствует 1-ой комбинации в таблице состояний - включите моделирование

- изменяя состояния входов в строгом соответствии с таблицей, с помощью мышки выберите в каждой строке вид операции, выполняемой триггером

Таблица состояний триггера

| № комбинации |

|

| Операция |

Установка выхода

| |||

В сокращенном варианте таблицу состояний RS-триггера с инверсными входами принято изображать в следующем виде (при данной комбинации входных сигналов выход Q устанавливается в указанное состояние независимо от его предыдущего состояния):

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Примечание: (в этой и других подобных таблицах приняты следующие обозначения):

| X | - безразличное (любое) состояние входа |

| N | - состояние выходов для недопустимой комбинации входных сигналов |

| Q(t) | - режим хранения информации (состояние в предыдущем такте) |

(t) (t)

| - изменение состояния выхода триггера на противоположное. |

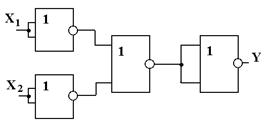

- Исследуйте работу асинхронного RS-триггера с прямыми входами на логических элементах 2И-НЕ.

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

- Исследуйте работу синхронизируемого RS-триггера (RST-триггера).

|

Для этого откройте схему RST-триггера (файл E:\MeLabs\Lab3\rst_trig_analis.EWB), ко входам которого подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются логическим анализатором (Logic Analyzer). Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Разверните панель логического анализатора. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

|

|

|

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| R | ||||||||||

| S | ||||||||||

| Q |

- Исследуйте работу статического и динамического D‑триггеров. Откройте схему параллельно включенных статического и динамического D‑триггеров (файл E:\MeLabs\Lab3\D_trig.EWB), ко входам которых подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются пробниками.

|

Разверните панель генератора слова. Из таблицы состояний выпишите по тактам двоичные коды слов и, преобразовав их в 16-ные, введите в память генератора слов. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Заполните потактовую таблицу состояний триггеров.

Таблица состояний триггеров

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| D | ||||||||||

| Q стат. | ||||||||||

| Q дин. |

- Откройте схему JK-триггера с динамическим управлением (jk_триг_анализ).

|

Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

|

|

|

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||||

| C | ||||||||||||

| J | ||||||||||||

| K | ||||||||||||

| Pre | ||||||||||||

| Clr | ||||||||||||

| Q |

Замечание: В отличие от ранее исследовавшихся схем в этом задании исследуется работа конкретной микросхемы 7476 (Dual JK MS‑SLV FF (pre, clr)), в связи с чем при моделировании необходимо к соответствующим выводам подключить источник питания Vcc и заземление GND. В задании задействованы выводы только одного из JK-триггеров (первого). Входы Pre (предустановка) и Clr (очистка) играют роль установочных входов S и R соответственно.

- Выберите из библиотеки Digital интегральную схему JK-триггера 7472 (And‑gated JK MS‑SLV FF (pre, clr)) и соберите на ней схему счетного триггера. Обратите внимание, что на информационных входах используется логика 3И. Вывод NC микросхемы – свободный (не используется).

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.

|

|

|

|

|

Дата добавления: 2014-12-08; Просмотров: 3578; Нарушение авторских прав?; Мы поможем в написании вашей работы!