КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Аналоговые цифровые преобразователи, цифро –аналоговые преобразователи в устройствах автоматизации

ЛЕКЦИЯ 7

Сигналы процесса термообработки представляют собой аналоговые сигналы амплитуда которых зависит от температуры процесса обработки (лазерной, плазменной и т.д.). Для того чтобы эту информацию использовать необходимо преоборазовать ее в цифровую форму. Преобразование сигналов из аналоговой формы в цифровую выполняется в устройстве, называемом аналого-цифровым преобразователем (АЦП). В преобразователе сигналов из аналоговой формы в цифровую можно выделить следующие процессы: дискретизацию, квантование, кодирование. Рассмотрим сущность этих процессов. При этом для определенности в последующем изложении будем считать, что преобразова-ние в цифровую форму осуществляется над сигналом, представленным в форме меняющегося во времени напряжения.

Дискретизация непрерывных сигналов. Процесс дискретизации заключается в том, что из непрерывного во времени сигнала выбираются отдельные его значения, соответствующие моментам времени, следующим через определенный временной интервал Т Интервал Г называется тактовым интервалом времени, а моменты в которые берутся отсчеты, — тактовыми моментами времени.

Дискретные значения сигнала следует отсчитывать с таким малым тактовым интервалом Г, чтобы по ним можно было бы восстановить сигнал в аналоговой форме с требуемой точностью.

Квантование и кодирование. Сущность этих операций заключается в следующем. Создается сетка так называемых уровней квантования, сдвинутых друг относительно друга на величину Д, называемую шагом квантования. Каждому уровню квантования можно приписать порядковый номер (0, 1, 2, 3, 4 и т.д.). Далее полученные в результате дискретизации значения исходного аналогового напряжения заменяются ближайшими к ним уровнями квантования. Так, на диаграмме рис. 3.59 значение напряжения в момент Г0 заменяется ближайшим к нему уровнем квантования с номером 3, в тактовый момент ft значение напряжения ближе к уровню 6 и заменяется этим уровнем и т.д.

Описанный процесс носит название операции квантования, смысл которой состоит в округлении значений аналогового напряжения, выбранных в тактовые моменты времени. Как и всякое округление, процесс квантования приводит к погрешности (к ошибкам квантования) в представлении дискретных значений напряжения, создавая так называемый шум квантования. При проектировании АЦП стремятся снизить шум квантования до такого уровня, при котором он еще обеспечивает требуемую точность. Подробнее шум квантования будет рассмотрен далее.

Следующая операция, выполняемая при аналого-цифровом преобразовании сигналов, — кодирование. Смысл ее состоит в следующем. Округление значения напряжения, осуществляемое при операции квантования, позволяет эти значения представлять числами — номерами соответствующих уровней квантования.

Получаемая таким образом последовательность чисел представляется двоичным кодом.

Так как в процессе квантования значение напряжения в каждый тактовый момент округляется до ближайшего уровня квантования, ошибка в представлении значений напряжения оказывается в пределах Следовательно, чем больше шаг квантования Л, тем больше ошибки квантования Считая, что в указанных пределах любые значения равновероятны, можно получить выражение среднеквадратичного значения ошибки квантования Уменьшение шума квантования достигается только уменьшением шага квантования. Так как Л — промежуток между соседними уровнями квантования, то с уменьшением А, очевидно, должно возрасти число уровней Квантования в заданном диапазоне значений напряжения. Пусть А = Umax - Umin — ширина диапазона изменений напряжения. Тогда требуемое число уровней квантования. Отсюда видно, что уменьшение шума квантования путем уменьшения А приводит к увеличению числа уровней квантования N. Это увеличивает число разрядов при представлении номеров уровней квантования двоичными кодами. При организации телефонной связи номера уровней квантования обычно выражаются семи- восьмиразрядными двоичными числами, а число уровней квантования N = 27...28 = 128...256.

Наряду с рассмотренными выше погрешностями квантования при аналого-цифровом преобразовании возникают аппаратурные погрешности, связанные с неточностью работы отдельных узлов АЦП. Эти погрешности будут выявляться при рассмотрении различных схемных построений АЦП.

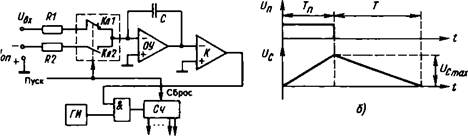

преобразователя. Очередным тактовым импульсом счетчик сбрасывается в нулевое состояние и одновременно запускается генератор линейно изменяющегося напряжения (ГЛИН). Выходное напряжение ГЛИН поступает на входы компараторов К1 и К2, на другие входы которых подаются соответственно нулевое напряжение и подлежащее преобразованию в числовую форму напряжение £/вх на входе схемы (Вх). В момент времени, когда линейно изменяющееся напряжение, нарастая от небольших отрицательных значений, проходит нулевое значение, выдает импульс первый компаратор. Этим импульсом триггер устанавливается в состояние 1. В момент, когда линейно изменяющееся напряжение достигает значения UBX, выдается импульс вторым компаратором. Этим импульсом триггер возвращается в состояние 0.

Время, в течение которого триггер находится в состоянии 1, пропорционально входному напряжению. Таким образом, входное напряжение преобразуется во временной интервал, длительность которого пропорциональна значению входного напряжения.

В течение времени Т с выхода триггера подается высокое напряжение на вход элемента И, и импульсы генератора импульсной последовательности (ГИП) проходят через элемент на вход счетчика (Сч). устанавливающееся в счетчике число пропорционально Т, а следовательно и аналоговому сигналу.

Для получения нового отсчета напряжения следует вновь подать импульс запуска. Таким образом, импульсы запуска должны следовать с частотой дискретизации входного напряжения. Покажем, как определяются параметры элементов преобразователя.

По заданной относительной погрешности преобразователя определяется максимальное число до которого счетчик должен производить счет.

Процесс преобразования значения в число занимает время, пропорциональное. Максимальное значение Ттшх называется временем преобразования:

При проектировании преобразователя время бывает задано. Этот параметр определяет так называемую динамическую погрешность преобразователя, связанную с тем, что за время преобразования входное напряжение UBX может измениться. Изменение UBX за время Гпр должно быть меньше напряжения, соответствующего единице младшего разряда счетчика.

Крутизна напряжения ГЛИН Р = UmBX / Tmax = Umax / Гпр.

Аппаратурные погрешности преобразователя связаны с неточностью работы отдельных его элементов: нелинейностью напряжения ГЛИН; отклонениями момента времени, в который компаратором выдается импульс, от момента точного равенства входных напряжений компаратора; конечным временем срабатывания триггера, элемента И; нестабильностью частоты следования импульсов генератора.

АЦП с двойным интегрированием. Схема АЦП приведена на рис. В ней, как и в схеме рассмотренного выше типа АЦП, не используется ЦАП, который для своего построения требует применения резис- торной матрицы с высокоточными значениями сопротивлений..

Рассмотрим работу преобразователя. В момент г0 (рис. подачей импульса Un в цепь Пуск осуществляется запуск схемы: сбрасывается в 0 счетчик (Сч), первый ключ (Кл1) устанавливается в замкнутое состояние, второй ключ (Кл2) — в разомкнутое.

Предварительно разряженный конденсатор С начинает заряжаться током от источника входного напряжения UBX. Так как входное напряжение операционного усилителя (ОУ) близко к нулю, практически все напряжение UBX падает на резисторе R1 и ток в цепи резистора р = UBX/R{. Этот ток замыкается через конденсатор С. Если за время длительности импульса значение напряжения UBX считать неизменным, конденсатор будет заряжаться постоянным током и напряжение на нем будет изменяться по линейному закону, достигая к моменту /2 значения

В момент окончания импульса на входе "Пуск" счетчик начинает счет импульсов, поступающих в него из генератора импульсной последовательности (ГИ) через элемент И. В этот же момент ключ Кл1 устанавливается в разомкнутое состояние, ключ Кл2 — в замкнутое. В цепи конденсатара возникает ток обратного направления. Конденсатор разряжается постоянным током, и напряжение на нем снижается по линейному закону. В момент напряжение на конденсаторе Uq и напряжение на выходе операционного усилителя проходят нулевое значение, на выходе компаратора (К) устанавливается уровень лог.О, прекращается прохождение импульсов ГИ через элемент И на вход счетчика (Сч). Образующееся к этому моменту в Сч число N есть значение UBX, представленное в цифровой форме.

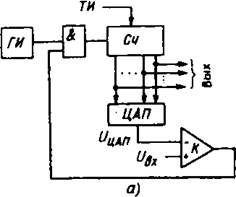

Аналого-цифровой преобразователь последовательного счета. Структурная схема преобразователя данного типа приведена на рис. Тактовым импульсом (ТИ) счетчик (Сч) сбрасывается в нулевое состояние. Нулевое напряжение UцАП = 0 возникает на выходе ЦАП, преобразующего числа в счетчике в пропорциональное напряжение. Устанавливается неравенство при котором компаратор (К) подает на вход элемента И уровень этом импульсы генератора импульсной последовательности (ГИ) проходят через элемент И на вход счетчика. Каждый поступивший на вход счетчика импульс вызывает увеличение на единицу хранившегося в нем числа, на одну элементарную ступеньку возрастает напряжение на выходе ЦАП. Таким образом, напряжение растет по ступенчатому закону, как показано на рис. В момент времени, когда достигает значения, превышающего UBX, компаратор выдает уровень лог.О, и в дальнейшем прекращается доступ импульсов генератора в счетчик. Полученное к этому моменту времени в счетчике число пропорционально напряжению UBX.

Из-за тога, что в АЦП рассматриваемого типа не используется генератор линейно изменяющегося напряжения, его аппаратурные погрешности меньше, чем могут быть в АЦП с промежуточным преобразованием напряжения во временной интервал.

В необходимые моменты времени с выхода счетчика могут сниматься числа, пропорциональные значениям UBX.

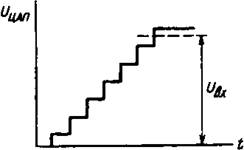

Аналого-цифровой преобразователь последовательного приближения. Структурная схема преобразователя приведена на рис.. В схеме предусмотрен построенный на RS-триггерах 1... п регистр числа. В этом регистре формируется число, пропорциональное напряжению UBX.

Вначале записывается единица только в триггер п старшего разряда этого регистра. Получающееся в регистре число с помощью ЦАП преобразуется в напряжение кот°Р°е сравнивается с напряжением UBX. Если выполняется неравенство UBX > число, в которое преобразуется UBX, действительно содержит единицу в старшем разряде. При невыполнении неравенства триггер п сбрасывается в нуль. Далее производится запись единицы в триггер п - 1 следующего разряда регистра и вновь сравнением напряжения UBX с соответствующим имеющемуся к этому моменту времени числу в регистре, выясняется, должна ли быть сохранена единица в данном разряде или триггер этого

разряда должен быть возвращен в состояние 0. Аналогичные операции выполняются во всех разрядах, после чего получающееся в регистре число может быть выдано на выход.

Рассмотрим выполнение указанных действий в преобразователе, схема которого представлена на рис.. Тактовый импульс устанавливает триггер п в состояние 1, остальные триггеры 1... п - 1 — в состояние 0. Этим же импульсом одновременно производится запись единицы в старший разряд сдвигового регистра RG, и на л-м выходе регистра появляется уровень лог.1.

Компаратор сравнивает UBX с соответствующим имеющемуся к этому моменту числу в регистре числа, и при выполнении условия UBX < выдает уровень лог.У. При поступлении импульса сдвига логический уровень с выхода компаратора через элемент И0 передается на вход элемента, и если этот уровень был уровнем лог.1, то триггер п возвращается в состояние 0. В момент окончания импульса сдвига завершается процесс сдвига на один разряд вправо содержимого регистра, появляется уровень лог.1 на (л - 1)-м выходе этого регистра, триггер п устанавливается в состояние 1. Далее с приходом очередного импульса сдвига определяется требуемое состояние триггера л - 1 и в момент окончания импульса триггер л - 2 устанавливается в состояние 1. Эти действия повторяются до тех пор, пока не будет определено состояние всех триггеров.

Для управление лазером или плазменной установкой необходимо формировать напряжение в аналоговой форме. Для этого служат цифро-аналоговые преобразователи. Рассмотрим цифроаналоговые преобразователи (ЦАП), построенные по принципу суммирования напряжений или токов, пропорциональных весовым коэффициентам двоичного кода. Схема ЦАП с суммированием напряжений. Одна из таких схем с суммированием напряжений на операционном усилителе приведена на рис.. Триггеры 1... п образуют регистр, в который помещаются двоичные числа, предназначенные для перевода в пропорциональные им значения напряжения на выходе.

Будем считать, что напряжение на выходе каждого из триггеров может принимать одно из двух возможных значений: при состоянии 1 и 0 при состоянии 0

Напряжения с выходов триггеров передаются на выход ЦАП через операционный усилитель (ОУ), работающий в режиме взвешенного суммирования напряжений (аналогового сумматора). Для каждого триггера предусматривается отдельный вход в сумматоре с коэффициентом передачи

Если в состоянии 1 находятся одновременно триггеры нескольких разрядов, то напряжение на выходе усилителя равно сумме напряжений, передаваемых на этот выход от отдельных разрядов двоичного числа в регистре:

Здесь N — десятичное значение двоичного числа, введенного в регистр. Из последнего выражения видно, что напряжение на выходе ЦАП пропорционально числу в регистре.

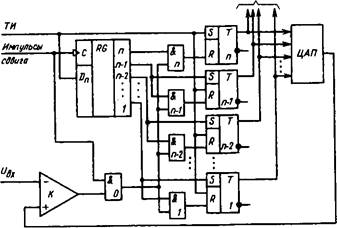

Рассмотрим работу ЦАП в случае, когда на триггерах 1... л построен двоичный счетчик. Если подать на вход этого счетчика последовательность импульсов, то с приходом каждого очередного импульса число в счетчике будет увеличиваться на единицу напряжение на выходе ЦАП будет возрастать на ступеньку, соответствующую единице младшего разряда счетчика. Таким образом, напряжение на выходе ЦАП будет иметь ступенчатую форму, как показано на рис.. После поступления 2я - 1 импульсов все разряды счетчика будут содержать 1, на выходе ЦАП образуется максимальное напряжение

Далее очередным импульсом счетчик будет сброшен в нулевое состояние, нулевым будет и выходное напряжение ЦАП. После этого счетчик начинает счет импульсов сначала, и на выходе ЦАП вновь формируется напряжение ступенчатой формы.

Аппаратурные погрешности преобразования в данной схеме связаны с отклонениями сопротивления резисторов от их номинальных значений, неидеальностью ключей (сопротивление реального ключа в закрытом состоянии не равно бесконечности, а в открытом — не равно нулю), нестабильностью источника напряжения Е. Наибольшее влияние на погрешность ЦАП оказывают эти отклонения в старших разрядах

Схема ЦАП с суммированием токов. На рис. показан еще один вариант схемы ЦАП — схема с суммированием токов в резисторной матрице. Вместо источника стабильного напряжения Е в данной схеме используются источники стабильного тока. Если триггер находится в состоянии 1, ток I источника через открытый ключ втекает в резисторную матрицу, если триггер в состоянии 0, то открывается другой ключ, который замыкает источник.

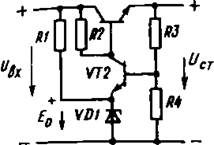

Рассмотрим схемные решения элементов, используемых в ЦАП. Источник стабильного напряжения. На риспредставлена схема простого стабилизатора напряжения. В цепь между входом и выходом стабилизатора последовательно включен транзистор VT1. Стабилизация выходного напряжения Vст обеспечивается тем, что при возраста-

нии входного напряжения UBX увеличивается напряжение на транзисторе VT1 и, наоборот, при снижении UBX напряжение на транзисторе уменьшается. Таким образом, все изменения входного напряжения гасятся на транзисторе VT1. Такой режим транзистора VT1 обеспечивается усилителем, построенным на транзисторе VT2. Пусть, например, UBX растет и вследствие этого имеется тенденция к увеличению и С/Ст. Малое увеличение Uст, далее усиливаясь, уменьшает напряжение на коллекторе VT2 и базе VT1, увеличивается падение напряжения между коллектором и эмиттером транзистора VT1.

Цепочка из резистора R1 и стабитрона VD1 обеспечивает в цепи эмиттера VT2 постоянное напряжение £0, которое стремится запереть транзистор. Для компенсации этого отрицательного смещения используется положительное напряжение, снимаемое с резистора R4 делителя напряжения, составленного из резисторов R3 и R4. Чем больше £0, тем ббльшая часть напряжения (/ст должна передаваться с R4 на базу VT2 и вместе с этим и ббльшая часть изменений напряжения Uст будет прикладываться к базе VT2 и, усиливаясь, передаваться на базу VT1.

Источник стабильного тока. Стабилизатор тока, схема которого приведена на рис., работает аналогично стабилизатору напряжения. Отличие состоит в том, что входное напряжение усилителя на транзисторе VT2 снимается с резистора R4, который в схеме стабилизатора тока включен последовательно с нагрузкой (ток нагрузки I проходит через RH, VT1, R3, R4). Если, например, UBX возрастает или сопротивление RH уменьшается и, таким образом, ток имеет тенденцию к росту, возрастает напряжение на R4 и на базе транзистора VT2. Это приводит к снижению потенциала коллектора VT2 и базы VT1, растет напряжение между коллектором и базой транзистора VT1, что препятствует росту тока /.

Ключевые устройства. Ключи преобразователя с суммированием напряжений на резисторной матрице могут быть выполнены по схеме, представленной на рис. 3.69,д. Транзисторы VT1 и VT2 управляются напряжениями с выходов триггера. Выход схемы подключается к резисторной матрице.

VT1

Рис.

Пусть триггер находится в состоянии 1. На его инверсном выходе низкий потенциал и транзистор VT2, на базу которого поступает этотпотенциал, закрыт. На прямом выходе триггера напряжение высокого уровня. Оно поступает на вход транзистора VT1 и удерживает его в открытом состоянии. Через открытый транзистор VT1 в резисторную матрицу подается напряжение, близкое к Е. Если триггер находится в состоянии О, закрыт транзистор VT1, а через открытый транзистор VT2 в резисторную матрицу поступает на пряжение низкого уровня. Таким образом, реализованное по данной схеме устройство выполняет роль двух ключей в разряде преобразователя.

В преобразователе с суммированием токов не обязательно стремиться к малому сопротивлению открытого ключа. В этом преобразователе, может быть использован диодный переключатель, схема которого представлена на рис.. Если триггер находится в состоянии 0, высокое напряжение, поступающее с инверсного выхода триггера, удерживает диод VD2 в открытом достоянии. Ток источника замыкается через диод VD2 и триггер. Если триггер находится в состоянии 1, диод VD2 закрыт и ток / замыкается через диод VD1 и резисторную матрицу.

Для хранение небольших массивов кодовых слов могут использоваться регистры. Но уже при необходимости хранить десятки слов применение регистров приводит к неоправданно большим аппаратурным затратам. Для хранения больших массивов слов строят запоминающие устройства (ЗУ) с использованием специальных микросхем, в каждой из которых может храниться информация объемом в тысячи битов.

По выполняемым функциям различают следующие типы запоминающих устройств: оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ), перепрограммируемое постоянное запоминающее устройство (ППЗУ).

Оперативное ЗУ используется в условиях, когда необходимо выбирать и обновлять хранимую информацию в высоком темпе работы процессора цифрового устройства. Вследствие этого в ОЗУ предусматриваются три режима работы: режим хранения при отсутствии обращения к ЗУ, режим чтения хранимых слов и режим записи новых слов. При этом в режимах чтения и записи ОЗУ должно функционировать с высоким быстродействием (обычно время чтения или записи слова в ОЗУ составляет доли микросекунды). В цифровых устройствах ОЗУ используются для хранения данных (исходных данных, промежуточных и конечных результатов обработки данных) и программ.

Постоянное ЗУ предназначено для хранения некоторой однажды записанной в него информации, не нарушаемой и при отключении источников питания. В ПЗУ предусматриваются два режима работы: режим хранения и режим чтения с высоким быстродействием. Режим записи не предусматривается. Используются ПЗУ для хранения программ в таких специализированных цифровых устройствах, которые, функционируя длительное время, многократно выполняют действия по одному и тому же алгоритму при различных исходных данных.

Перепрограммируемое ПЗУ в процессе функционирования цифрового устройства используется как ПЗУ. Оно отличается от ПЗУ тем, что допускает обновление однажды занесенной информации, т.е. в нем предусматривается режим записи. Однако в отличие от ОЗУ запись информации требует отключения ППЗУ от цифрового устройства, производится с использованием специальных предназначенных для записи устройств (программаторов) и занимает длительное время, достигаю, щее десятков минут. Перепрограммируемые ПЗУ дороже ПЗУ, и их применяют в процессе отладки программы, после чего их можно заменить более дешевым ПЗУ.

Запоминающее устройство содержит некоторое число N ячеек, в каждой из которых может храниться слово с определенным числом разрядов п. Ячейки последовательно нумеруются двоичными числами. Номер ячейки называется адресом. Если для представления адресов используются комбинации /п-разрядного двоичного кода, то число ячеек в ЗУ может составить N= 2т.

Количество информации, которое может храниться в ЗУ, определяет его емкость. Емкость можно выражать числом ячеек N с указанием разрядности п хранимых в них слов в форме N х л, либо ее можно определять произведением Nun: М= N -п бит. Часто разрядность ячеек выбирают кратной байту (1 байт равен 8 битам). Тогда и емкость удобно представить в байтах. Большие значения емкости часто выражаются в единицах К = 210 = 1024. Например, М = 64 Кбайт означает емкость, равную М = 64 • 1024 • 8 бит.

Быстродействие ЗУ характеризуется двумя параметрами: временем выборки гв, представляющим собой интервал времени между моментом подачи сигнала выборки и появлением считанных данных на выходе, и циклом записи определяемым минимально допустимым временем между моментом подачи сигнала выборки при записи и моментом, когда допустимо последующее обращение к памяти.

Запоминающие устройства строятся из набора однотипных микросхем ЗУ с определенным их соединением. Каждая микросхема ЗУ кроме времени обращения и емкости характеризуется потребляемой мощностью, набором питающих напряжений, типом корпуса (числом выводов). Микросхемы ППЗУ дополнительно характеризуются временем хранения записанной в них информации (по истечении которого хранящаяся в ячейках информация может самопроизвольно измениться), допустимым количеством циклов перезаписи (после чего микросхема считается негодной для использования).

Оперативное запоминающее устройство

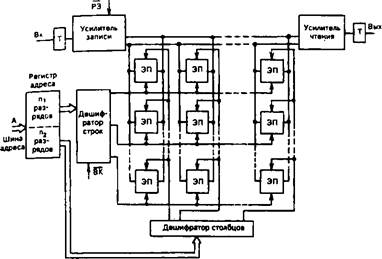

На рис. приведена типичная структура микросхемы ОЗУ. Информация хранится в накопителе. Он представляет собой матрицу, составленную из элементов памяти (ЭП), расположенных вдоль строк и столбцов. Элемент памяти может хранить 1 бит информации (лог.О либо лог.1). Кроме того, он снабжен управляющими цепями для установки элемента в любом из трех режимов: режиме хранения, в котором он отключается от входа и выхода микросхемы, режиме чтения, в котором содержащаяся в ЭП информация выдается на выход микросхемы, режи-

ме записи, в котором в ЭП записывается новая поступающая со входа микросхемы информация.

Каждому ЭП приписан номер, называемый адресом элемента. Для поиска требуемого ЭП указывается строка и столбец, соответствующие положению ЭП в накопителе. Адрес ЭП в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Число строк и число столбцов накопителя выбираются равными целой степени двух.

Разряды регистра адреса делятся на две группы: одна группа из Л] разрядов определяет двоичный номер строки, в которой в накопителе расположен ЭП, другая группа из л2 разрядов — двоичный номер столбца, в котором расположен выбираемый ЭП. Каждая группа разрядов адреса подается на соответствующий де шифратор: дешифратор строк и дешиф ратор столбцов. При этом каждый из дешифраторов создает на одной из своих выходных цепей уровень лог. 1 (на остальных выходах дешифратора устанавливается уровень лог.О), выбранный оказывается под воздействием уровня лог. 1 одновременно по цепям строки и столбца. При чтении содержимое ЭП выдается на усилитель чтения и с него — на выходной триггер (Т) и выход микросхемы. Режим записи устанавливается подачей сигнала на вход разрешения записи (РЗ). При уровне лог.О на входе РЗ открывается усилитель записи и бит информации со входа данных поступает в выбранный ЭП и запоминается в нем.

Указанные процессы происходят в том случае, если на входе выбора кристалла (ВК) действует активный уровень лог.О. При уровне лог.1 на этом входе на всех выходах дешифратора устанавливается уровень лог.О и ЗУ оказывается в режиме хранения.

На рис. показано условное графическое обозначение микросхемы ОЗУ.

Рассмотрим последовательность подачи сигналов в режимах чтения и записи. На рис. а представлена временная диаграмма сигналов в режиме чтения. С определенной задержкой | относительно момента подачи адреса и сигнала в цепь ВК (связанной с процессами дешифрации адреса и включения выходных цепей выбранного ЭП) на выход микросхемы передается содержимое выбранного ЭП. В режиме записи (рис.) должны быть соблюдены условия, которые исключали бы нарушение содержимого ячеек, в которые не производится обращение. Это обеспечивается тем, что сигнал в цепь РЗ подается с задержкой относительно момента подачи сигналов в цепь адреса, ВК и входных данных и снимается сигнал в цепи РЗ прежде, чем будет снят сигнал в цепи ВК. В противном случае, при преждевременной подаче сигнала РЗ, может произойти запись в ячейку с адресом, не совпадающим с адресом на входах микросхемы.

Микросхемы ОЗУ допускают наращивание емкости памяти наращиванием разрядности (и, следовательно, разрядности хранимых слов) и наращиванием числа ячеек (и, значит, числа слов, которые можно хранить в памяти). Таким образом, используя соответствующее число микросхем в определенном их соединении, можно строить память с требуемой организацией.

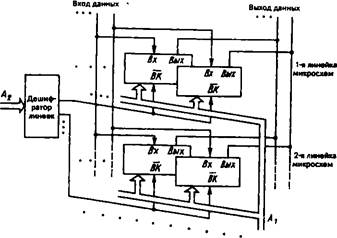

Рассмотрим схему наращивания разрядности ячеек (рис.). На все микросхемы подается один и тот же адрес. При чтении каждой микросхемой выдается определенный разряд считываемого слова. При записи входное слово поразрядно заносится в ЭП отдельных микросхем. Таким образом, если микросхемы имеют организацию Nx 1 (;V одноразрядных ячеек), то для блока памяти с организацией N*n(N ячеек с разрядностью каждой п) потребуется п микросхем.

На рис. показана схема наращивания числа ячеек и их разрядности. Блок памяти состоит из микросхем, образующих отдельные линейки (ряды), каждая из которых строится по схеме наращивания разрядности. Разряды адреса блока памяти в этом случае делятся на две группы Лх и Л2. Группа разрядов Л2 определяет номер линейки, группа разрядов А — номер ячейки в выбранной линейке.

Выбор линейки осуществляется с помощью дешифратора, на вход которого подается Л2, а каждый из выходов подключен к входу ВК определенной линейки. Таким образом, в зависимости от кодовой комбинации, содержащейся в Л2, на соответствующем выходе дешифратора появляется уровень лог.О, который обеспечивает выбор определенной линейки микросхем. На входы ВК остальных линеек с выходов дешифратора поступает уровень лог.1, и микросхемы этих линеек устанавливаются в режим хранения, в котором они не реагируют на адресную группу Л j.

Рассмотрим пример наращивания емкости блока памяти. Пусть на микросхемах с организацией 1024 х 1 необходимо построить блок памяти, имеющий организацию 4096 х 8, т.е. блок памяти на 4096 8-разрядных ячеек. Наращивание разрядности потребует в каждой линейке схемы на рис. 3.80 использовать восемь микросхем; для увеличения числа ячеек с 1024 до 4096 (в четыре раза) необходимо предусмотреть четыре линейки микросхем. Таким образом, общее число требуемых микросхем 8 • 4 = 32. Адрес, по которому в таком блоке памяти будет производиться обращение, формируется следующим образом. Для выбора линейки в адресе потребуется двухразрядная группа Л2, каждой из четырех кодовых номбинаций этой группы (00, 01, 10, 11) будет соответствовать определенная линейка в блоке памяти. Выбор ячейки в линейке микросхем потребует наличия в адресе 10-разрядной группы Лх (число комбинаций 10-разрядной группы210 = 1024 равно числу ЭП в микросхеме). Таким образом, адрес рассматриваемого блока памяти должен иметь 12 разрядов.

В каждом столбце матрицы микросхем на рис. выходы всех микросхем объединяются в цепь соответствующего разряда выхода данных блока, все входы данных — в цепь соответствующего разряда входа данных блока памяти.

Постоянные запоминающие устройства

Как и ОЗУ, ПЗУ состоит из ячеек, обратившись к которым можно вывести их содержимое. Отличие от ОЗУ заключается в том, что информация в ячейки записывается однократно, после чего в процессе эксплуатации используется лишь режим чтения.

По способу занесения информации ПЗУ делятся на два вида: ПЗУ, программируемые маской на предприятии-изготовителе, и ПЗУ, программируемые пользователем.

В первые информация заносится в процессе изготовления микросхем с помощью соответствующего фотошаблона. Очевидно, такой способ записи пригоден в тех случаях, когда производится выпуск крупной партии ПЗУ с одной и той же записанной в них информацией. Промышленность выпускает такие ПЗУ, например, для использования в качестве преобразователя двоичного кода в определенные двоично-десятичные коды и других преобразователей. В них входная кодовая комбинация служит адресом ячейки, а содержимое ячейки — выходной кодовой комбинацией (являющейся, например, кодовой комбинацией двоично- десятичного кода).

В ПЗУ, программируемых пользователем, запись информации производится непосредственно пользователем с помощью специальных устройств, называемых программаторами. Программатор выдает в микросхему соответствующие напряжения для записи информации, набираемой на клавиатуре либо предварительно нанесенной путем пробивок на перфоленту. Этими напряжениями осуществляется прожигание плавких перемычек в элементах памяти. Очевидно, однажды записанная в ПЗУ информация в дальнейшем не может быть изменена. При необходимости изменить содержимое ПЗУ микросхемы с ранее записанной информацией заменяются новыми, в которые записываются новые данные.

На рис приведена структура ПЗУ, программируемого пользователем. Как и в ОЗУ, матрица-накопитель состоит из элементов памяти, образующих строки и столбцы, но в отличие от ОЗУ при считывании из накопителя выдается содержимое целой строки элементов памяти. Такая строка обычно содержит несколько слов. С помощью селектора из строки выделяется и передается на выход требуемое слово.

Пусть, например, ПЗУ имеет емкость М = 210 бит, разбивающихся на N = "2я слов по 22 = 4 разрядов в каждом слове. Накопитель будет содержать 210 элементов памяти, расположенных вдоль 2s = 32 строк и 25 = 32 столбцов. При обращении должен указываться адрес слова, этот адрес в рассматриваемом примере будет содержать восемь разрядов, разбивающихся на две группы разрядов А 2 и А1: пятиразрядную группу Ах и трехразрядную группу Аг Группа At подается на дешифратор 1, который выбирает одну из 25 = 32 строк накопителя. Содержимое строки состоит из 32 бит или восьми 4-разрядных слов. Номер слова в строке задается группой Аг Дешифратор 2 преобразует эту адресную группу в сигнал на одном из восьми своих выходов. По этому сигналу в селекторе из содержимого строки выделяется требуемое слово, которое передается через буфер ввода-вывода на выход микросхемы.

Перепрограммируемые постоянные запоминающие устройства

Перепрограммируемые ПЗУ обладают всеми достоинствами ПЗУ, храня записанную в них информацию неопределенно долго и при отключении питания. В то же время они допускают стирание записанной информации и запись новой информации. Однако если чтение осуществляется за доли микросекунды, то время записи на много порядков больше. Рассмотрим принцип работы приведенного на рис. элемента памяти с электрической записью информации и стиранием ультрафиолетовым светом.

Транзистор VT1 служит для выборки элемента памяти. Хранение информации осуществляется в транзисторе VT2. Особенность транзистора VT2, структура которого показана на рис., состоит в том, что он имеет изолированный затвор.

При подаче достаточно большого напряжения кр—л-переходу истока либо стока происходит инжекция электронов в затвор, после чего этот заряд может удерживаться на затворе длительное время. Отрицательный заряд на затворе, притягивая дырки, создает в области проводящей р-канал между истоком и стоком.

Транзистор оказывается в состоянии 0. Если же к переходу не прикладывалось повышенного напряжения, заряд на затворе отсутствует, транзистор оказывается в непроводящем состоянии (состояние 1).

Стирание информации в одних микросхемах производится путем подачи соответствующих напряжений, в других — путем подачи ультрафиолетового излучения через прозрачную кварцевую крышку в корпусе микросхемы.

Под действием напряжений либо светового излучения, действующего в течение примерно 10 мин, снимается заряд с затворов транзисторов, и все транзисторы накопителя оказываются установленными в непроводящее состояние. Обычное комнатное освещение практически не оказывает влияния на состояние транзисторов.

Перепрограммируемые ПЗУ дороже ПЗУ, и их применяют в процессе отладки цифровых устройств, когда необходимо уточнить информацию, которая должна храниться в памяти. После отладки ППЗУ можно заменить более дешевыми ПЗУ.

|

|

Дата добавления: 2014-12-10; Просмотров: 2178; Нарушение авторских прав?; Мы поможем в написании вашей работы!