КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Логический элемент И-НЕ транзисторно-транзисторной логики

|

|

|

|

Транзисторный логический элемент НЕ.

Логический элемент НЕ реализуется с помощью биполярного транзистора n-p-n cтруктуры. Принципиальная электрическая схема транзисторного логического элемента НЕ и его таблица истинности приведены на рис.10.7.

Схема работает следующим образом. Если на вход x логического элемента подать сигнал лог. 0, то транзистор VT будет закрыт и на выходе y появится сигнал лог. 1, так как всё напряжение будет падать на закрытом транзисторе. При подаче на вход x логического элемента сигнала лог. 1, транзистор VT открывается и на выходе y появится сигнал лог. 0, при этом всё напряжение падает на резисторе Rк.

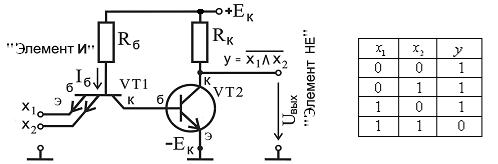

При использовании логических элементов транзисторно-транзисторной логики, построенной с помощью биполярных транзисторов n-p-n cтруктуры, реализуется операция И-НЕ. На рис.10.8 приведена электрическая схема логического элемента И-НЕ и таблица истинности. Схема состоит из двух логических элементов И и НЕ, соединённых последовательно. Транзисторный элемент И имеет несколько входов. На схеме рассматриваются только два из эмиттерных входов х1 и х2 транзистора VT1, коллектор которого соединён с базой инвертора, построенного на транзисторе VT2.

Рис.10.7. Принципиальная электрическая схема транзисторного логического элемента НЕ и его таблица истинности

Рис.10.8. Электрическая схема логического элемента И-НЕ и его таблица истинности

Схема работает следующим образом. Если на входы х1 и х2 транзистора VT1 поступают сигналы лог. 0 или на одном из этих входов присутствует сигнал лог. 1, то базовый ток  пройдет через сопротивление базы транзистора к эмиттерным входам (входу) от “+” источника питания к его “–“. При этом, транзистор VT2 будет закрыт и на его выходе y присутствует cигнал лог. 1. Если на входы х1 и х2 транзистора VT1 поступают положительные сигналы лог. 1, то в этом случае закрываются эмиттерные входы тразистора VT1 и базовый ток

пройдет через сопротивление базы транзистора к эмиттерным входам (входу) от “+” источника питания к его “–“. При этом, транзистор VT2 будет закрыт и на его выходе y присутствует cигнал лог. 1. Если на входы х1 и х2 транзистора VT1 поступают положительные сигналы лог. 1, то в этом случае закрываются эмиттерные входы тразистора VT1 и базовый ток  течет через коллектор тразистора VT1 к базе тразистора VT2, открывая его. При этом на выходе у тразистора VT2 появится синал лог. 0.

течет через коллектор тразистора VT1 к базе тразистора VT2, открывая его. При этом на выходе у тразистора VT2 появится синал лог. 0.

|

|

|

10.5. Логический элемент ИЛИ-НЕ эмиттерно-связанной логики

10.5. Логический элемент ИЛИ-НЕ эмиттерно-связанной логики

На рис.10.9 изображена электрическая схема логического элемента ИЛИ-НЕ, построенного на транзисторах n-p-n cтруктуры, и его таблица истинности. Если на

входах х1 и х2 транзисторов VT1, VT2 присутствуют входные сигналы лог. 0, то эти транзисторы будут закрыты и сопротивление между их коллекторами и эмиттерами будет бесконечным. При этом коллекторная цепь этих транзисторов будет иметь положительный потенциал, то есть инвертированный сигнал ИЛИ, который будет поступать на вход транзистора VT3. На выходе у транзистора VT3, работающего в режиме повторителя, появится сигнал лог. 1.

В случае поступления на входы х1 и х2 транзисторов VT1, VT2 положительных сигналов лог. 1 или на одном из этих входов присутствует сигнал лог. 1, то их коллекторные цепи будут иметь отрицательный потенциал. При этом транзисторы VT1, VT2 (или один из них) открываются, и сопротивление цепи коллектор-эмиттер будет равно нулю. Так как Rк>Rэ1, то на общем коллекторном выходе транзисторов VT1, VT2 появится отрицательный потенциал, который поступит на вход транзистора VT3 и закроет его. Сигнал на выходе y транзистора VT3 будет иметь лог. 0. Фактически транзистор VT3 является повторителем действия выходного сигнала транзисторов VT1 и VT2, работающих в режиме операции ИЛИ-НЕ.

Рис.10.9. Электрическая схема логического элемента ИЛИ-НЕ и его таблица истинности

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 1737; Нарушение авторских прав?; Мы поможем в написании вашей работы!