КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Исследование логических схем

|

|

|

|

ЛАБОРАТОРНАЯ РАБОТА № 5

Цель работы: ознакомление с работой и характеристиками логического элемента И-HЕ и JК-триггера, а также применением их в схемах дешифраторов, счетчиков и распределителей; исследование RS-, JK- и Т-триггеров, комбинационных логических схем, счетчиков и распределителей.

Описание лабораторной установки

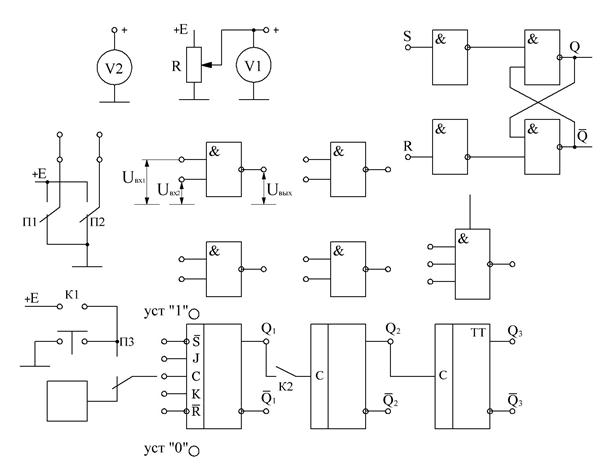

Схема макета лабораторной установки приведена на рис. 5.1. В работе исследуются интегральные микросхемы (ИМС) ТТЛ-типа серии K133.

Рис. 5.1. Лицевая панель лабораторной установки для исследования

логических схем

В макете установки используются пять элементов И-НЕ: четыре двухвходовых (2И-НЕ типа К133ЛА3) и один с тремя входами (3И-НЕ типа К133ЛА4), а также три JК-триггера (типа K133TВ1), Входы и выходы ИС выведены на лицевую панель в виде контактных гнезд. Необходимые соединения осуществляются гибкими проводниками.

Для контроля выходных сигналов микросхем установлены лампочки, свечение которых означает наличие на выходе логической единице, а отсутствие свечения означает логический ноль. С помощью потенциометра R регулируется постоянное напряжение, подаваемое на один из входов элемента 2И-НЕ, при снятии передаточной характеристики. Вольтметры V1 и V2 служат для измерения входного и выходного напряжений. Управляющие сигналы (0 или 1) на входы микросхем подаются с гнезд X и Y.Значению логического 0 соответствует нижнее положение переключателей П1 или П2, а значению логической 1 (+Е) - верхнее положение П1, П2. С помощью переключателя П3 на синхронизирующий вход JK-триггера подаются либо одиночные тактовые импульсы (П3 в верхнем положении), формируемые при нажатии и отпускании кнопки К1, либо тактовые импульсы от генератора ГИ (П3 в нижнем положении).

|

|

|

Для установки JK-триггеров в исходное состояние (0 или 1) служат кнопки «Уст. 0» и «Уст. 1». Включение установки осуществляется тумблером «Сеть».

Указания и пояснения к работе

Логические ИМС являются элементами, на основе которых выполняются схемы цифровой техники. В работе исследуются ИМС ТТЛ-типа серии К133: логические элементы И-НЕ, JK-триггеры и логические устройства на их основе.

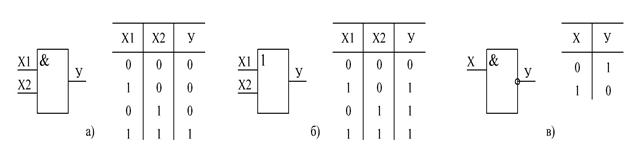

Логические элементы предназначены для выполнения логических операций над дискретными сигналами при двоичном способе их представления. Основные логические операции:.

«И» - логическое умножение (конъюнкция);

«ИЛИ» - логическое сложение (дизъюнкция);

«НЕ» - логическое отрицание (инверсия);

Для выполнения этих операций служат соответствующие логические элементы И, ИЛИ, НЕ (рис. 5.2.).

Рис. 5.2. Условные графические обозначения и таблицы истинности

элементов «И» (а), «ИЛИ» (б), «НЕ» (в)

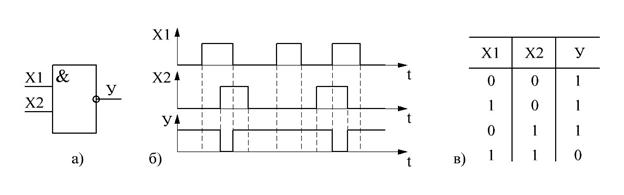

Широкое применение получили логические элементы И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, выполняющие несколько логических операций. На рис. 5.3 приведены условное графическое обозначение, временные диаграммы и таблица истинности элемента И-НЕ.

Рис.5.3. Условное графическое обозначение (а), временные диаграммы (б) и таблицы истинности (в) элемента И-НЕ

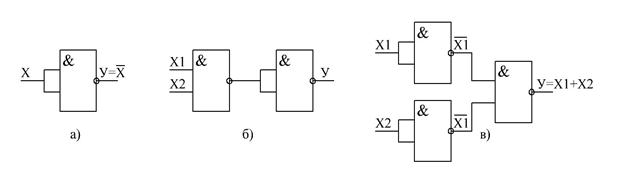

Логический элемент И-НЕ (как и элемент ИЛИ-НЕ) представляет собой функционально полную логическую систему. Из этого следует, что используя необходимое количество этих элементов можно реализовать любую логическую схему. На рис. 5.4 в качестве примера приведена схемная реализация логических операций НЕ, И, ИЛИ на элементах И-НЕ.

Рис. 5.4. Реализация логических операций НЕ (а), И (б), ИЛИ (в)

на элементах И-НЕ

Логические устройства, у которых отсутствуют элементы памяти, и выходные сигналы которых определяются только комбинацией входных сигналов в данный момент времени, называются комбинационными (КЛУ). К таким устройствам относятся дешифраторы, сумматоры, преобразователи кодов и другие.

|

|

|

Порядок построения КЛУ.

1. Составляют таблицу истинности, в которой для всех комбинаций входных сигналов указывают соответствующие выходные сигналы.

2. Для каждого истинного выходного состояния формируют логические произведения соответствующих входных сигналов.

3. Суммируют логические произведения и составляют уравнение логической функции.

4. Используя законы и тождества алгебры логики (АЛ) или диаграммы Вейча, минимизируют функцию и приводят ее к виду, удобному для реализации.

5. Составляют логическую схему.

Для осуществления преобразований логических выражений используют: переместительный (x + y = y + x, x∙y = y∙x), сочетательный и распределительный (x∙(y + z) = x∙y + x∙z) законы, а также тождества:

x + 0 = x; x ∙ 0 = 0; x ∙ y + x ∙  = x; x ∙ (

= x; x ∙ ( + y);

+ y);

x + 1 = 1; x ∙ 1 = x; x + x ∙ y = x; (x + y) ∙ (x + z) = x + y ∙ z;

x + x = x; x ∙ x = x; x ∙ (x + y) = x; ( );

);

x +  = 1; x ∙

= 1; x ∙  = 0; (

= 0; ( ) =

) =  ;

;  = x;

= x;

А так же законы инверсии (законы двойственности, теоремы де Моргана)

;

;  ;

;

Таблица 5.1.

| x1 | x2 | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Пример:

На элементах И-НЕ составить схему, выполняющую операцию ИЛИ.

1. Составляем таблицу истинности элемента ИЛИ (табл. 5.1).

2. Для каждого выходного истинного состояния (y = 1) формируем логические произведения:( ); (

); ( ); (

); ( ).

).

3. Суммируем логические произведения и составляем уравнение логической функции: y =  +

+  +

+  .

.

4. Используя законы и тождества АЛ, минимизируем функцию. Группируем второе и третье слагаемые и выносим за скобки x2:

y =  + (

+ ( +

+  ) =

) =  ;

;

Вводим двойное отрицание, чтобы затем перейти от операции ИЛИ к операции И, используя теоремы де Моргана:

;

;

5. Составляем схему на элементах И-НЕ (см. рис. 5.4, в).

Триггеры - это устройства с двумя устойчивыми состояниями, предназначенные для записи и хранения логических значений. В отличие от комбинационных, они относятся к классу устройств последовательностного типа. Состояние, в которое переходит триггер, зависит не только от комбинации входных сигналов, но и от состояния, в котором находился триггер до прихода входных сигналов. Триггер имеет два выхода: прямой и инверсный, на которых отображается его состояние. Число входов зависит от структуры триггера и функции, которую он выполняет. По функциональному признаку триггеры делятся на RS-, JK-, D-, Т-триггер и др. По способу записи информации триггеры делятся на асинхронные и синхронные. В асинхронных триггерах запись информации (переход из одного состояния в другое) происходит при поступлении входных сигналов. В синхронных - при наличии входных сигналов и при поступлении синхронизирующего (тактового) импульса.

|

|

|

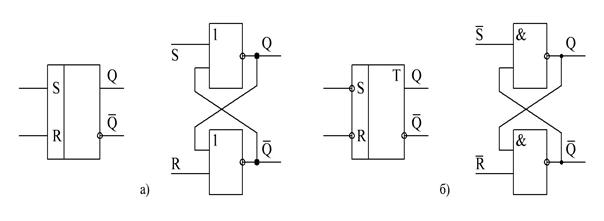

Простейшим триггером является RS-триггер. Он имеет два входа: S (от английского слова set - установка в 1) и R (от reset - сброс или установка в 0) и два выхода - прямой и инверсный. В зависимости от логической структуры может быть с прямыми (рис. 5.5, а) и инверсными (рис. 5.5, б) входами.

Рис. 5.5. RS-триггер с прямыми (а) и инверсными (б) входами

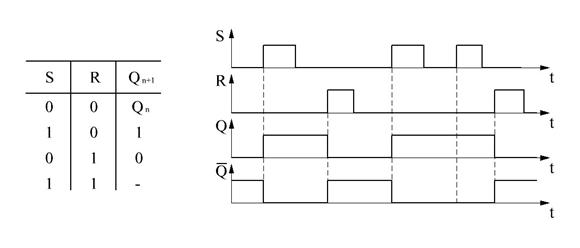

В таблице истинности (рис. 5.6.) символом Qn+1 обозначено состояние, в которое триггер переходит из предыдущего состояния Qn.

Сочетание входных сигналов S = 0, R = 0 означает хранение информации (предыдущее состояние триггера не изменяется);

Сочетание S = 0, R = 1 - установку триггера в 0;

Сочетание S = 1, R = 0 означает установку триггера в 1;

Сочетание S = 1, R = 1 - запрещенная комбинация (данное состояние на практике должно быть исключено).

Рис. 5.6. Таблица истинности и временные диаграммы

асинхронного RS-триггера

Работу RS-триггера можно описать уравнением  . Самостоятельно RS-триггер в устройствах цифровой технике не используется из-за низкой помехоустойчивости.

. Самостоятельно RS-триггер в устройствах цифровой технике не используется из-за низкой помехоустойчивости.

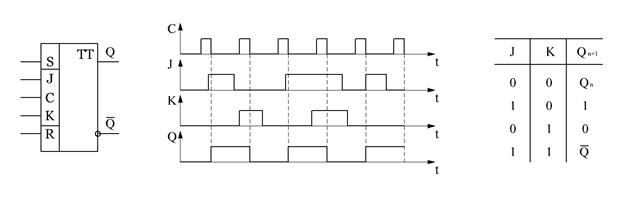

JK-триггер (рис. 5.7) является наиболее универсальным среди синхронных триггеров. Он имеет установочные входы R и S, информационные входы J и K и синхронизирующий вход C.

Рис. 5.7. Условное обозначение, временные диаграммы и таблица

истинности JK-триггера

Сочетание входных сигналов J = 0, K = 0 означает хранение информации (предыдущее состояние триггера не изменяется);

Сочетание сигналов J = 0, K = 1 означает установку триггера в 0;

Сочетание J = 1, K = 0 - установку триггера в 1;

Сочетание J = 1, K = 1 - не является запрещенной комбинацией, но в данном случае происходит инверсия предыдущего состояния триггера.

|

|

|

Из временных диаграмм видно, что JK-триггер реагирует на сигналы J и К только при наличии тактовых импульсов. Переход триггера в новое состояние происходит по заданному фронту тактовых импульсов. Работу JK - триггера можно описать уравнением  . Дополнительные входы S и R служат для предварительной установки начального состояния выходов триггера. На основе JK-триггера можно выполнить D- и T-триггеры.

. Дополнительные входы S и R служат для предварительной установки начального состояния выходов триггера. На основе JK-триггера можно выполнить D- и T-триггеры.

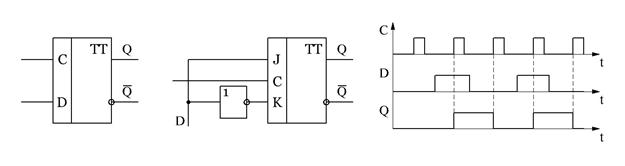

D-триггер имеет два входа - информационный D и синхронизирующий C (он же тактовый) (рис. 5.8).

Рис. 5.8. Условное обозначение D-триггера, D-триггер на основе JK-триггера и временные диаграммы D-триггера

D-триггер в момент времени n + i переходит в состояние, соответствующее значению переменной на D-входе в момент времени n. Он запоминает значение входного сигнала до следующего тактового импульса, являясь одноразрядной ячейкой памяти.

Т-триггер это триггер со счетным входом (счетный триггер), он имеет один вход Т - тактовый (рис. 5.9).

Рис. 5.9. Условное обозначение Т-триггера, Т-триггер на основе

JK-триггера и временные диаграммы D-триггера

В момент заднего фронта тактового импульса триггер переходит в состояние, противоположное предыдущему ( ). Частота сигналов на выходе Т-триггера в два раза ниже частоты входных сигналов, поэтому его можно использовать как делитель частоты и двоичный счетчик.

). Частота сигналов на выходе Т-триггера в два раза ниже частоты входных сигналов, поэтому его можно использовать как делитель частоты и двоичный счетчик.

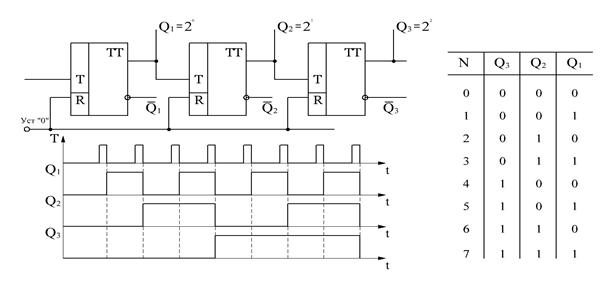

Двоичный суммирующий счетчик (рис. 5.10) производит счет импульсов, поступающих на вход, в двоичной системе счисления.  Рис. 5.10. Структурная схема, временные диаграммы и таблица истинности трехразрядного суммирующего счетчика

Рис. 5.10. Структурная схема, временные диаграммы и таблица истинности трехразрядного суммирующего счетчика

Максимальное число, которое может быть записано в счетчике,  , где 2 - коэффициент счета, n - число разрядов. Каждый разряд счетчика состоит из триггера. Наиболее просто реализовать счетчик на Т-триггерах, срабатывающих по заднему фронту входного импульса.

, где 2 - коэффициент счета, n - число разрядов. Каждый разряд счетчика состоит из триггера. Наиболее просто реализовать счетчик на Т-триггерах, срабатывающих по заднему фронту входного импульса.

Трехразрядный счетчик осуществляет счет от 0 до 7. Для увеличения числа N к выходу добавляют разряды. Первый триггер счетчика образует младший разряд двоичного числа. Сигнал с его выхода Q1 подается на вход второго разряда, а сигнал Q2 с выхода второго разряда на вход третьего разряда. Каждый последующий разрядный триггер переключается задним фронтом выходного импульса предыдущего разряда. Состояние разрядов счетчика представляет собой запись количества импульсов, поступивших на вход, в двоичном коде, например, N = 5 = 1 ∙ 22 + 0 ∙ 21 + 1 ∙ 20. После записи максимального числа N счетчик автоматически обнуляется, т. е. во всех разрядах устанавливается Q1 = Q2 = Q3 = 0. Частота повторения выходного сигнала в i -м разряде в 2 i раз меньше частоты повторения входных импульсов.

На основе счетчиков строятся распределители импульсов, широко применяемые в системах управления тиристорным преобразователям. Распределитель импульсов представляет собой комбинацию счетчика и дешифратора на несколько выходов. В свою очередь дешифратор преобразует двоичное число, содержащееся на совокупности его входов, в сигнал на одном из выходов, а номер выхода соответствует десятичному числу.

Предварительное задание

Таблица 5.2.

| X | Y | Варианты | |||

| f 1 | f 2 | f 3 | f 4 | ||

1. По таблице истинности (табл. 5.2) составить формулу логической функции (по одному из четырех вариантов), упростить ее и привести к виду, удобному для реализации на элементах И-НЕ. Составить на элементах И-НЕ структурную схему КЛУ для проверки ее на лабораторной установке.

2. По таблице истинности (табл. 5.3) составить формулу логической функции дешифратора для выделения (в соответствии с вариантом) им-

Таблица 5.3.

| N | Q1 | Q2 | Q3 | Варианты | |||

| f 1 | f 2 | f 3 | f 4 | ||||

пульсов с разными номерами, упростить ее и привести к виду, удобному для реализации на элементах И-НЕ. Составить структурную схему распределителя (трехразрядного счетчика с дешифратором) для проверки ее на лабораторной установке.

Рабочее задание

1. Исследование логического элемента 2И-НЕ.

1.1. Подать на один из входов логического элемента 2И-HЕ напряжение с гнезд X или Y, а на второй - регулируемое постоянное напряжение. К выходу элемента подключить вольтметр V2. Изменяя потенциометром R величину входного напряжения Uвх1, снять и построить передаточную характеристику элемента 2И-НЕ  по одному из входов. При этом напряжение на другом входе Uвх2 должно быть равно поочередно логическим 0 и 1.

по одному из входов. При этом напряжение на другом входе Uвх2 должно быть равно поочередно логическим 0 и 1.

1.2. Подать на вход элемента 2И-НЕ напряжение с шин X и Y. Для всех комбинаций входных сигналов X и Y (00, 01, 10, 11) записать в таблицу 5.4 входной сигнал f. Результат сравнить с таблицей истинности элемента И-НЕ.

Таблица 5.4.

| X | Y | f |

2. Исследование комбинационных схем.

2.1. Собрать схемы, приведенные на рис. 5.4, выполняющие логические операции НЕ, И, ИЛИ. Для всех комбинаций входных сигналов составить таблицы соответствия и сравнить их с таблицами истинности элементов НЕ, И, ИЛИ.

2.2. Собрать на элементах 2И-НЕ схему, реализующую одну из функций предварительного задания. Для всех комбинаций входных сигналов составить таблицу соответствия и сравнить ее с исходной.

3. Исследование триггеров.

3.1. Собрать RS-триггер на элементах 2И-НЕ (рис. 5.1, б). Входы S и R соединить с гнездами X и Y. Для всех комбинаций входных сигналов составить таблицу переходов RS-триггера (табл. 5.5). Убедиться, что при S = R = 1 работа триггера нарушается  .

.

| S | R |

|

|

Таблица 5.5.

Проверить по таблице переходов RS-триггера соответствие его работы характеристическому уравнению  .

.

3.2. Исследовать JK-триггер (рис. 5.1, а, ключ К2 разомкнут). Подавая на входы S и R сигналы с шин X и Y, убедиться, что при подаче сигнала 0 на вход S триггер устанавливается в состояние Q = 1, а при подаче сигнала 0 на вход R триггер устанавливается в состояние Q = 0.

Подать сигналы на входы J и К с гнезд X и Y. Для всех комбинаций входных сигналов составить таблицу переходов JK-триггера (табл. 5.6).

| J | K |

|

|

Таблица 5.6.

Состояние триггера Qn+1 фиксировать после подачи (кнопка К нажата) и снятия (кнопка К отпущена) синхронизирующего сигнала. Обратить внимание на то, что «опрокидывание» триггера происходит при переходе синхронизирующего импульса из 1 в 0.

Проверить по таблице переходов JK-триггера соответствие его работы характеристическому уравнению  .

.

3.3. Исследовать Т-триггер на основе JK-триггера. Для этого: входы J и К JК-триггера оставить свободными (J = K = 1); периодически нажимая кнопку К, подавать тактовые импульсы на вход С. Составить таблицу переходов Т-триггера (табл. 5.7).

Таблица 5.7.

| Т |

|

Проверить по таблице переходов соответствие работы Т-триггера характеристическому уравнению  .

.

4. Исследование счетчиков и распределителей.

4.1. Собрать последовательный двоичный трехразрядный суммирующий счетчик (ключ К2 замкнут). Кнопкой "Уст. 0" установить состояние разрядов

счетчика Q1 = 0, Q2 = 0, Q3 = 0. Таблица 5.8.

| Номер такта | Q1 | Q2 | Q 3 |

| … |

Периоди ческим нажатием кнопки К1 подавать входные импульсы и составить таблицу функционирования счетчика (табл. 5.8).

4.2. Собрать схему распределителя для выделения импульсов по одному из вариантов предварительного задания. Затем периодическим нажатием кнопки K1 создать последовательность входных импульсов и убедиться в правильности работы распределителя.

Контрольные вопросы

1. Составьте таблицы истинности, нарисуйте схемное обозначений и временные диаграммы логических элементов И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ.

2. Какое устройство называется триггером? Как подразделяются триггеры по функциональному назначению и способу управления?

3. Составьте таблицу истинности, изобразите схемы и временные диаграммы RS-, JК-, D-, Т-триггеров.

4. Поясните работу суммирующего счетчика.

5. Составьте схему КЛУ и распределителя по заданию преподавателя.

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 4724; Нарушение авторских прав?; Мы поможем в написании вашей работы!