КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Указания по организации самостоятельной работы. Изучение принципов функционирования микропроцессоров со стековой архитектурой на примере математического сопроцессора і80х87

|

|

|

|

Изучение принципов функционирования микропроцессоров со стековой архитектурой на примере математического сопроцессора і80х87.

Лабораторная работа № 5.

Push BXзагрузка в стек относительного адреса параметраb

call near ptr summa в стек загружается относительный адрес следующей за call команды (mov c,AX) и осуществляется переход на первый оператор функции summa.

mov c,AX присвоение переменной с суммы (а + b) из АХ;

end; завершающая операторная скобка ассемблерного кода;

end. завершающий оператор основной программы.

Полный текст программы приводится в Приложении 7.

4.4. Содержание отчета:

В отчете необходимо привести следующее:

Характеристики лабораторной вычислительной системы.

Блок–схемы алгоритмов, исходный модуль и результаты тестирования разработанной программы.

Краткие выводы по работе, в которых необходимо отразить принципы модульного программирования, организации подпрограмм, механизмы передачи параметров и вызова процедур и функций.

4.5. Контрольные вопросы и задания:

1. Объясните принципы организации и работы стека в МП і80х86.

2. Объясните механизм передачи параметров подпрограмм через регистры.

3. Объясните механизм передачи параметров подпрограмм через стек.

4. Объясните различия между передачей параметров по адресу и по значению.

5. Для чего необходимы коды пролога и эпилога в подпрограммах.

6. В чем различие между дальним и ближним вызовами подпрограмм.

Цель работы: Изучить основные принципы функционирования, форматы данных и систему команд математического сопроцессора і80х87. Получить практические навыки разработки программ для микропроцессоров со стековой архитектурой.

Перед работой необходимо проработать теоретический материал по литературе [5-7] и конспект лекций, ознакомиться с архитектурой, принципами функционирования и системой команд математического сопроцессора і80х87, форматами чисел с плавающей запятой, способом записи арифметических выражений с помощью обратной польской нотации.

|

|

|

5.1.1. Представление действительных чисел в формате с плавающей запятой. Числа в экспоненциальном формате (научная нотация) представляются в виде:

,

,

где f – мантисса, е – порядок числа.

Поскольку в представлении числа участвуют два параметра f и е, такая форма записи является неоднозначной. Для устранения этой неоднозначности принято ограничивать диапазон допустимых значений мантиссы [1,2[. При использовании двоичного представления целая часть мантиссы всегда будет содержать единицу, которую, следовательно, можно не хранить. Этот механизм называется использованием неявного старшего бита. Для представления знака мантиссы используется прямой код – модуль мантиссы и знаковый бит хранятся независимо. При представлении порядка используется excess - формат числа:

h=е+ 2N- 1 -1,

где h -характеристика числа, N – разрядность характеристики.

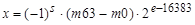

В математическом сопроцессоре і80х87 используются 3 формата представления чисел в формате с плавающей запятой (см. рис. 5.1). В формате расширенной точности для хранения данных отводится 80 битов (см. рис.5.1,а), из которых 64 бита отводится на мантиссу, 15 бит – на порядок и 1 - на знак. При этом число х представляется, как:

,

,

где s – знаковый разряд, m - разряды мантиссы. Причем в расширенном формате целая часть мантиссы, равная 1, не отбрасывается, а хранится в 63 бите.

В формате с двойной точностью для хранения данных отводится 64 бита (см. рис.5.1,б), из которых 52 бита отводятся на мантиссу, 11 битов – на порядок и 1 - на знак. При этом число х представляется, как:

.

.

Целая часть мантиссы в формате с двойной точностью отбрасывается.

|

|

|

В формате с одинарной точностью для хранения данных отводится 32 бита (см. рис.5.1,в), из которых 23 бита отводятся на мантиссу, 8 битов – на порядок и 1 - на знак. При этом число х представляется, как:

.

.

Целая часть мантиссы в формате с одинарной точностью отбрасывается.

Рис. 5.1. Форматы представления действительных чисел

в математическом сопроцессоре і80х87.

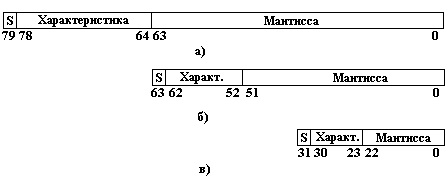

Рассмотрим пример представления числа 7.375 при использовании формата одинарной точности: 7.375 =111.011b. Хранимая мантисса будет равна 11011b, a порядок 2+127=129=10000001b. Так, как число положительное, знаковый бит равен 0. Полное двоичное представление числа 7.375 в формате одинарной точности приведено на рис.5.2.

Рис. 5.2. Представление числа 7.375 в формате одинарной точности.

5.1.2. Архитектура математического сопроцессора і80х87. Для обработки чисел с плавающей запятой в архитектуре вычислительных систем на базе микропроцессора і80х86 предусмотрен специализированный вычислительный блок – математический сопроцессор. Начиная с модели микропроцессора і486, математический сопроцессор выполняется в одном корпусе с центральным процессором и позволяет существенно (в 10 и более раз) увеличить скорость вычислений при выполнении операций над числами с плавающей запятой.

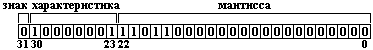

Сопроцессор і80х87 аппаратно представлен следующим набором регистров (см. рис.5.3):

1. Восемь регистров данных R0-R7 – составляющих основу стека сопроцессора;

2. Три служебных регистра: регистр управления CWR, регистр состояния SWR, регистр слова тегов TWR.

3. Регистры указатели данных DPR, IPR – используются для запоминания адреса команды, вызвавшей исключение.

Рис. 5.3. Архитектура математического сопроцессора і80х87.

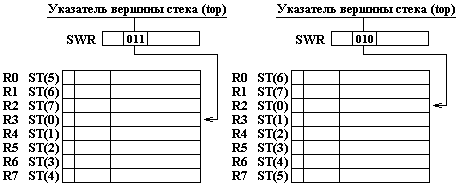

Регистровый стек сопроцессора организован по принципу кольца - нет регистра, аппаратно указывающего на вершину стека. Все регистры R0-R7 функционально равноправны. Вершина стека является плавающей. Данный механизм реализуется с помощью системы команд сопроцессора, оперирующих не с физическими регистрами, а с логическими номерами этих регистров (ST0-ST7). В специально отведенном поле top регистра состояния SWR, фиксируется номер аппаратного регистра стека (R0-R7), являющегося в данный момент текущей вершиной стека. На рис.5.4,а показан пример, когда текущей вершиной стека является физический регистр R3 (ST0), затем данные записываются в стек и текущей вершиной (см. рис. 5.4,б) становится физический регистр R2 (ST0). В 16 – разрядном регистре тегов TWR хранятся 2 -разрядные значения признаков, по содержимому которых можно судить о наличии данных в физических регистрах R0-R7 (см. рис. 5.3.).

|

|

|

а) б)

Рис. 5.4. Физическая и логическая нумерации регистров сопроцессора і80х87.

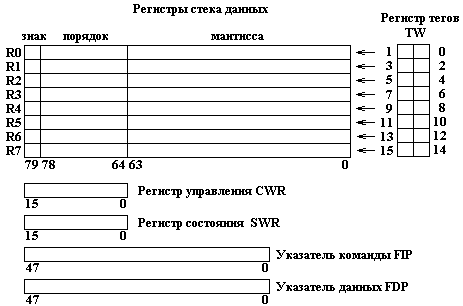

Формат регистра статуса SWR приведен на рис.5.5. Регистр статуса содержит 6 флагов исключительных ситуаций (exceptions flags), битов sf и es, отвечающих за корректность работы стека и общего функционирования сопроцессора соответственно, 4-х битов-флагов с0-с3, в которых отражаются признаки результата последней команды, поля top, в котором фиксируется номер аппаратного регистра стека (R0-R7), являющегося текущей вершиной стека.

Рис. 5.5. Формат регистра статуса SWR сопроцессора і80х87.

Формат регистра управления CWR сопроцессора і80х87 представлен на рис. 5.6. В регистре CWR содержатся 6 масок исключений для разрешения/запрета исключительных ситуаций, фиксируемых в регистре SWR, поле управления точностью вычислений рс (выбор форматов данных расширенной, двойной, одинарной точности), поле управления округлением результата операции.

Рис. 5.6. Формат регистра управления CWR сопроцессора і80х87.

Необходимо отметить, что внутренним форматом данных в сопроцессоре і80х87 является формат расширенной точности, а остальные форматы образуются путем округления.

5.1.3. Основные команды сопроцессора і80х87. Постфиксная форма записи математических выражений. В связи с тем, что в сопроцессоре і80х87 используется стековая архитектура, формат его команд и принцип программирования несколько отличаются от классических представлений. Для оптимального использования стековой архитектуры сопроцессора применяется постфиксная запись арифметических выражений (сначала записываются операнды, а затем знак арифметического действия). Например, с учетом старшинства операций выражение:

|

|

|

А+В*С= ВС*А+,

где слева – стандартная (инфиксная) форма записи, справа – соответствующая постфиксная.

Для упрощения работы с постфиксной нотацией математические выражения удобно представлять в виде деревьев, в узлах которых расположены операции, а в ветвях - операнды. При использовании сопроцессора необходимо поместить сначала операнды в стек, а затем выполнить действие.

Рассмотрим основные команды сопроцессора і80х87.

Команды для выполнения основных арифметических операций:

fadd - команда сложения: (ST0)=(ST1+ST0);

fsub - команда сложения: (ST0)=(ST1-ST0);

fmul - команда сложения: (ST0)=(ST1*ST0);

fdiv - команда деления: (ST0)=(ST1/ST0)

fsqrt - команда извлечения квадратного корня: (ST0)=sqrt(ST0).

Команды пересылки данных:

fld m - команда загрузки в ST0 значения из ячейки памяти m: (ST0)=m;

fst m - команда извлечения данных из ST0 в ячейку памяти m: m=(ST0);

fstp m - команда извлечения данных из ST0 в ячейку памяти m: m=(ST0)

c последующим удалением значения m из стека

В качестве m могут использоваться 32, 64, 80 разрядные ячейки памяти, описанные в Pascal как single, double и extended.

Рассмотрим пример выполнения арифметического действия С=А+В с использованием сопроцессора:

fld A загрузка в ST0 значения в ячейке А;

fld B загрузка в ST0 значения в ячейке В;

fadd выполнение сложения;

fstp С запись значения из ST0 в C и удаление значения С из стека.

Иллюстрация изменения значений в регистрах сопроцессора во время проводимых действий приводится на рис. 5.7.

|

|

|

|

|

Дата добавления: 2014-12-07; Просмотров: 491; Нарушение авторских прав?; Мы поможем в написании вашей работы!