КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Сумматоры и арифметические устройства

|

|

|

|

В самом начале (Тема 1) этого пособия было указано, что алгебра логики и двоичная арифметика – совершенно разные математические методы описания дискретной информации, хоть и оперируют внешне схожими объектами (0 и 1). С помощью логических элементов, однако, можно воспроизводить действия над разрядами двоичных чисел, совпадающие с правилами двоичной арифметики. Этот факт, собственно, и лежит в основе построения арифметико-логических устройств компьютеров.

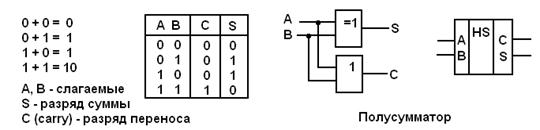

Устройство на логических элементах, которое выполняет арифметическое сложение двух двоичных разрядов, вырабатывает значения суммы и переноса, но само не получает перенос из предыдущего разряда, называется полусумматор. Такая схема имеет, следовательно, два входа и два выхода.

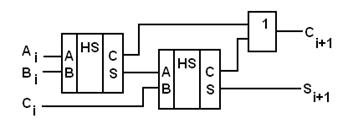

Из двух полусумматоров и одного элемента ИЛИ можно составить полный одноразрядный сумматор, который вычисляет сумму двух двоичных разрядов с учётом переноса и сам вырабатывает перенос. Наконец, из нескольких одноразрядных сумматоров, соединяя их по цепи переноса, можно построить многоразрядный сумматор.

Существуют также схемы для увеличения двоичного кода числа на единицу – инкременторы и уменьшения на единицу – декременторв. Схемы этих устройств оставляем для самостоятельного рассмотрения.

Тема 9, Цифровые устройства с памятью

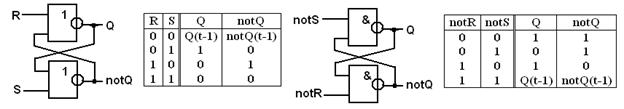

Триггер из двух логических элементов – самое простое устройство, способное запоминать один бит информации, то есть сколь угодно долго находиться в одном из двух возможных состояний. Классические варианты такой схемы строятся либо на элементах ИЛИ-НЕ, либо на элементах И-НЕ и называются RS-триггер (Reset – сброс, Set - установка).

Задание. Смоделировать работу RS-триггера на элементах И-НЕ со следующими параметрами входных сигналов:

|

|

|

GEN [0 0] notS (S0.2 S1/2)

GEN [0 0] notR (S0.4 S1/2)

Обратить внимание на то, как ведёт себя триггер при переходе от комбинации входных сигналов (0 0) к комбинации (1 1). Обсудить с преподавателем понятие «запрещённая комбинация».

Существует множество других, в определённом смысле более совершенных, схем триггеров, например:

Здесь показаны схемы синхронного RS-триггера и так называемого прозрачного D-триггера («прозрачная защёлка»). Описание теоретических аспектов работы этих, как и нижеследующих, устройств здесь приводиться не будет – для этой цели имеется обширная учебная литература.

Задание. Смоделировать работу приведённых схем. На вход С следует подать периодический сигнал (меандр) с периодом повторения 2 цикла. На информационные входы подать сигналы с периодами повторения, существенно большими, чем C, например, 4…6 циклов. Пронаблюдать переключение триггеров по изменению состояний выходов. В случае затруднений посмотрите текст CMD-файла для следующей схемы.

D-триггер этого типа прозрачен для входных сигналов при C=1. Промоделировать этот эффект. Далее рекомендуется добавить к этим схемам цепи (входы) для подачи сигналов асинхронной установки-сброса, как показано в следующем примере, и использовать эти входы до начала действия сигнала C.

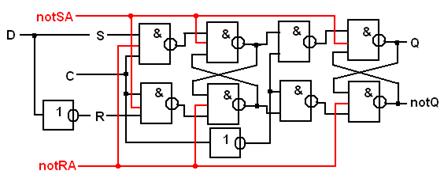

Следующее устройство, которое мы будем рассматривать – это двухступенчатый (двухтактный) RS-триггер.

На цепь, помеченную буквой D и содержащую инвертор, сначала не следует обращать внимания. Такой триггер, состоящий из двух ступеней, непрозрачен для входных сигналов ни при C=0, ни при C=1. Здесь предусмотрены входы асинхронной установки в 1 (notSA) и сброса в 0 (notRA) с низким активным уровнем сигнала. Запрещённая комбинация существует и для данного триггера, что будет видно, наряду с другими особенностями поведения, при моделировании:

|

|

|

|

|

|

|

|

Дата добавления: 2014-12-07; Просмотров: 383; Нарушение авторских прав?; Мы поможем в написании вашей работы!