КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Готовимся к ГИА по русскому языку 4 страница

|

|

|

|

- описание организации процедур ввода-вывода.

Существуют два основных типа архитектуры – фоннеймановская и гарвардская. На рис. 4.2 приведена фоннеймановская архитектура, которую предложил в 1945 г. американский математик Джо фон Нейман. Особенность этой архитектуры заключается в том, что программа и данные находятся в общей памяти, доступ к которой осуществляется по одной шине данных и команд.

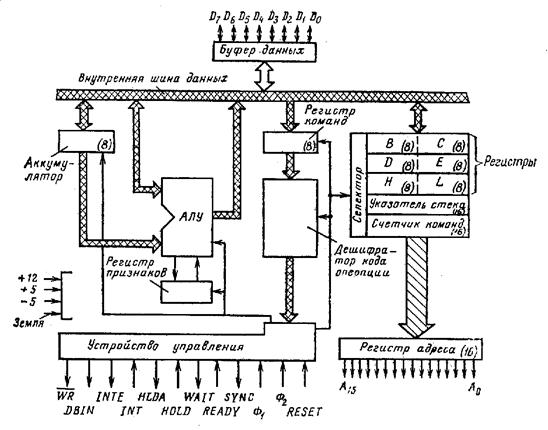

Рис.4.2. Блок-схема микропроцессора.

Гарвардская архитектура впервые была реализована в 1944 г. Ее особенностью является то, что память данных и память программ разделены и имеют отдельные шины данных и шины команд, что позволяет повысить скорость микропроцессорных систем.

Микропроцессор состоит из арифметико-логического устройства (АЛУ), регистров, внутренней шины данных, устройства управления.

Арифметико-логическое устройство предназначено для выполнения арифметических и логических операций.

К арифметическим операциям относятся, как правило, операции сложения и вычитания.

К логическим операциям относятся логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ.

Данные, предназначенные для обработки в АЛУ, или операнды, могут поступать в АЛУ одновременно из разных мест:

- данные передаются из аккумулятора и регистра общего назначения;

- данные передаются из аккумулятора и через буфер шины данных из памяти.

Схема организации ЦП соответствует одноадресной машине, так как при этом один из операндов всегда поступает из аккумулятора, другой передается либо из одного регистров общего назначения или из памяти. Таким образом, одно из чисел всегда необходимо предварительно разместить в аккумуляторе. Результат вычисления размещается в аккумуляторе.

|

|

|

Регистр признаков.

Выполнение какой-либо операции может ставиться в зависимость от значения результата выполнения предыдущей операции. Подобная ситуация возникает в том случае, когда при сложении появляется единица переноса.

Регистр признаков

| Признак переноса | Признак знака | Признак нуля | Признак всп.переноса | Признак переполн. | Признак четности |

Чтобы можно было обратиться к информации о результатах вычислений, АЛУ соединяется со специальным набором триггеров, которые устанавливаются в 1 или сбрасываются в 0 в зависимости от результата произведенных вычислений. Каждый из триггеров хранит какой-то признак, а в совокупности эти триггеры образуют регистр признаков. Таким образом, регистр признаков содержит информацию о данных, пересылаемых из АЛУ в аккумулятор после выполнения операции.

Признак переноса.

Одним из важнейших признаков является признак переноса. При сложении в АЛУ двух 8-разрядных чисел этот признак показывает, нужно ли переносить единицу в младший значащий разряд следующего байта.

10111000

+

11011010

_________

10010010

Признак переноса равен 1.

Признак переноса также указывает, нужно ли занимать единицу при вычитании двух 8-разрядных чисел.

Если АЛУ имеет операцию вычитания, то вычитание осуществляется по этой команде. Если нет, то необходимо получить дополнительный код числа и затем сложить.

Признак вспомогательного переноса.

Признак вспомогательного переноса устанавливается в единицу, если происходит перенос из разряда b3 в разряд b4. Этот признак используется при сложении чисел, записанных в двоично-десятичном коде BCD. Независимо от причины, порождающей перенос из разряда b3 в разряд b4, необходимо применение десятичной коррекции. При любой обработке чисел, записанных в коде BCD, программист должен учитывать в соответствующих командах возможность использования признака вспомогательного переноса. Если этого не делать, то признак автоматически игнорируется.

|

|

|

При сложении чисел 19 и 09, записанных в коде BCD. Единица переноса из разряда b3 в разряд b4 в процессе сложения используется обычным образом. Вместе с тем эта единица воздействует на значение признака вспомогательного переноса, который устанавливается соответствующим образом. Это означает, что необходимо применение десятичной коррекции, которая выполняется автоматически в соответствии с содержащимися в команде указаниями.

0001 1001 (BCD)=19

+

0000 1001 (BCD)=09

_________

0010 0010 (BCD)=28

0010 0010

+

0000 0110 + 6 – коррекция

_________

0010 1000 (BCD)=28

Признак нуля.

Признак нуля отмечает случай появления в АЛУ после выполнения какой-либо операции результата 00000000. Этот признак используется, например, для организации циклов ожидания.

Признак знака.

Отрицательные числа представляют вычислительной машине в виде дополнительных кодов. В этом случае старший значащий разряд может нести не только цифровое значение, но и знак числа: если в старшем значащем разряде стоит 1, то число отрицательное, если 0, то число положительное. Старший значащий разряд запоминается в признаке знака для дальнейшего использования.

Признак переполнения.

Вычисления с использованием дополнительных кодов производятся над словами определенной длины. Если в процессе вычислений получается результат большей длины, то должен вырабатываться сигнал, требующий расширения длины слова. Если такое расширение невозможно, то вычисления должны останавливаться. Средством индикации того, что возникла подобная ситуация, является признак переполнения.

Признак четности.

Этот признак устанавливается равным единице, если в результате операции общее число единиц является четным. Признак четности используется для контроля на четность данных при их передаче; он позволяет выявить ошибки, которые при этом могут возникать.

Регистр команды и дешифратор кода операции.

Вид каждой операции определяется с помощью кода соответствующей команды. В 8-битной ЭВМ можно различать 256 кодов. Число байт, отводимых для записи команды, определяется типом операции. В микро-ЭВМ максимальное число этих байт обычно равно трем.

|

|

|

Код операции, указывающий, как происходит обработка данных при выполнении команды, всегда размещается в первом байте. Если вся команда занимает 1 байт, то для кода операции отводится часть этого байта, например, 2 бита. Если команда занимает 3 байта, то для кода операции отводится весь первый байт.

Весь первый байт кода команды считывается из памяти и передается в регистр команды в течении цикла считывания независимо от того, какая его часть отведена для записи кода операции. Декодирование содержимого первого байта позволяет определить следующее:

- сколько байтов содержится в команде;

- является ли содержимое второго и третьего байтов в совокупности адресом памяти, по которому хранятся предназначенные для обработки данных;

- какая должна выполняться операция.

Для декодирования первый байт передается из регистра команды в дешифратор кода операции, по результатам работы которого под воздействием тактовых сигналов вырабатывается нужная последовательность сигналов управления. Это приводит к считыванию второго и третьего байтов из памяти, если это необходимо, а также к собственно выполнению операции, предписываемого командой.

Регистры общего назначения.

ЦП содержит определенный набор регистров общего назначения. Эти регистры обеспечивают быстрый доступ к хранящимся в них операндам. Для адресации регистров общего назначения используется укороченное адресное поле длиной три бита. С помощью слова такой длины можно различать 8 регистров. Это регистры B,C,D,E,H,L. Эти регистры объединены попарно, что позволяет обрабатывать слова длиной как 8 бит, так и 16 бит.

Счетчик команд.

Счетчик команд указывает, где в памяти расположены байты данной команды. Устройство управления увеличивает содержимое счетчика команд на единицу всякий раз, когда байт кода команды передается из памяти в ЦП. Если код команды состоит из двух байт, то ее считывание происходит за два шага. Перед началом считывания счетчик команд уже содержит адрес байта текущей команды, так как содержимое его было увеличено на единицу; в конце процедуры считывания предыдущей команды первый байт сразу может передаваться в ЦП, после чего содержимое счетчика команд снова увеличивается на единицу. Теперь счетчик содержит адрес второго байта текущей команды, после передачи которого в ЦП содержимое счетчика команд опять увеличивается на единицу и определяет адрес первого байта следующей команды.

|

|

|

Указатель стека.

16 разрядный регистр, который предназначен для адресации ячеек стековой памяти и носит название указателя стека. Указатель стека определяет адрес ячеек памяти в стеке, в которых хранится нужный адрес возврата.

Регистр адреса.

Чтение и запись информации в память может происходить, если определено значение соответствующего адреса памяти. Этот адрес указывает ячейку памяти, предназначенную для записи или считывания байта команды или байта данных. ЦП передает адрес из регистра в память по шине адреса. Для доступа к памяти требуется некоторое время, в силу чего возможность обратиться к нужному слову в памяти появляется не сразу. Существование такой задержки обусловливает необходимость хранения адреса, сформированного ЦП, в течение определенного промежутка времени. Для этого в большинстве ЭВМ встраивается специальный регистр, предназначенный для хранения адреса памяти и называемый регистром адреса.

Генератор тактовых сигналов

События в микро-ЭВМ должны происходить в нужной последовательности и скоординировано, что требует организации управления событиями во времени. Такое управление осуществляется с использованием интегрального генератора тактовых сигналов. Генератор тактовых сигналов может размещаться как на том же кристалле, что и микропроцессор, или в виде отдельной микросхемы.

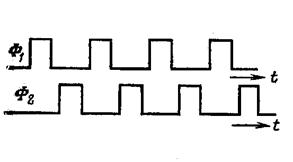

Сигналы тактирования, обычно обозначаемый Ф, могут представлять собой последовательность прямоугольных сигналов. В большинстве случаев используется пара сигналов тактирования: Ф1 и Ф2, представляющих собой две последовательности прямоугольных сигналов с одинаковой амплитудой, частотой и скважностью, но сдвинутых по фазе на 180° (рис.4.1).

Рис.4.1. Тактовые импульсы.

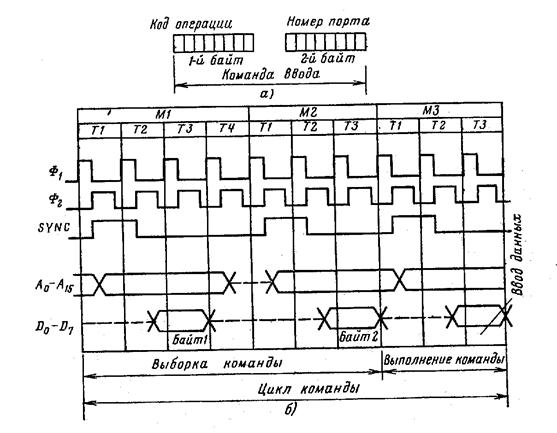

При рассмотрении работы микропроцессора во времени оперируют терминами цикл команды, машинный цикл, состояние (рис.4.1).

Циклом команды называют время, необходимое для считывания команды из памяти и ее исполнения. Цикл команды реализуется за 1-5 машинных циклов, точное число которых зависит от сложности команды и равно числу обращений ЦП к памяти или одному из устройств ввода-вывода. Таким образом, число машинных циклов в цикле команды определяется тем, сколько раз используется шина данных, и цикл любой команды состоит, по меньшей мере, из одного машинного цикла, так как в самом простом случае необходимо извлечь из памяти 1 байт команды и передать его в ЦП.

Каждый машинный цикл состоит из определенной последовательности элементарных действий, называемых состояниями (тактами). Например, для считывания команды необходимо сначала определить значение нужного адреса памяти и декодировать его. Только после этого первый байт команды можно передавать в ЦП и записывать его в регистр команд. Таким образом, состояние – это простейшее действие, которое может выполнено в микро-ЭВМ. Состояние выполняется в течение одного периода сигнала тактирования, а в отдельном машинном цикле может быть от трех до пяти состояний.

Для определения времени выполнения команды нужно знать, какое число состояний содержится в цикле команды и чему равен период сигнала тактирования.

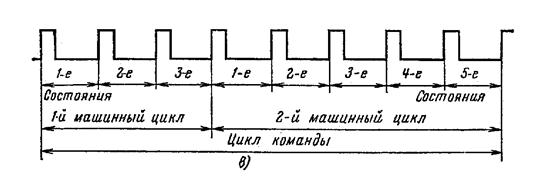

Рис.4.2.Диаграммы цикла команды.

Устройство управления

Устройство управления является одним из важнейших блоков ЦП. Совместно с генератором тактовых сигналов устройство управления обеспечивает, чтобы события в микро-ЭВМ происходили в правильной последовательности.

После извлечения команды из памяти и ее дешифрирования устройство управления генерирует последовательность сигналов, необходимую для выполнения команды.

Кроме этого, устройство управления способно самостоятельно реагировать на различные внешние сигналы, например, на сигналы прерывания от внешних устройств. Сигнал готовности, поступающий из памяти или порта УВВ, также воспринимается устройством управления.

Временные диаграммы

Характеристики МП обычно публикуются их изготовителями в виде временных диаграмм, на которых последовательность событий представляется как функция времени, причем временную диаграмму можно построить для любой операции, выполняемой микро-ЭВМ.

Ниже рассматривается временная диаграмма выполнения команды ввода (рис.4.3).

Рис.4.3. Временные диаграммы.

Команда ввода занимает два байта, первый из которых, содержащий код операции, указывает, какие действия нужно совершить (принять данные из порта ввода). Второй байт указывает на операнд, т.е. из какого порта должны быть приняты данные.

На рис.4.3. изображены:

- сигналы тактирования Ф1 и Ф2, изменяющиеся в противофазе;

- сигнал синхронизации SYNC, порождаемый сигналом Ф2. Появление каждого сигнала SYNC означает начало нового машинного цикла;

- наличие или отсутствие передачи сигналов А0-А15 по шине адреса. Так как для общего случая невозможно указать конкретные значения этих сигналов, то указывается, что по шине адреса передается или не передается некоторая информация. Отсутствие информации обозначается пунктирной линией.

- наличие или отсутствие передачи сигналов D0-D7 по шине данных.

На временной диаграмме изображены три машинных цикла: М1-М3. Код операции считывается в течение цикла М1. В течение цикла М2 адрес операнда считывается из памяти, а в течение цикла М3 происходит выполнение команды, т.е по адресу порта ввода данные считываются и передаются в ЦП. Таким образом, считывание команды производится в течение циклов М1и М2, а ее исполнение в течение цикла М3.

Каждый машинный цикл состоит из определенного числа состояний. Код адреса передается по шине адреса в течение состояния Т2 каждого машинного цикла. В цикле М! – это адрес кода операции в памяти, в цикле М2 – это адрес операнда (номер порта) в памяти, в цикле М№ - это номер порта ввода.

Во время состояния Т2 каждого машинного цикла производится проверка условий, которые могут сделать необходимой задержку в выполнении данного машинного цикла. Одной из причин, которые могут вызвать задержку, может быть разница в быстродействии ЦП и порта УВВ или ЦП и памяти.

Если существуют причины для такой задержки, то ЦП переходит в состояние ожидания; если же причин для задержки нет, то первый и второй байты команды считываются из памяти в течение состояний Т3 машинных циклов соответственно М1 и М2. Эта информация передается в ЦП по шине данных в виде сигналов D0-D7. В течение состояния Т3 машинного цикла М3 команда выполняется, т.е. данные принимаются из порта.

Из временной диаграммы видно, что машинный цикл М1 содержит не три, а четыре состояния. Четвертое состояние отводится для таких действий ЦП, как дешифрирование кода операции.

Ввод информации связан с обращением в порту УВВ, в результате чего для выполнения команды ввода требуется добавить отдельный машинный цикл. В том случае, когда выполнение команды реализуется исключительно средствами ЦП, а необходимость обращения к памяти или УВВ отсутствует, выполнение команды может происходить в течение четвертого или, возможно, пятого состояния предшествующего машинного цикла. Следовательно, существует возможность реализации цикла команды за один машинный цикл.

Внешние выводы микропроцессора

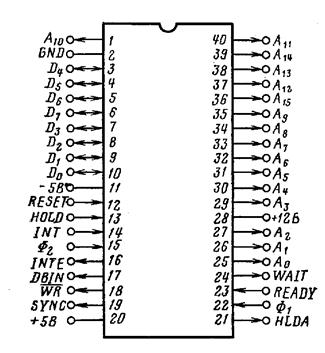

Микропроцессор подключается с помощью внешних выводов, назначение которых приведено на рис.4.4.

Рис.4.4. Конфигурация системы внешних выводов МП.

Все МП должны иметь соединения с шиной адреса, которая используется для передачи адресов памяти или одному из УВВ. Так как адресация 16-разрядная, то необходимо иметь 16 внешних выводов А0-А15. В некоторых МП некоторые выводы шины адреса выполняют двойную функцию: по ним передаются или значения соответствующих бит адреса, или информация о процессах записи-считывания в памяти. Иногда восемь из шестнадцати выводов шины адреса могут использоваться для подключения в шине данных в режиме мультиплексирования.

D0-D7 – выводы двунаправленной шины данных. Шина данных является двунаправленной и поэтому эти выводы используются для передачи информации в ЦП и из него.

Ф1-Ф2 – тактовые входы, на которые подаются сигналы тактирования от внешней ИС.

SYNC – выход синхронизации. С этого вывода снимается сигнал синхронизации, который оповещает память или УВВ о начале нового машинного цикла, чем обеспечивается согласование работы этих устройств с работы ЦП во времени.

Выводы для подключения напряжения питания. На ЦП подается напряжение питания +12, -5, +5 В и он подключается к общей точке GND (ground - земля) источника питания. Другие типы МП могут иметь один источник питания +5 В.

RESET – вход гашения (сброса). По этому входу можно сбрасывать счетчик команд, т.е. устанавливать его значение 0000(16), и затем передавать в регистр адреса нулевой адрес первой исполняемой команды. После подачи сигнала сброса RESET содержимое всех других регистров ЦП остается неопределенным.

WR – выход сигнала "Запись". Информация передается по шине в двух направлениях: из ЦП в память или порт УВВ либо в противоположном направлении. ЦП должен информировать память или порт УВВ о выполнении им операции записи (WRITE) или чтения (READ). ЦП указывает на то, что выполняется операция записи путем подачи сигнала высокого или низкого уровня на вывод WR (write).

READY – вход сигнала готовности. Если необходимо произвести обмен данными между памятью или УВВ и ЦП, то перед началом передачи данных следует указать адрес модуля, которому передается информация или, наоборот, от которого она принимается. Этот адрес декодируется в памяти или порте УВВ, что позволяет определить источник либо место назначения передаваемых данных. Однако, прежде чем сможет начаться действительно начаться обмен данных, происходит некоторый промежуток времени, который называется временем доступа. То, что этот промежуток времени истек, отражается в посылке памятью или портом УВВ сигнала готовности на соответствующий вход МП. Это дает ЦП информацию о том, что может начаться обмен данными.

WAIT – выход сигнала ожидания. ЦП указывает, что он находится в режиме ожидания, путем подачи сигнала на вывод WAIT.

DBIN – выход сигнала "шина данных в режиме ввода". Если в ЦП передаются данные при считывании их из памяти или при выполнении операции ввода, то он указывает на это путем генерации сигнала на выводе DBIN (data bus in). При считывании из памяти сигнал DBIN отображает команду READ, а при выполнении операции ввода команду IN.

HOLD – вход сигнала захвата шин.

HLDA – выход сигнала подтверждения захвата шин. Большие объемы информации, хранящиеся на магнитных дисках, могут передаваться в основную память микро-ЭВМ без вмешательства ЦП. Такой режим называют прямым доступом к памяти (ПДП). В этом режиме ЦП должен отключаться от шин адреса и данных. Это происходит при появлении сигнала захвата шин на входе HOLD. Результатом появления сигнала захвата шин является то, что ЦП отключается от своих шин и информирует об этом другие блоки с помощью сигнала подтверждения захвата шин, подаваемого на выход HLDA (hold acknowledge output).

INT – вход сигнала "запрос прерывания".

INTE – выход сигнала разрешения прерывания. Если возникает необходимость передачи данных от УВВ, то соответствующее устройство посылает запрос прерывания ЦП. Этот сигнал поступает на вывод INT (interrupt). В МП 8080 предусмотрена возможность использования специальной команды, запрещающей ЦП реагировать на запрос прерывания. Если такой сигнал отсутствует, то МП выдает сигнал разрешения прерывания на вывод INTE (interrupt enable). Если сигнал INTE равен 1, то ЦП принимает запрос прерывания; если же сигнал INTE равен 0, то запрос прерывания от УВВ игнорируется ЦП.

Слово состояния процессора

Микропроцессор Intel8080 (КР580) имеет десять типов машинных циклов, которые могут быть при выполнении команды:

- выборка байта команды;

- чтение из памяти;

- запись в память;

- чтение из стековой памяти;

- запись в стековую память;

- ввод;

- вывод;

- обработка прерывания;

- останов;

- обработка прерывания при останове.

При этом первым машинным циклом всегда является выборка команды. Для определения типа машинного цикла в первом состоянии каждого машинного цикла на шину данных передается 8-битный код, который запоминается во внешнем регистре и используется для формирования системных управляющих сигналов для обращения к памяти, периферийным устройствам. Назначение каждого разряда в коде слова состояния процессора приведено в таблице 4.1, структура слова состояния приведена в таблице 4.2.

Таблица 4.1. Слово состояния процессора

| Символи- ческое обозна-чение | Бит шины данных | Смысл сообщаемой информации |

| D0 | Сигнал подтверждения запроса на прерывание, используется для разрешения передачи команды вызова подпрограммы обработки запроса прерывания |

| D1 | Признак записи-вывода, указывает, что в текущем машинном цикле будет выполняться запись в память или вывод кода в порт вывода (при  ) )

|

| D2 | Признак указывает, что на шину адреса передается адрес из указателя стека, используемый для адресации области стековой памяти |

| D3 | Признак подтверждает выполнение команды останова

|

| D4 | Признак вывода, указывает, что шина адреса содержит адрес порта вывода, а шина данных будет содержать данные при сигнале

|

| D5 | Признак указывает, что МП находится в цикле выборки первого байта команды |

| D6 | Признак ввода, указывает, что шина адреса содержит адрес порта ввода и входные данные передаются по шине данных при сигнале

|

| D7 | Признак указывает, что шина данных будет использована для приема данных из памяти. |

Таблица 4.2. Структура слова состояния МП Intel 8080

| Бит шины данных | Информация о состоянии | Выборка команды | Чтении из памяти | Запись в память | Чтение из стека | Запись в стек | Ввод | Вывод | Подтвержде-ние прерывания | Подтвержде-ние останова | Подтвержде-ние прерывания во время останова |

| D0 |

| ||||||||||

| D1 |

| ||||||||||

| D2 |

| ||||||||||

| D3 |

| ||||||||||

| D4 |

| ||||||||||

| D5 |

| ||||||||||

| D6 |

| ||||||||||

| D7 |

|

Диаграмма переходов при выполнении машинного цикла представлена на рис.4.1, на котором используются следующие обозначения:  - состояние ожидания МП;

- состояние ожидания МП;  - состояние ожидания МП при выполнении команды останова HLT;

- состояние ожидания МП при выполнении команды останова HLT;  - состояние МП, i=1…5.

- состояние МП, i=1…5.

Командный цикл – время, необходимое для выборки, дешифрирования и выполнения команды.

Машинный цикл – время, необходимое для передачи данных в память или в порты ввода/вывода или обратно.

Такт (состояние) – промежуток времени между двумя соседними переходами тактового сигнала Ф1 из отрицательного состояния в положительное. Такт совпадает с одним периодом тактового генератора.

Машинный цикл длится от трех до пяти тактов. Три такта используются для осуществления доступа к модулю памяти или ввода/вывода. Остальные два такта используются для декодирования и выполнения команды.

1. Во время такта Т1 цикла М1 ЦП помещает содержимое СК на адресную шину, а информацию о состоянии (нужную в цикле выборки команды) на шину данных. Эти операции выполняются непосредственно за фронтом тактового сигнала Ф2. Первая часть цикла используется для завершения предыдущего цикла с целью предотвращения возможного наложения. Максимальное время задержки адреса составляет 200 нс, а максимальное время задержки данных 0 220 нс.

2. Во время такта Т2 цикла М1 информация о состоянии фиксируется внутри процессора и информационная шина используется либо для вывода данных, либо переводится в состояние ожидания ввода данных (DBIN=1). Все эти действия выполняются непосредственно за фронтом тактового сигнала Ф2, за исключением фиксации состояния, которая происходит по срезу сигнала Ф1.

3. Во время такта Т3 цикла М1 осуществляется либо передача данных в процессор (цикл чтения), либо формирование сигнала записи  . Чтобы данные были приняты корректно, этот сигнал должен удовлетворять временам установки как во время сигнала Ф1, так и во время сигнала Ф2. Минимальные времена установки составляют 30 нс до среза Ф1 и 130 нс до среза Ф2. Сигнал записи прекращается примерно через 130 нс после смены данных и адреса относительно фронта Ф2 в следующем цикле.

. Чтобы данные были приняты корректно, этот сигнал должен удовлетворять временам установки как во время сигнала Ф1, так и во время сигнала Ф2. Минимальные времена установки составляют 30 нс до среза Ф1 и 130 нс до среза Ф2. Сигнал записи прекращается примерно через 130 нс после смены данных и адреса относительно фронта Ф2 в следующем цикле.

|

|

|

|

|

Дата добавления: 2014-12-27; Просмотров: 558; Нарушение авторских прав?; Мы поможем в написании вашей работы!