КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

N-МОП элемент памяти

ТТЛ элемент памяти.

Электронное устройство предназначенное для хранения бита информации будем называть запоминающим элементом. Рассмотрим схему и работу запоминающего элемента ТТЛ. Схема приведена на рис. 76. ТТЛ элемент памяти представляет собой схему статического триггера собранного на транэисторах VT1 и VT2. Особенность схемы состоит в том, что использованы двухэмиттерные транзисторы. Электронное устройство предназначенное для хранения бита информации будем называть запоминающим элементом. ТТЛ элемент памяти представляет собой схему статического триггера собранного на транэисторах VT1 и VT2. Особенность схемы состоит в том, что использованы двухэмиттерные транзисторы.

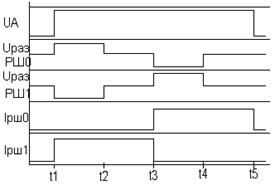

На диаграмме приняты следующие обозначения: UA -- напряжение на адресном проводнике; Uраз -- напряжение на разрядной шине; Iрш0 -- ток в разрядной шине нулей. Показаны режимы: 0 - t1 -- хранение; t1 - t2 -- запись “1”; t2 - t3 -- чтение “1”; t3 -t4 -- запись “0”; t4 - t5 -- чтение “0”.

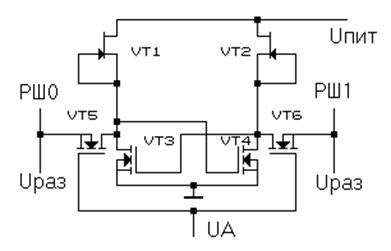

Для серий логических элементов, имеющих положительное напряжение питания, лучше всего использовать МОП транзисторы с индуцированным каналом типа “n”, так как у этих транзисторов напряжение питания и напряжение отсечки -- положительны. Схемотехнической основой построения ячейки является статический триггер, у которого в стоковых цепях транзисторов использованы n - канальные полевые транзисторы в режиме источников тока. Схема ячейки приведена на рис. 78.

Транзисторы VT1, VT2 -- n - канальные с изоляцией канала от затвора обратносмещённым p-n переходом в режиме источника тока используются в качестве стоковых нагрузок транзисторов VT3,VT4, которые образуют статический триггер. Транзисторы VT5,VT6, так называемые боковые транзисторы, предназначены для управления записью и считыванием информации в статическом триггере.

|

|

Дата добавления: 2014-12-24; Просмотров: 629; Нарушение авторских прав?; Мы поможем в написании вашей работы!