КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

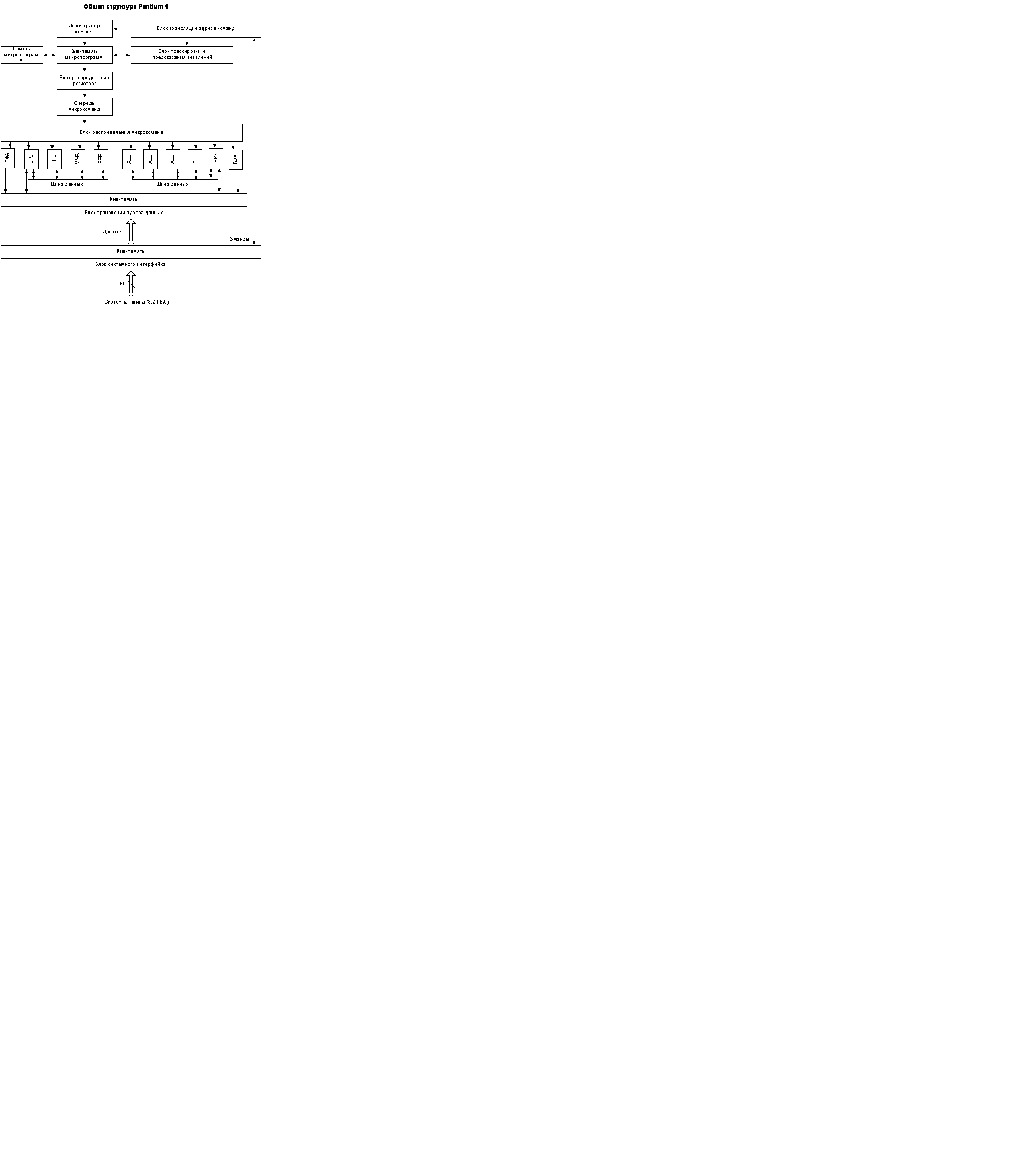

Микропроцессор Pentium 4

ALU - блоки целочисленной обработки (ОУ);

БРЗ - блоки регистров для целочисленных операндов;

БФА – блок формирования адреса операндов (один для выборки, другой для записи операндов);

FPU –устройство обработки с плавающей точкой;

MMX – SIMD-обработка целочисленных операндов; 8, 16, 32-х разрядные операнды на базе 128-разрядного регистра;

SEE – пакетные 128-битные SIMD-операции с плавающей точкой и перестройкой разрядности;

SEE2 – комбинирование MMXи SЕE.

Особенности:

- Гарвардскаяструктура с разделением потоков команд и данных.

- Суперскалярная архитектура, обеспечивающая параллельное выполнение нескольких команд в параллельно работающих исполнительных устройствах.

- Динамическое изменение последовательности команд по готовности данных.

- Конвейерное исполнение команд и операций на функциональных операционных устройствах.

- Предсказание направления ветвления.

Во входном окне – 126 CISC команд (на ЯВУ). Дешифратор команд формирует последовательность микрокоманд на основании поступивших команд из программ на ЯВУ. В кэш-памяти микропрограмм может размещаться до 12000 микрокоманд для 126 команд CISC. Микрокоманды (для 40-ка CISC-команд) размещаются в очереди микрокоманд. Эти микрокоманды направляются на исполнительные устройства по мере готовности данных и наличия свободных ОУ, пригодных для реализации данных микрокоманд. Эти функции реализует блок распределения микрокоманд. В ОУ реализуется параллельное выполнение микрокоманд на основе конвейерного принцмпа.

Число ступеней конвейера достигает 20, т.е. в одном конвейере может находиться до 20-ти микрокоманд.

В основе построения операционных устройств ядра – RISC-архитектура.

42 млн. транзисторов н7а кристалле.

Архитектура микропроцессора в целом: CISK+RISK.

|

|

Дата добавления: 2015-04-24; Просмотров: 377; Нарушение авторских прав?; Мы поможем в написании вашей работы!