КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Сегмент состояния задачи

|

|

|

|

Мультизадачность

Под мультизадачностью понимают способность процессора выполнять несколько задач "одновременно". Конечно, процессор традиционной архитектуры не может выполнять строго одновременно более одного потока команд, однако он может некоторое время выполнять один поток команд, потом быстро переключиться на выполнение другого потока команд, потом третьего, потом — снова первого и т. д. Такая организация вычислительных процессов при высоком быстродействии процессора создает иллюзию одновременности (параллельности) выполнения нескольких задач. Для реализации мультизадачности необходимо: □ располагать быстродействующим процессором;

□ процессор должен аппаратно поддерживать механизм быстрого переключения задач;

□ процессор должен аппаратно поддерживать механизм защиты памяти;

□ использовать специальную мультипрограммную операционную систему.

(Страница192)

Под задачей в мультизадачной системе понимается программа, которая выполняется или ожидает выполнения, пока выполняется другая задача, причем в определение задачи обычно включают ресурсы, требуемые для ее решения (объем памяти, процессорное время, дисковое пространство и др.).

Рассмотрим, как реализуется механизм переключения задач в процессорах x86.

Переключение задач в мультизадачной системе предполагает сохранение состояния приостанавливаемой задачи на момент ее останова. Информация о задаче, сохраняемая для последующего восстановления прерванного процесса, называется ее контекстом. В системе выделяется область оперативной памяти, доступная только ОС, в которой хранятся контексты задач. Для минимизации времени переключения контекста следует сохранять и восстанавливать минимальную информацию о каждой задаче.

|

|

|

В какой-то степени процесс переключения задачи напоминает вызов процедуры. Отличие состоит в том, что при вызове процедуры информация о точке возврата (автоматически) и содержимое некоторых РОН (программно) помещается в стек, что определяет свойство реентерабельности процедур (возможность вызова самой себя). Задачи не являются реентерабельными, т. к. контексты сохраняются не в стеке, а в фиксированной (для каждой задачи) области памяти в специальной структуре данных, называемой сегментом состояния задачи (Task State Segment, TSS), причем каждой задаче соответствует один TSS.

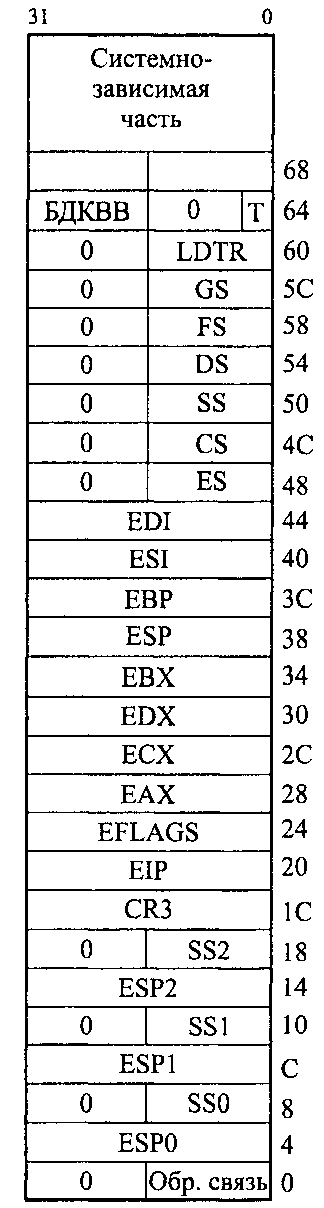

Сегмент TSS определяется дескриптором, который может находиться только в GDT. Формат дескриптора TSS похож на дескриптор сегмента кода и содержит обычные для дескриптора сегмента поля: базового адреса, предела, DPL, биты гранулярности (G=0) и присутствия P, бит S=0 — признака системного сегмента. В поле типа бит занятости B показывает, занята задача или нет. Занятая задача выполняется сейчас или ожидает выполнения. Процессор использует бит занятости для обнаружения попытки вызова задачи, выполнение которой прервано. Поле предела должно содержать значение, не меньшее 67h, что на один байт меньше минимального размера TSS. Формат 32-разрядного TSS представлен на рис. 7.11.

Процедура, которая обращается к дескриптору TSS, может вызвать переключения задачи. В большинстве случаев поле DPL дескрипторов сегментов TSS должно содержать 00, поэтому переключение задач могут проводить только привилегированные программы (на нулевом уровне).

(Страница193)

Рис. 7.11. Сегмент TSS

Сегмент TSS не является ни сегментом кода, ни сегментом данных. Доступ к нему имеет только процессор, но не задача, даже на нулевом уровне! Если предполагается программно использовать сегмент TSS, то следует применить альтернативное именование.

|

|

|

Обращение к дескриптору TSS не предоставляет возможность процедуре считать или модифицировать сегмент TSS. Загрузка селектора дескриптора TSS в сегментный регистр вызывает особый случай. Доступ к сегменту TSS возможен только с помощью альтернативного именования, когда сегмент данных отображен на ту же область памяти.

Сегмент состояния задачи TSS (рис. 7.11) включает в себя содержимое всех пользовательских регистров процессора, причем 8 регистров общего назначения хранятся в сегменте в том же порядке, в каком они помещаются в стек командой pushad. Кроме того, в TSS сохраняются значения трех указателей стека SS i: ESP i для трех уровней привилегий — i  {0, 1, 2}. Сохранение в TSS регистров CS и EIP позволяет осуществлять рестарт задачи, при этом гарантируется правильное действие команд условных переходов, т. к. в TSS сохраняется и EFLAGS. Сохранение в TSS содержимого регистров CR3 и LDTR позволяет для каждой задачи образовывать свой каталог разделов и локальную дескрипторную таблицу.

{0, 1, 2}. Сохранение в TSS регистров CS и EIP позволяет осуществлять рестарт задачи, при этом гарантируется правильное действие команд условных переходов, т. к. в TSS сохраняется и EFLAGS. Сохранение в TSS содержимого регистров CR3 и LDTR позволяет для каждой задачи образовывать свой каталог разделов и локальную дескрипторную таблицу.

В сегменте TSS имеется также несколько дополнительных полей. Поле обратной связи содержит селектор TSS той задачи, которая выполнялась перед данной; с его помощью можно организовать цепь вложенных задач. Поле базы двоичной карты разрешения ввода/вывода (БДКВВ) содержит 16-битовое смещение в данном сегменте TSS, с которого начинается сама двоичная карта ввода/вывода. Эта карта позволяет определить произвольное подмножество адресов в пространстве ввода/вывода, по которым данной задаче разрешено обращаться независимо от уровня привилегий. Если в этом поле — 00h, то карта отсутствует. Бит ловушки T применяется для отладки: когда в TSS T=1, при переключении на данную задачу генерируется особый случай отладки (прерывание 1).

При переключении задач между ними не передается никакой информации, т. е. они максимально изолированы друг от друга. Этим исключается искажения задач и обеспечивается возможность прекращения и запуска любой задачи в любой момент времени и в любом порядке.

С целью экономии времени на процедуру переключения задач все поля TSS разделяются на "статические" и "динамические". К статическим относятся поля указателей стека трех уровней и содержимое регистра LDTR — они остаются неизменными в течение всего времени существования задачи. Содержимое статических полей TSS определяется ОС при создании задачи. Статические поля процессор только считывает при переключении задачи. Поля регистров и поле обратной связи модифицируются при каждом переключении задачи.

|

|

|

До перехода в мультипрограммный режим необходимо определить дескрипторы TSS, разместить сами сегменты TSS в адресном пространстве и правильно инициировать их. Напомним, что селекторы TSS нельзя загружать в сегментные регистры, поэтому для работы с TSS следует пользоваться альтернативным именованием, т. е. псевдонимами этих сегментов. При загрузке начальных значений полей TSS в CS: EIP указывают точку старта программы (задачи), а в регистр SS — селектор сегмента стека с правильным уровнем привилегий. Если предполагается работа задачи на разных уровнях привилегий, следует инициализировать поля SS/: ESPi, а если задача рассчитана на использование локальной дескрипторной таблицы и страничного преобразования, в сегменте TSS потребуется инициировать поля LDTR и CR3.

В сегменте TSS отсутствуют поля для регистров CR0 и CR2, следовательно, их значение не изменяется при переключениях задач. Поэтому страничное преобразование и условия работы с устройством "плавающей арифметики" (определяются полями CR0 и CR2) являются глобальными для всех задач. Для каждой задачи может быть свой каталог разделов, но страничное преобразование может быть разрешено или запрещено только для всей системы. Переключение задач не затрагивает регистры GDTR и IDTR, а также регистры отладки и проверки.

Минимальный размер сегмента TSS должен быть 104 байта (68h). Однако пользователь может увеличить размер сегмента TSS для размещения дополнительной информации, например, состояние устройства регистров сопроцессора "плавающей арифметики" FPU, списка открытых файлов, двоичной карты ввода/вывода и др. Однако когда процессор привлекает TSS для переключения задач, он игнорирует все данные сверх аппаратно поддерживаемых 104 байтами, и эту дополнительную информацию из TSS считывают программно.

|

|

|

|

|

Дата добавления: 2015-04-25; Просмотров: 955; Нарушение авторских прав?; Мы поможем в написании вашей работы!