КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Архитектура ЭВМ 3 страница

|

|

|

|

|

| ||||||||||||

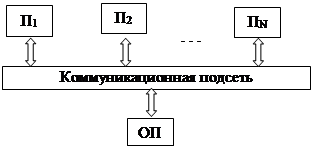

| Рис. 2.4. Вычислительные системы с общей памятью (а) и распределённой памятью (б) |

Вычислительные системы с общей памятью предусматривают все операции обмена информацией с общей памятью, т.е. в этом отношении похожи на рассмотренный выше персональный компьютер. Их производительность ограничена невозможностью выполнения параллельного обмена данными нескольких процессоров с памятью. С другой стороны имеется некоторая компенсация этого недостатка в виде упрощения процедур обмена информацией между процессорами вследствие наличия общего запоминающего устройства.

В зависимости от построения коммуникационной подсети можно построить несколько вариантов многопроцессорных систем по схемам:

· ОКОД (один поток команд – один поток данных);

· МКОД (один поток команд – много потоков данных);

· ОКМД (один поток команд – много потоков данных);

· МКМД (много потоков команд – много потоков данных).

Системы с несколькими потоками данных могут быть реализованы только как системы с распределённой памятью. В системах с одним потоком команд процессоры образуют последовательную технологическую цепочку, в которой информация из памяти читается головным процессором цепочки, передаётся от одного процессора к другому по каналу прямой связи и записывается в память конечным процессором технологической цепочки. Каждый процессор в таких системах специализируется на своей операции, поэтому очень прост и имеет высокое быстродействие. Системы с одним потоком данных называются конвейерными.

В системах с одним потоком команд вовсе процессоры поступают одни и те же команды. Может существовать два варианта построения таких систем:

|

|

|

· все процессоры выполняют одни и те же команды, но работают с разными наборами данных;

· все процессоры выбирают из потока команд только предназначенные им команды.

2.4. Внутренние устройства персонального компьютера

и их характеристики

Ниже рассмотрены разновидности внутренних устройств компьютера и их характеристики. Архитектура устройств будет рассмотрена в дальнейших разделах. Разновидности, характеристики и архитектура внешних устройств будет рассмотрена в соответствующих разделах.

2.4.1. Центральный процессор

Появление микропроцессора явилось революционным прорывом в области вычислительной техники, позволившим приблизить вычислительные машины к пользователям и сделать их индивидуальными инструментами переработки информации. Развитие процессоров пошло по двум направлениям, определившим в принципиальных чертах их архитектуру:

· CISK-процессоры, имеющие полный (расширенный) набор необходимых команд;

· RISK-процессоры, имеющие ограниченный набор быстро исполняемых команд с реализацией команд из расширенного набора с помощью быстро исполняемых команд ограниченного набора;

· MISK-процессоры, имеющие минимальный набор команд и высокое быстродействие.

Центральный процессор выполняет следующие функции:

· чтение и дешифрацию команд из основной памяти;

· чтение данных из ОЗУ и регистров адаптеров и внешних устройств;

· приём и обработку запросов и команд от адаптеров на обслуживание внешних устройств;

· обработку данных и их запись в ОЗУ и регистры адаптеров внешних устройств;

· создание управляющих сигналов для всех прочих устройств компьютера.

Важнейшими характеристиками процессора являются:

· тактовая частота ядра процессора (рабочая частота его внутренних устройств);

· частота системной шины (частота работы основных внутренних устройств или их интерфейсных частей);

|

|

|

· разрядность шины данных, определяющая разрядность вычислительной машины в целом;

· размер адресуемой памяти;

· ёмкость КЭШ-1;

· наличие поддержки КЭШ-2;

· тип архитектуры (CISK, RISK, MISK), определяющий набор команд;

· наличие поддержки ММХ (встроенных команд работы с мультимедийными приложениями);

· тип разъёма для подключения к системной плате (Socket-370, Socket-7, Slot1, Slot2, Slot A);

· напряжение питания.

2.4.2. Оперативное запоминающее устройство

Оперативное запоминающее устройство (ОЗУ) – устройство, которое хранит программу и данные только при включённом питании. С точки зрения пользователя ОЗУ представляет собой множество однотипных устройств, имеющих два состояния (ячеек памяти). Все ячейки памяти организованы в строки и в столбцы. Адрес ячейки при обращении к памяти может быть задан в виде пары чисел, определяющих номера строки и столбца

Для всех ОЗУ определён интерфейс, т.е. набор правил и средств доступа к ячейкам. Для обеспечения возможности обращения к ним ячейкам присвоены номера, которые называются адресами. В состав ОЗУ кроме указанных ячеек памяти входят средства присоединения к системной шине и организации доступа к ячейкам.

Различают два типа таких устройств: статические и динамические. Статические ОЗУ построены на электронных устройствах типа "триггер" – электронных аналогах выключателей. Они имеют более высокое быстродействие, но и более высокую цену. Динамические ОЗУ построены на основе множества конденсаторов, наличие или отсутствие зарядов которых позволяют передавать логические единицы и нули. Поскольку существует саморазряд конденсаторов и разряд их через присоединённые к ним элементы, в состав ОЗУ включены средства регенерации ОЗУ, т.е. восстановление уровней зарядов конденсаторов до стандартных значений. Динамические ОЗУ дешевле статических, но имеют более низкое быстродействие.

К основным характеристикам ОЗУ относятся:

· ёмкость – количество битов, байтов, килобайтов и т.д., которые могут храниться в запоминающем устройстве;

· единица пересылки – количество битов, пересылаемых параллельно в один и тот же момент времени;

|

|

|

· метод доступа к данным – для внутренней памяти произвольный и ассоциативный;

· быстродействие – характеризуется следующими ппрпметрами: время выборки данных, время хранения данных (без регенерации), период обращения, скорость передачи данных;

· физический тип памяти (для современных компьютеров – полупроводниковый);

· физические особенности, например энергонезависимость или способность сохранения информации в процессе считывания и т.д.

· стоимость.

2.4.3. Постоянное запоминающее устройство

Постоянное запоминающее устройство (ПЗУ) хранит информацию независимо от наличия питания. Микросхемы ПЗУ построены по принципу матрицы, в узлах которой имеются перемычки в виде проводников, полупроводниковых транзисторов и диодов, или конденсаторов. Запись информации в ПЗУ сводится к воздействию на указанные перемычки и называется программированием ("прошивкой") ПЗУ. Основным режимом работы ПЗУ является считывание информации.

По способности к перепрограммированию различают ПЗУ следующих видов:

· программируемые при изготовлении;

· однократно программируемые после изготовления;

· многократно программируемые (перепрограммируемые):

§ EPROM – стираемые программируемые ПЗУ;

§ EEPROM – электрически стираемые программируемые ПЗУ;

§ флэш-память;

§ PSM – фазовая память.

В первых двух типах ПЗУ на перемычки оказывается воздействие, приводящее к их необратимым изменениям. При программировании ПЗУ третьего типа изменения перемычек обратимы. В настоящее время популярность не перепрограммируемых ПЗУ резко снизилась.

Характеристики ПЗУ:

· ёмкость – количество битов, байтов, килобайтов и т.д., которые могут храниться в запоминающем устройстве;

· единица пересылки – количество битов, пересылаемых параллельно в один и тот же момент времени;

· метод доступа к данным – для внутренней памяти произвольный и ассоциативный;

· быстродействие – характеризуется следующими ппрпметрами: время выборки данных, время хранения данных (без регенерации), период обращения, скорость передачи данных;

|

|

|

· число циклов перепрограммирования;

· физический тип памяти (для современных компьютеров – полупроводниковый);

· стоимость.

2.4.4. КЭШ-память

Применение КЭШ-памяти является экономичным решением повышения производительности запоминающего устройства без замены всей основной динамической памяти на статическую. Полная замена вызывает существенное повышение цены.

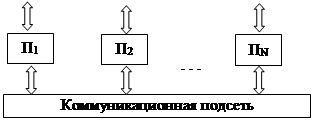

КЭШ-память состоит из двух частей: памяти тегов и памяти данных. Основная память разбивается на блоки по k слов (длина слова кратна целому числу байт). Основная память состоит из М блоков, а КЭШ-память – из С блоков, причём С<М. В КЭШ-памяти находятся копии подмножества блоков основной памяти. Схема взаимодействия КЭШ-памяти и основной памяти показана на рис. 2.5.

|

Рис. 2.5. Принцип действия КЭШ-памяти

При обращении к какой-либо ячейке блока в память данных КЭШ-памяти переписывается весь блок и происходит переадресация обращений к этому блоку на блок, находящийся в КЭШ-памяти. Поскольку вследствие малого объёма КЭШ-памяти копии блоков в ней непрерывно меняются, в памяти тегов помещаются признаки нахождения в ней копий конкретных блоков основной памяти. Такими признаками, например, могут быть номера блоков основной памяти. Указанные признаки называются тегами.

При попытке центрального процессора прочитать слово, находящееся по некоторому адресу из основной памяти происходит проверка наличия блока, содержащего это слово в КЭШ-памяти, и, следовательно, проверка наличия в ней искомого слова. Если этого слова нет, то слово, подлежащее считыванию, вместе со всем блоком записывается в память данных КЭШ-памяти и происходит переадресация обращений к слову основной памяти на слово, находящееся в КЭШ-памяти. Такая ситуация называется промахом (miss). Далее процессор получает запрошенное слово.

Если запрошенное слово в КЭШ-памяти есть, то обращение к основной памяти не происходит, что ускоряет процесс доступа к данным. Такая ситуация называется попаданием (hit).

В случае необходимости процессор может записать в слово, находящееся в КЭШ-памяти новые данные.

Основными характеристиками КЭШ-памяти являются:

· ёмкость памяти;

· размер блока;

· способ отображения основной памяти на КЭШ-память;

· алгоритм замещения информации в заполненной КЭШ-памяти;

· алгоритм согласования основной и КЭШ-памяти;

· число уровней КЭШ-памяти.

2.4.5. Энергонезависимое оперативное запоминающее устройство

Энергонезависимая оперативная память (NVRAM) – это память, которая может хранить данные независимо от наличия основного питания компьютера от сети или от штатных аккумуляторов большой ёмкости. От обычных постоянных запоминающих устройств её отличает отсутствие этапа стирания данных при их перезаписи. Существует несколько вариантов построения такой памяти:

· микросхемы BBSRAM – обычные статические ОЗУ с малым энергопотреблением, питающиеся от встроенных малоразмерных литиевых аккумуляторов и имеющие усиленную защиту от искажения информации при включении и отключении питания;

· микросхемы NVRAM – микросхемы, объединяющие в одном корпусе статическое ОЗУ и перепрограммируемую память EEPROM, обменивающиеся данными при включении и отключении питания;

· микросхемы FRAM – ферроэлектрическая память;

Первый вариант энергонезависимого ОЗУ часто используется в современных компьютерах для построения CSMOS-памяти, хранящей основные сведения об оборудовании компьютера и различные настройки системы.

Контрольные вопросы

1. Что такое двоичное кодирование данных и команд?

2. Что предусматривает принцип однородности памяти?

3. Объясните принцип программного управления архитектуры фон Неймана.

4. Что такое принцип адресуемости памяти в архитектуре фон Неймана?

5. Разъясните назначение АЛУ в вычислительной машине фон Неймана.

6. Что такое ЗУ в архитектуре фон Неймана, и каково его назначение?

7. Какой блок в архитектуре фон Неймана управляет всеми процессами (АЛУ, УУ, ЗУ, УВВ) и как он называется?

8. Нарисуйте структурную схему вычислительной машины фон Неймана. Объясните назначение её блоков.

9. Почему вычислительную машину фон Неймана называют машиной с последовательной обработкой данных? По какому признаку структурной схемы можно обнаружить это свойство машины?

10. Что такое регистры в расширенной архитектуре фон Неймана?

11. Что такое кэш-память и в чём заключается принцип её работы?

12. Какие элементы входят в центральный процессор расширенной архитектуры фон Неймана?

13. Что такое основная и вторичная память расширенной архитектуры фон Неймана? Где они размещаются в реальной вычислительной машине?

14. Что такое порты расширенной архитектуры фон Неймана?

15. Какие элементы входят во вторичную память расширенной архитектуры фон Неймана.

16. Каким образом достигается иллюзия многозадачности в вычислительной машине фон Неймана?

17. По какому признаку различаются внешние и внутренние устройства вычислительной машины (персонального компьютера)?

18. Что такое внутренняя память, и из каких элементов она состоит?

19. Какова роль тактового генератора в персональном компьютере?

20. Что представляет собой системная шина компьютера? Какова её роль?

21. Какова роль контроллеров и портов персонального компьютера?

22. Что такое Com-порт персонального компьютера?

23. Что такое LPT-порт персонального компьютера?

24. Каковы особенности USB-порта с точки зрения эксплуатации персонального компьютера?

25. Каким образом присоединяются к системной шине внешние устройства и как они управляются?

26. Что такое ОЗУ персонального компьютера. Каковы разновидности ОЗУ по принципу действия?

27. Что такое ПЗУ персонального компьютера, что оно хранит, каковы его разновидности по способу стирания?

28. Каким образом к системной шине присоединяются накопители на дисках?

29. Что такое CSMOS и какова его роль в персональном компьютере?

30. Нарисуйте и объясните структурные схемы вычислительных систем с общей и распределённой памятью.

31. Объясните, что означают обозначения ОКОД, МКОД, ОКМД, МКМД?

32. Нарисуйте и объясните схему взаимодействия основной и кэш памяти.

3. АРХИТЕКТУРА ВНУТРЕННИХ УСТРОЙСТВ

ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА

3.1. Архитектура процессора

Под архитектурой микропроцессора понимается его программная модель, т.е. программно-видимые устройства. Под микроархитектурой понимается внутренняя реализация этой программной модели. Следует иметь в виду, что различные фирмы могут использовать одну и ту же архитектуру, например,

32-разрядную IA-32, но реализовывать её разными способами.

Как уже говорилось выше, различают следующие типы процессоров:

· CISK (с полным набором команд);

· RISK (с ограниченным набором быстрых команд и реализацией остальных команд через быстрые);

· MISK (быстродействующие процессы с минимальным набором быстрых команд).

Для современных микропроцессоров характерно наличие двух режимов работы: режим реальной адресации и защищённый режим. В режиме реальной адресации процессору доступно около 1Мб памяти. В защищённом режиме доступны 4Гб физической памяти, через которую можно получить доступ к 64Тб виртуальной памяти. Отдельные области памяти объявляются защищёнными от записи. Это сделано для того, чтобы в мультипрограммном режиме программы не влияли друг на друга.

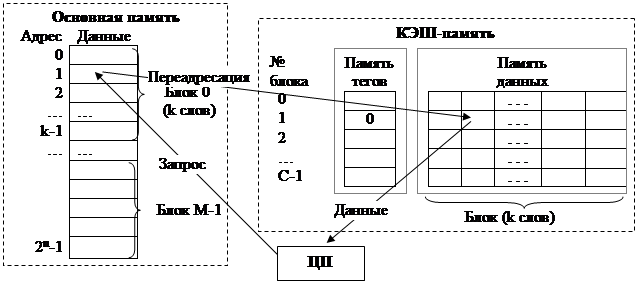

На рис. 3.1 показан один из вариантов структурной схемы микропроцессора фирмы Intel. Все внутренние устройства микропроцессора объединены в единую систему внутренней магистралью, которая присоединяется к системной шине компьютера через специальное устройство – интерфейс системной шины. Толстыми белыми стрелками показаны направления движения информации, тонкими чёрными – линии передачи управляющих сигналов.

Все вычисления ведутся двумя арифметико-логическими устройствами (АЛУ). АЛУ команд обрабатывает команды, АЛУ данных выполняет вычислительные операции над данными. Управляет всеми процессами внутри микропроцессора устройство управления, состоящее из множества блоков. Внутреннюю память процессора образует множество регистров.

Регистром называется несколько ячеек памяти (их число кратно восьми), которые имеют два устойчивых состояния и позволяют выполнять над данными, помещёнными в них такие операции как инкремент и декремент[6], а также арифметический и циклический сдвиг[7] данных на одну позицию. Поскольку количество регистров в процессоре невелико, то их стоимость не имеет значения, и регистры имеют более высокое быстродействие, чем основная память.

Как известно при запуске программы для неё выделяется определённая область памяти, которая делится на отдельные части (сегменты). Примерами сегментов являются сегменты кода программы (CS) и данных (DS). Для работы с данными используются также сегменты ES, FS иGS. Кроме того, для организации временной передачи управления для организации подпрограмм, процедур и функций выделяются специальный сегмент стека (SS) адресов возврата и регистр IP указателя вершины стека адресов возврата. Таким образом, часть регистров микропроцессора выделяется для хранения адресов начала сегментов. Эти сегменты называются регистрами сегментов. Именно через них АЛУ команд общается с внутренней магистралью.

|

Рис. 3.1. Вариант структурной схемы микропроцессора фирмы Intel

Микропроцессор имеет также множество регистров общего назначения. С ними работает АЛУ данных. Из регистров общего назначения регистр SP содержит указатель вершины стека, т.е. адрес данного, которое должно быть записано при следующем обращении к стеку.

Регистр флагов – специальный регистр, биты которого не зависят друг от друга и не могут быть использованы для операций обработки данных Они содержат информацию о состоянии процесса и наступивших событиях.

На рис. 4.1 показаны 16-битовые регистры общего назначения. Каждый из регистров АХ, ВХ, СХ и DX разбивается на старший и младший байты. Названия байтов регистра образуются из названия регистра посредством замены буквы Х буквой L для младшего байта и буквой H – для старшего. В частности, в регистре АХ старший и младший байты называются соответственно AH и AL.

Современные микропроцессоры имеют уже 64-битные регистры, поэтому к их именам слева добавляется буква Е. Например регистр АХ получил название ЕАХ

В процессе работы программы очередная команда выбирается из ОЗУ и через регистр команды поступает в устройство управления. Устройство управления опознаёт команду, распознаёт способ адресации данных, организует вычисления адресов АЛУ команд и управляет работой АЛУ данных и всех остальных устройств. Внутри устройства управления имеется множество различных блоков, часть которых управляют выполнением арифметических операций, а часть повышает производительность системы.

В устройстве управления имеется короткая очередь команд. Это позволяет параллельно с обработкой данных выбирать последующие команды и подготавливать данные к исполнению команд. Вторым способом повышения производительности процессора является конвейеризация. Она предполагает организацию из блоков устройства управления последовательной технологической цепочки. Каждая операция по обработке инструкции выполняется своим элементом конвейера и продвигается по технологической цепочке от начала к концу. Это позволяет запустить на обработку несколько инструкций программы. В процессоре может быть несколько конвейеров. Процессор с одним конвейером называется скалярным.

Устройство управления позволяет реализовать технологию продвижения данных, которая предусматривает возможность начала выполнения инструкции до окончания подготовки всех необходимых данных.

Интересные возможности повышения производительности обеспечивают технологии предсказания переходов и исполнение по предположению. Они обрабатывают ветвящиеся алгоритмы. Первая технология в статическом варианте считает, что одни переходы произойдут, другие – нет, и направляют поток выборки и декодирования инструкций по ветви, которая, по мнению процессора, будет выполняться. В динамическом варианте накапливается статистика осуществления переходов, и предсказание оказывается более точным. В данном случае процессор рискует тем, что при неверном предсказании будут сделаны несколько лишних шагов.

Исполнение по предположению является развитием предсказания переходов и предусматривает не только декодирование инструкций, но и их исполнение, не дожидаясь фактического выполнения перехода.

Для обеспечения лучших возможностей обработки данных в классическую архитектуру микропроцессоров вводятся расширения. Наиболее ранним по времени расширением является введение в микропроцессор математического сопроцессора, выполняющего операции с плавающей точкой и вычисляющий различные математические функции. Для этого в микропроцессор добавлен блок FPU (он же NPX), который содержит стек из восьми 80-битных регистров.

Более поздним расширением является поддержка приложений мультимедиа, т.е. операций с 2D- и 3D-графикой. Эта технология называется ММХ и предусматривает использование младших битов регистров FPU для выполнения операций над целыми комплектами операндов, включающих в себя 1, 2, 4 и 8 операндов. В этой технологии используется арифметика с насыщением, которая игнорирует перенос единиц из самого старшего и самого младшего разряда, теряя эти единицы как ненужные.

В процессорах старше Pentium-III для этой цели используются дополнительные восемь 128-битные регистры, которые позволяют выполнять операции над одним комплектом операндов (скалярные инструкции) и четырьмя комплектами данных (векторные инструкции). Такое расширение называется потоковым расширением SSE.

Технология 3Dnow! расширяют возможности блока ММХ и позволяют использовать операции с упакованными в FP-формат числами с плавающей точкой. При этом задействованными оказываются регистры блока ММХ. Это существенно повышает быстродействие при обработке графики и открывает возможность расширить наборы инструкций ММХ и кэширования, а также ввести новый комплект команд, ориентированных на обработку сигналов.

3.2. Архитектура оперативной памяти [8]

3.2.1. Блочная организация памяти

Несмотря на большие успехи в области разработки и производства сверхбольших интегральных микросхем, в настоящее время отсутствует возможность создания оперативной памяти, имеющей достаточную ёмкость, в виде одной микросхемы. Второй проблемой является обеспечение должной разрядности ячеек памяти, соответствующей разрядности слов вычислительной машины. Поэтому основная память строится на множестве микросхем.

На рис. 3.2 показана схема увеличения разрядности памяти. Интегральные микросхемы ИМС0, ИМС1, …, ИМС7 имеют информационные выходы,

На рис. 3.2 показана схема увеличения разрядности памяти. Интегральные микросхемы ИМС0, ИМС1, …, ИМС7 имеют информационные выходы,

соединённые параллельно и присоединённые к шине данных. Адресные входы А0, А1, …, Аm-1 также соединены параллельно и присоединены к шине адреса. Комбинация импульсов на шине адреса указывает на ячейки микросхем памяти ИМС0, ИМС1, …, ИМС7. Многопроводная линия "Выбор микросхемы" определяет одну из указанных микросхем, с которой производится операция чтения или записи данных. По линии "Чтение/запись" передаётся сигнал "Чтение" (логическая единица) или запись (логический ноль).

Несколько микросхем, обеспечивающих нужную разрядность, называются модулем памяти. Модулем памяти можно назвать и несколько микросхем, и единственную микросхему, имеющую нужную разрядность. Несколько модулей памяти называются банком памяти. Несколько банков памяти называется блоком памяти.

|

Рис. 3.2. Увеличение разрядности памяти

Для блочной памяти, состоящей из банков, имеющих ёмкость В, известно три основных схемы построения адресов (А), состоящих из пары чисел b (номер банка) и w (адрес ячейки памяти внутри банка)[9]:

· блочная (номер банка памяти b определяет старшие разряды памяти);

· циклическая (b = A mod B – остаток от деления A/B, w = A – B•b – результат деления нацело А на В);

· блочно-циклическая (комбинация двух первых).

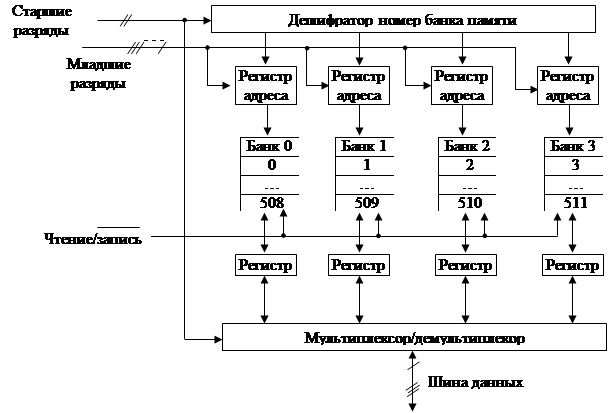

Структура основной памяти с блочным способом построения адресов показана на рис. 3.3. На рисунке показаны 4 банка памяти, содержащие по 128 слов. По двухпроводной линии поступает двухразрядный код номера банка памяти, а по многопроводной – адрес слова в банке. Таким образом, физический адрес (А) слова превращается в пару чисел (b, w). Дешифратор номера блока преобразует двухразрядный двоичный код номера банка в четырёхразрядный параллельный единичный код. В зависимости от команды в выбранную ячейку выбранного банка записываются данные или читаются из неё. Мультплексор/демультиплексор в зависимости от кода номера банка подключает информационные входы/выходы банков памяти к шине данных. Если происходит запись данных, то мультплексор/демультиплексор работает в режиме мультиплексора, а при чтении данных – в режиме демультиплексора.

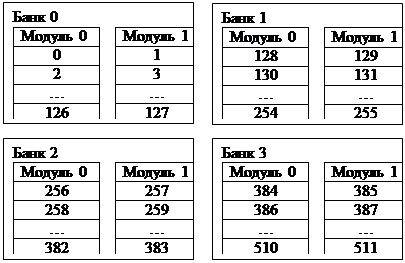

На рис. 3.4 показана структурная схема блочной памяти с чередованием адресов по циклической схеме. От схемы рис. 3.3 эта схема отличается наличием регистров адресов и двунаправленных регистров данных, а также нумерацией слов в банках памяти. Расчёт параметров b и w для первых и последних слов в банках памяти приведена в табл. 4.1. Ёмкость банка равна 128 словам, следовательно, параметр B в вышеприведённых формулах равен 128, поэтому формулы для подсчёта параметров b и w примут вид:

b=A mod 128

w=A–128b

Таблица 3.1. Иллюстрация применения формул расчёта b и w (В=128)

| № слова | Адрес А | b | W | № слова | Адрес А | b | w |

| 00 00000002= 0 | 00 11111112=127 | ||||||

| 01 00000002=128 | 01 1111112=256 | ||||||

| 10 00000002=256 | 10 11111112=767 | ||||||

| 11 00000002=512 | 11 1111112=512 |

|

Рис. 3.3. Структура памяти с блочным способом построения адресов

|

Рис. 3.4. Структура блочной памяти с циклическим способом построения адресов

Блочно-циклический способ образования адресов показан на рис. 3.5. Структурная схема памяти похожа на рис. 3.4, но каждый банк состоит из двух модулей. В каждом блоке адреса слов чередуются циклически, номера банков задаются старшими разрядами адреса.

|

Рис. 3.5. Блочно-циклический способ образования адресов

Циклический и блочно-циклический способы образования адресов также называются расслоением памяти. Этот приём имитирует одновременный доступ к банкам памяти. Это невозможно в пределах одного такта работы памяти. Однако легко организуется для нескольких тактов со сдвигом на один такт. Если обращение к памяти требует слова из разных банков, то время доступа к оперативной памяти сокращается в N раз (где N – число банков памяти).

|

|

|

|

|

Дата добавления: 2015-04-25; Просмотров: 804; Нарушение авторских прав?; Мы поможем в написании вашей работы!