КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Внутрисхемное программирование 2 страница

|

|

|

|

Рисунок 18 – Структура постоянного ЗУ типа 3D с одноразрядной (а) и многоразрядной организациями (б)

Окончание рисунка 18

Рисунок 19 – Структура ЗУ типа 2DM для ROM

На рисунке 20 в более общем виде структура 2DM показана для ЗУ типа RAM с операциями чтения и записи. Из матрицы по-прежнему считывается «длинная» строка.

Рисунок 20 – Структура ЗУ типа 2DM для RAM

Данные в нужный отрезок этой строки записываются (или считываются из нее) управляемыми буферами данных BD, воспринимающими выходные сигналы второго дешифратора DCY и выполняющими не только функции мультиплексирования, но и функции изменения направления передачи данных под воздействием сигнала  .

.

Кэш-память

Кэш-память запоминает копии информации, передаваемой между устройствами (прежде всего между процессором и основной памятью). Она имеет небольшую емкость в сравнении с основной памятью и более высокое быстродействие (реализуется на триггерных элементах памяти).

При чтении данных сначала выполняется обращение к Кэш-памяти (рисунок 21). Если в КЭШе имеется копия данных, адресованной ячейки основной памяти, то КЭШ вырабатывает сигнал Hit (попадание) и выдает данные на общую шину данных. В противном случае сигнал Hit не вырабатывается, и выполняется чтение из основной памяти и одновременное помещение считанных данных в КЭШ.

Рисунок 21 – Структура Кэш-памяти

Эффективность кэширования обуславливается тем, что большинство прикладных программ имеют циклический характер и многократно используют одни и те же данные. Поэтому после первого использования данных из относительно медленной основной памяти повторные обращения требуют меньше времени. К тому же при использовании процессором Кэш-памяти основная память освобождается, и могут выполняться регенерация данных в динамическом ЗУ или использование памяти другими устройствами.

|

|

|

Объем Кэш-памяти много меньше емкости основной памяти, и любая единица информации, помещаемая в КЭШ, должна сопровождаться дополнительными данными (тегом), определяющими копией содержания, какой ячейки основной памяти является эта единица информации.

В полностью ассоциативной Кэш-памяти (FACM, Fully Associated Cache Memory), структура которой показана на рисунке 22, каждая ячейка хранит данные, а в поле «тег» – полный физический адрес информации, копия которой записана. При любых обменах физический адрес запрашиваемой информации сравнивается с полями «тег» всех ячеек, и при совпадении их в любой ячейке устанавливается сигнал Hit.

Рисунок 22 – Структура полностью ассоциативной Кэш-памяти

При чтении и значении сигнала Hit = 1 данные выдаются на шину данных, если же совпадений нет (Hit = 0), то при чтении из основной памяти данные вместе с адресом помещаются в свободную или наиболее давно не используемую ячейку Кэш-памяти.

При записи данные вместе с адресом сначала, как правило, размещаются в Кэш-памяти (в обнаруженную ячейку памяти при Hit = 1 и свободную при Hit = 0). Копирование данных в основную память выполняется под управлением специального контроллера, когда нет обращений к памяти.

Память типа FACM является весьма сложным устройством и используется только при малых емкостях. В то же время этот вид Кэш-памяти обеспечивает наибольшую функциональную гибкость и бесконфликтность адресов, так как любую единицу информации можно загрузить в любую ячейку Кэш-памяти.

Сложность FACM заставляет искать иные структуры Кэш-памяти, более экономичные по затратам аппаратных средств на их реализацию. К числу таких структур относятся Кэш-память с прямым размещением и Кэш-память с наборно-ассоциативной архитектурой (с ассоциацией по нескольким направлениям).

|

|

|

Запоминающие элементы оперативных ЗУ

Статические ОЗУ (SRAM), как правило, имеют структуру 2DM, часть их при небольшой информационной емкости строится по структуре 2D.

Запоминающими элементами (ЗЭ) статических ОЗУ служат триггеры с цепями установки и сброса. В последнее время наиболее интенсивно развиваются статические ОЗУ, выполненные по схемотехнике КМОП, которые имеют сверхмалую потребляемую мощность в режиме хранения, высокую помехоустойчивость, повышенную емкость и высокое быстродействие (быстродействие повышается по мере уменьшения топологических норм технологического процесса).

Рассмотрим принципиальную схему ЗЭ на КМОП-транзисторах, который можно использовать в оперативных ЗУ со словарной организацией (рисунок 23).

ЗЭ на КМОП-транзисторах (рисунок 23) представляет собой RS-триггер на транзисторах VT1…VT4 с ключами выборки на транзисторах VT5 и VT6. При обращении к заданному ЗЭ появляется высокий уровень напряжения на адресной линии, который открывает ключи выборки (адресные ключи) по всей строке накопителя, и выходы триггеров соединяются со столбцовыми разрядными линиями считывания-записи. Через эти линии можно считывать состояние триггера (штриховыми линиями показан дифференциальный усилитель считывания), через них же можно записывать данные в триггер, подавая уровень логического нуля на ту или иную линию.

При подаче нуля на выход D0 снижается стоковое напряжение транзистора VT2, что запирает транзистор VT4 и повышает напряжение его стока. Это открывает транзистор VT2 и фиксирует созданный на его стоке низкий уровень даже после снятия сигнала записи. Триггер установлен в единичное состояние (Q = 1,  = 0). Аналогичным образом нулевым сигналом по линии D1 можно установить триггер в нулевое состояние.

= 0). Аналогичным образом нулевым сигналом по линии D1 можно установить триггер в нулевое состояние.

Рисунок 23 – Принципиальная электрическая схема ЗЭ на КМОП-транзисторах

Статические ОЗУ энергозависимы – при снятии питания информация в триггерных ЗЭ теряется. Можно придать им искусственную энергонезависимость с помощью резервного источника питания. Это наиболее пригодно для ЗУ на элементах КМОП, так как они в режиме хранения потребляют чрезвычайно малую мощность. Для подключения к накопителю ЗУ резервного источника питания рекомендуется схема, приведенная на рисунке 24.

|

|

|

В этой схеме напряжение резервного источника несколько ниже напряжения основного источника UИП. В рабочем режиме накопитель питается от напряжения UИП, при этом диод VD1 проводит, а диод VD2 заперт. При снижении рабочего напряжения к накопителю автоматически подключается источник резервного питания. При этом проводит диод VD2, а диод VD1 запирается, так как при малых значения UИП он попадает под обратное смещение.

Рисунок 24 – Схема подключения резервного источника питания к накопителю ЗУ

Для повышения надежности работы МПС нарушение нормальной работы источника питания обнаруживается контролем напряжения переменного тока.

В динамических ОЗУ (DRAM) данные хранятся в виде зарядов емкостей МОП-структур, и основой ЗЭ является просто конденсатор небольшой емкости. Такой ЗЭ значительно проще триггерного, содержащего 6 транзисторов, что обеспечивает динамическим ОЗУ в 4…5 раз большую емкость.

Известны конденсаторные ЗЭ разной сложности. В последнее время применяют однотранзисторные ЗЭ – лидеры компактности (рисунок 25).

Ключевой транзистор VT отключает запоминающий конденсатор CЗ от линии записи-считывания или подключает его к ней. Сток транзистора VT не имеет внешнего вывода и образует одну из обкладок конденсатора. Другой обкладкой служит подложка. Между обкладками расположен тонкий слой диэлектрика – оксида кремния SiO2.

Рисунок 25 – Принципиальная схема ЗЭ динамического ОЗУ

В режиме хранения ключевой транзистор VT заперт. При выборке данного ЗЭ на затвор подается напряжение, отпирающее транзистор. Запоминающая емкость CЗ через проводящий канал подключается к ЛЗС и в зависимости от заряда различно влияет на потенциал ЛЗС.

При считывании нуля к ЛЗС подключается емкость CЗ, имевшая нулевой заряд. Часть заряда емкости ЛЗС перетекает в емкость CЗ, и напряжения на них уравниваются. Потенциал ЛЗС снижается на величину ∆U, которая и является сигналом, поступающим на усилитель считывания. При считывании единицы, наоборот, часть заряда CЗ стекает в емкость ЛЗС, и потенциал ЛЗС увеличивается на ∆U.

|

|

|

Значение ∆U можно вычислить по формуле

∆U  UИПCЗ/2CЛ, (1)

UИПCЗ/2CЛ, (1)

где CЛ – емкость ЛЗС.

В силу неравенства CЗ << CЛ сигнал ∆U оказывается слабым. Кроме того, считывание является разрушающим, так как подключение запоминающей емкости CЗ к ЛЗС изменяет ее заряд.

Мерами преодоления отмеченных недостатков служат способы увеличения емкости CЗ (без увеличения площади ЗЭ), уменьшения емкости ЛЗС и применения усилителей – регенераторов для считывания данных. Для увеличения емкости CЗ применяют новый диэлектрик (двуокись титана TiO2.), имеющий диэлектрическую постоянную в 20 раз большую, чем SiO2.

Уменьшения емкости ЛЗС можно достичь «разрезанием» этой линии на две половины с включением дифференциального усилителя считывания в разрыв между половинами ЛЗС (рисунок 26, а). Очевидно, что такой прием вдвое уменьшает емкость линий, к которым подключаются запоминающие емкости, т.е. вдвое увеличивает сигнал ∆U.

Усилители-регенераторы строятся на основе триггерных схем. Один из возможных вариантов (рисунок 26, б) основан на введении в

Рисунок 26 – Схема включения усилителя-регенератора в разрыв линии записи-считывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б)

схему дополнительного сигнала «Подготовка» для управления нагрузочными транзисторами VTН1 и VTН2. Вначале сигнал «Подготовка» имеет низкий уровень и нагрузочные транзисторы заперты. В этом состоянии усилитель-регенератор воспринимает слабые сигналы считывания с линий ЛЗС. Одна из половин ЛЗС, к которой не подключается CЗ, сохраняет напряжение предзаряда UИП/2, напряжение на другой половине, к которой подключается выбранный ЗЭ, отклоняется от напряжения предзаряда на ∆U в ту или иную сторону в зависимости от того, считывается единица или ноль. Неравенство напряжений в точках A и B вносит несимметрию проводимостей транзисторов VT1 и VT2. Для считывания и регенерации данных сигнал «Подготовка» переводится на высокий уровень. Транзисторы VTН1 и VTН2 открываются, и возникает схема триггера, находящегося в неустойчивом состоянии, близком к симметричному. Такой триггер в силу своих свойств быстро перейдет в устойчивое состояние, предопределенное начальной несимметрией его режима. На выходах триггера сформируются полные напряжения высокого и низкого уровней. Так как одни и те же точки A и B являются одновременно и входами, и выходами усилителя-регенератора, после своего срабатывания он восстанавливает на емкости CЗ полное значение считанного сигнала. Тем самым автоматически осуществляется регенерация данных в ЗЭ. Состояние триггера определяет также сигналы, выводимые во внешние цепи в качестве считанной информации.

Особенностью динамических ЗУ является мультиплексирование шины адреса. Адрес делится на два полуадреса, один из которых представляет собою адрес строки, а другой – адрес столбца матрицы ЗЭ. Полуадреса подаются на одни и те же выводы корпуса ИС поочередно. Подача адреса строки сопровождается соответствующим стробом RAS (Row Address Strobe), а адреса столбца – стробом CAS (Column Address Strobe). Причиной мультиплексирования адресов служит стремление уменьшить число выводов корпуса ИС и тем самым удешевить ее, а также то обстоятельство, что полуадреса и сигналы RAS и CAS в некоторых режимах и схемах используются различно (например, в режимах регенерации адрес столбца вообще не нужен). Сокращение числа внешних выводов корпуса для динамических ЗУ особенно актуально, так как они имеют максимальную емкость и, следовательно, большую разрядность адресов. Например, ЗУ с организацией 16 M ´ 1 имеет 24-разрядный адрес, а мультиплексирование сократит число адресных линий на 12.

Запоминающие элементы постоянных ЗУ

Программирование постоянной памяти заключается в том или ином размещении элементов связи между горизонтальными и вертикальными линиями матрицы запоминающих элементов. Запоминающие устройства типа ROM имеют многоразрядную организацию (чаще всего 8-разрядную или 4-разрядную, для некоторых ИС 16-разрядную) и обычно выполняются по структуре 2DM. Простейшие ПЗУ могут иметь структуру 2D. Технологии изготовления постоянных ЗУ разнообразны: ТТЛ(Ш), КМОП, n-МОП и др.

В масочных ПЗУ элементом связи могут быть диоды, биполярные транзисторы, МОП-транзисторы и т.д. Например, в матрице диодного ROM(M) (рисунок 27) горизонтальные линии являются линиями выборки слов (адресными линями – АЛ), а вертикальные – линиями считывания (разрядными линиями – РЛ). Считываемое слово определяется расположением диодов в узлах координатной сетки. При наличии диода высокий потенциал выбранной горизонтальной линии передается на соответствующую вертикальную линию, и в данном разряде слова появляется сигнал логической единицы. При отсутствии диода потенциал близок к нулевому, так как вертикальная линия через резистор связана с землей. В изображенной матрице при возбуждении линии выборки АЛ1 считывается слово 11010001 (это слово хранится в ячейке № 1). При возбуждении АЛ2 считывается слово 10101011 (оно хранится в ячейке № 2). Шины выборки являются выходами дешифратора адреса, каждая адресная комбинация возбуждает свой выход дешифратора, что приводит к считыванию слова из адресуемой ячейки.

В матрице с диодными элементами в одних узлах матрицы диоды изготавливаются, в других – нет. При этом, чтобы удешевить производство, при изготовлении ПЗУ стремятся варьировать только один шаблон, так чтобы одни элементы связи были законченными и работоспособными, а другие – незавершенными и как бы отсутствующими. Для матриц с МОП-транзисторами часто в МОП-транзисторах, соответствующих хранению нуля, увеличивают толщину подзатворного окисла, что ведет к увеличению порогового напряжения транзистора. В этом случае рабочие напряжения ПЗУ не в состоянии открыть транзистор. Постоянно закрытое состояние транзистора аналогично его отсутствию.

Рисунок 27 – Матрица диодных запоминающих элементов масочного ПЗУ

ПЗУ с масочным программированием отличаются компактностью запоминающих элементов и, следовательно, высоким уровнем интеграции. При больших объемах производства масочное программирование предпочтительно, однако при недостаточной тиражности ПЗУ затраты на проектирование и изготовление шаблона для их технологического программирования окажутся чрезмерно высокими. Отсюда видна и область применения масочных ПЗУ – хранение стандартной информации, имеющей широкий круг потребителей. В частности, масочные ПЗУ имеют в качестве «прошивки» [1]) коды букв алфавитов (русского и латинского), таблицы типовых функций (синуса, квадратичной функции и др.), стандартное программное обеспечение и т.п.

В ПЗУ типа PROM микросхемы программируются устранением или созданием специальных перемычек. В исходной заготовке имеются (или отсутствуют) все перемычки. После программирования остаются или возникают только необходимые.

Устранение части перемычек свойственно ПЗУ с плавкими перемычками (типа fuse – предохранитель). При этом в исходном состоянии ПЗУ имеет все перемычки, а при программировании часть их ликвидируется путем расплавления импульсами тока достаточно большой амплитуды и длительности.

В ПЗУ с плавкими перемычками эти перемычки включаются в электроды диодов или транзисторов. Перемычки могут быть металлическими (вначале изготавливались из нихрома, позднее из титановольфрамовых и других сплавов) или поликристаллическими (кремниевыми). В исходном состоянии запоминающий элемент хранит логическую единицу, логический нуль нужно записать, расплавляя перемычку.

Второй тип запоминающего элемента PROM – два встречно включенных диода или тонкий диэлектрический слой. В исходном состоянии сопротивление такой цепочки настолько велико, что практически равноценно разомкнутой цепи, и запоминающий элемент хранит логический нуль. Для записи единицы к диодам прикладывают повышенное напряжение, пробивающее диод, смещенный в обратном направлении. Диод пробивается с образованием в нем короткого замыкания и играет роль появившейся проводящей перемычки.

Схемы с тонкими пробиваемыми диэлектрическими перемычками (типа antifuse) наиболее компактны и совершенны. Их применение характерно для программируемых логических СБИС. В номенклатуре продукции стран СНГ ПЗУ с перемычками типа antifuse отсутствуют. Запоминающие элементы с плавкими перемычками и парами диодов показаны на рисунке 28 а, б в исходном состоянии и после программирования.

Плавкие перемычки занимают на кристалле относительно много места, поэтому уровень интеграции ПЗУ с такими перемычками существенно ниже, чем у масочных ПЗУ. В то же время простота программирования пользователем и невысокая стоимость в свое время обусловили широкое распространение ПЗУ типа PROM. Невысокая стоимость программируемых пользователем ПЗУ объясняется тем, что изготовитель выпускает микросхемы без учета их конкретного содержимого, т.е. освобожден от проектирования по специализированным заказам и, следовательно, связанных с этим затрат.

В репрограммируемых ПЗУ (РПЗУ) типов EPROM и EEPROM запоминающими элементами являются транзисторы типов МНОП и ЛИЗМОП (добавление ЛИЗ к обозначению МОП происходит от слов Лавинная Инжекция Заряда).

Рисунок 28 – Запоминающие элементы с плавкими перемычками (а) и диодными парами (б)

МНОП-транзистор отличается от обычного МОП-транзистора двухслойным подзатворным диэлектриком. На поверхности кристалла расположен тонкий слой двуокиси кремния SiO2, далее боле толстый слой нитрида кремния Si3N4 и затем уже затвор (рисунок 29, а). На границе диэлектрических слоев возникают центры захвата заряда. Благодаря туннельному эффекту, носители заряда могут проходить через тонкую пленку окисла толщиной не более 5 нм и скапливаться на границе раздела слоев. Этот заряд и является носителем информации, хранимой МНОП-транзистором. Заряд записывают созданием под затвором напряженности электрического поля, достаточной для возникновения туннельного перехода носителей заряда через тонкий слой SiO2. На границе раздела диэлектрических слоев можно создавать заряд любого знака в зависимости от направленности электрического поля в подзатворной области. Наличие заряда влияет на пороговое напряжение транзистора.

Для МНОП-транзистора с n-каналом отрицательный заряд на границе раздела слоев повышает пороговое напряжение (экранирует воздействие положительного напряжения на затворе, отпирающего транзистор). При этом пороговое напряжение возрастает настолько, что рабочие напряжения на затворе транзистора не в состоянии его открыть (создать в нем проводящий канал). Транзистор, в котором заряд отсутствует или имеет другой знак, легко открывается рабочим значением напряжения. Так осуществляется хранение бита данных в МНОП-транзисторе: отсутствие заряда трактуется как отображение логической единицы, а наличие заряда – логического нуля.

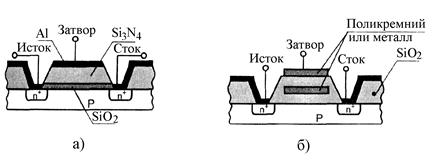

Рисунок 29 – Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б)

При программировании ПЗУ используются относительно высокие напряжения, около 20 В. После снятия высоких напряжений туннельное прохождение носителей заряда через диэлектрик прекращается и заданное транзистору пороговое напряжение остается неизменным.

После 104… 106 перезаписей МНОП-транзистор перестает устойчиво хранить заряд. РПЗУ на МНОП-транзисторах энергонезависимы и могут хранить информацию месяцами, годами и десятками лет. Перед новой записью старая информация стирается записью нулей во все запоминающие элементы.

Транзисторы типа ЛИЗМОП всегда имеют так называемый плавающий затвор, который может быть единственным или вторым, дополнительным к обычному (управляющему) затвору. Транзисторы с одним плавающим затвором используются в ЗУ типа EPROM, а транзисторы с двойным затвором пригодны для применения как в EPROM, так и в EEPROM. Рассмотрим более современный тип – ЛИЗМОП-транзистор с двойным затвором (рисунок 29, б).

Принцип работы ЛИЗМОП с двойным затвором близок к принципу работы МНОП-транзистора – здесь также между управляющим затвором и областью канала помещается область, в которую при программировании можно вводить заряд, влияющий на величину порогового напряжения транзистора. Только область введения заряда представляет собою не границу раздела слоев диэлектрика, а окруженную со всех сторон диэлектриком проводящую область (обычно из поликристаллического кремния), в которую, как в ловушку, можно ввести заряд, способный сохраняться в ней в течение очень длительного времени. Эта область и называется плавающим затвором.

При подаче на управляющий затвор исток и сток импульса положительного напряжения относительно большой амплитуды 20…25 В в обратно смещенных p-n переходах возникает лавинный пробой, область которого насыщается электронами. Часть электронов, имеющих энергию, достаточную для преодоления потенциального барьера диэлектрической области, проникает в плавающий затвор. Снятие высокого программирующего напряжения восстанавливает обычное состояние областей транзистора и запирает электроны в плавающем затворе, где они могут находиться длительное время (в высококачественных приборах многие годы).

Заряженный электронами плавающий затвор увеличивает пороговое напряжение транзистора настолько, что в диапазоне рабочих напряжений проводящий канал в транзисторе не создается. При отсутствии заряда в плавающем затворе транзистор работает в обычном ключевом режиме.

Стирание информации может производиться двумя способами – ультрафиолетовым облучением или электрическими сигналами.

В первом случае корпус ИС имеет специальное прозрачное окошко для облучения кристалла. Двуокись кремния и поликремний прозрачны для ультрафиолетовых лучей. Эти лучи вызывают в областях транзистора фототоки и тепловые токи, что делает области прибора проводящими и позволяет заряду покинуть плавающий затвор. Операция стирания информации этим способом занимает десятки минут, информация стирается сразу во всем кристалле. В схемах с УФ-стиранием число циклов перепрограммирования существенно ограничено, так как под действием ультрафиолетовых лучей свойства материалов постепенно изменяются. Число циклов перезаписи у отечественных ИС равно 10…100.

Электрическое стирание информации осуществляется подачей на управляющие затворы низкого (нулевого) напряжения, а на стоки – высокого напряжения программирования. Электрическое стирание имеет преимущества: можно стирать информацию не со всего кристалла, а выборочно (индивидуально для каждого адреса). Длительность процесса «стирание-запись» значительно меньше, сильно ослабляются ограничения на число циклов перепрограммирования (допускается 104… 106 таких циклов), кроме того, перепрограммировать ПЗУ можно, не извлекая микросхему из устройства, в котором она работает. В то же время схемы с электрическим стиранием занимают больше места на кристалле, в связи с чем уровень их интеграции меньше, а стоимость выше. В последнее время эти недостатки быстро преодолеваются, и электрическое стирание вытесняет УФ-стирание.

Подключение двухзатворных ЛИЗМОП-транзисторов к линиям выборки строк и линиям чтения в матрицах ЗУ показано на рисунке 30. Запись логического нуля осуществляется путем заряда плавающего затвора инжекцией «горячих» электронов в режиме программирования. Стирание информации, под которым понимается удаление заряда из плавающего затвора, приводит к записи во все запоминающие элементы логических единиц, так как в данном случае опрашиваемые транзисторы открываются и передают напряжение UCC на линии считывания.

Подключение двухзатворных ЛИЗМОП-транзисторов к линиям выборки строк и линиям чтения в матрицах ЗУ показано на рисунке 30. Запись логического нуля осуществляется путем заряда плавающего затвора инжекцией «горячих» электронов в режиме программирования. Стирание информации, под которым понимается удаление заряда из плавающего затвора, приводит к записи во все запоминающие элементы логических единиц, так как в данном случае опрашиваемые транзисторы открываются и передают напряжение UCC на линии считывания.

Рисунок 30 – Схема подключения ЛИЗМОП-транзисторов с двойным затвором к линиям выборки и считывания в РПЗУ

Предшественниками двухзатворных ЛИЗМОП-транзисторов были однозатворные, имевшие только плавающий затвор. Эти транзисторы изготовлялись обычно с p-каналом, поэтому введение электронов в плавающий затвор приводило к созданию в транзисторе проводящего канала, а удаление заряда – к исчезновению такого канала. При использовании таких транзисторов запоминающие элементы состоят из двух последовательно включенных транзисторов: ключевого МОП-транзистора обычного типа для выборки адресованного элемента и ЛИЗМОП-транзистора, состояние которого определяет хранимый бит. Стирание информации производится ультрафиолетовыми лучами.

Энергонезависимость всех ROM, сохраняющих информацию при отключении питания, открывает возможности экономии питания при их эксплуатации и, соответственно, улучшения их теплового режима, что повышает надежность схем. Питание можно подавать только на ИС, к которой в данный момент происходит обращение. Режим импульсного питания может многократно уменьшить потребляемую модулем мощность, но одновременно увеличивает время обращения к ЗУ при одиночных произвольных обращениях, так как после включения питания необходимо время для установления режима ИС.

Флэш-память (Flash-Memory) по типу запоминающих элементов и основным принципам работы подобна памяти типа EEPROM, однако ряд архитектурных и структурных особенностей позволяют выделить ее в отдельный класс. В схемах Флэш-памяти не предусмотрено стирание отдельных слов, стирание информации осуществляется либо для всей памяти одновременно, либо для достаточно больших блоков. Понятно, что это позволяет упростить схемы ЗУ, т.е. способствует достижению высокого уровня интеграции и быстродействия при снижении стоимости.

Одновременное стирание всей информации ЗУ реализуется наиболее просто, но имеет тот недостаток, что даже замена одного слова в ЗУ требует стирания и новой записи для всего ЗУ в целом. Для многих применений это неудобно. Поэтому наряду с одновременным стиранием всего содержимого имеются схемы с блочной структурой, в которых весь массив памяти делится на блоки, стираемые независимо друг от друга. Объем таких блоков сильно разнится: от 256 байт до 128 Кбайт и более.

Число циклов репрограммирования для Флэш-памяти хотя и велико, но ограничено, т.е. ячейки при перезаписывании «изнашиваются». Чтобы увеличить долговечность памяти, в ее работе используются специальные алгоритмы, способствующие «разравниванию» числа перезаписей по всем блокам микросхемы. Соответственно областям применения Флэш-память имеет архитектурные и схемотехнические разновидности. Двумя основными направлениями эффективного использования Флэш-памяти являются хранение не очень часто изменяемых данных (обновляемых программ, в частности) и замена памяти на магнитных дисках.

Для первого направления в связи с редким обновлением содержимого параметры циклов стирания и записи не столь существенны, как информационная емкость и скорость считывания информации. Стирание в этих схемах может быть как одновременным для всей памяти, так и блочным. Среди устройств с блочным стиранием выделяют схемы со специализированными блоками (несимметричные блочные структуры). По имени Boot-блоков, в которых информация надежно защищена аппаратными средствами от случайного стирания, эти ЗУ называют Boot Block Flash Memory. Boot-блоки хранят программы инициализации системы, позволяющие ввести ее в рабочее состояние после включения питания.

|

|

|

|

|

Дата добавления: 2015-03-29; Просмотров: 792; Нарушение авторских прав?; Мы поможем в написании вашей работы!