КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Мультиплексор. Схема НЕ на МДП с (не)линейной нагрузкой

|

|

|

|

Схема И-НЕ НА МДП и КМДП

Схема ИЛИ-НЕ на МДП и КМДП

Схема НЕ на КМДП

Схема НЕ на МДП с (не)линейной нагрузкой.

ЭСЛ. Переключатель тока.

Особенность ЭСЛ заключается в том, что схема логического элемента строится на основе интегрального ДУ в ключевом режиме (токовый ключ), выполненный на двух транзисторах, которые могут переключать ток и при этом никогда не входят в режим насыщения.

Особенность ЭСЛ заключается в том, что схема логического элемента строится на основе интегрального ДУ в ключевом режиме (токовый ключ), выполненный на двух транзисторах, которые могут переключать ток и при этом никогда не входят в режим насыщения.

На базу одного из транзисторов, например, VTоп, подано некоторое постоянное опорное напряжение Uоп.  . Изменение напряжения, подаваемого на вход UВХ ниже или выше Uоп, приводит к перераспределению постоянного тока эмиттера Iэ, заданного токостабилизирующим резистором Rэ, между транзисторами VT1 и VTоп. При этом транзисторы не входят в режим насыщения, и, следовательно, в ключе принципиально отсутствует интервал рассасывания их неосновных носителей.

. Изменение напряжения, подаваемого на вход UВХ ниже или выше Uоп, приводит к перераспределению постоянного тока эмиттера Iэ, заданного токостабилизирующим резистором Rэ, между транзисторами VT1 и VTоп. При этом транзисторы не входят в режим насыщения, и, следовательно, в ключе принципиально отсутствует интервал рассасывания их неосновных носителей.

Схема инвертора на МДП. Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой. При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке. При подаче на вход х низкого уровня напряжения VT1 запирается, VT2 близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень напряжения. Выполняется операция

Схема инвертора на МДП. Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой. При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке. При подаче на вход х низкого уровня напряжения VT1 запирается, VT2 близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень напряжения. Выполняется операция  ;

;

При подаче на вход напряжения высокого уровня VT1 открывается, а VT2 закрывается. На выходе устанавливается напряжение низкого уровня. При подаче на вход напряжения низкого уровня VT1 закрыт, а VT2 открыт. Напряжение источника питания через открытый VT2 подается на выход каскада — это напряжение высокого уровня. Т.о., данный ключевой каскад реализует логическую функцию НЕ.

При подаче на вход напряжения высокого уровня VT1 открывается, а VT2 закрывается. На выходе устанавливается напряжение низкого уровня. При подаче на вход напряжения низкого уровня VT1 закрыт, а VT2 открыт. Напряжение источника питания через открытый VT2 подается на выход каскада — это напряжение высокого уровня. Т.о., данный ключевой каскад реализует логическую функцию НЕ.

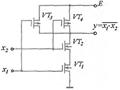

а) МДП, двухвходовой схеме ИЛИ-НЕ входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется операция

а) МДП, двухвходовой схеме ИЛИ-НЕ входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется операция  ;

;

б) КМДП, если на оба входа поданы сигналы низкого уровня, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Таким образом, на выходе установится напряжение высокого уровня (логическая единица). При подаче напряжения высокого уровня хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, т.е. ток через них не течет, а транзистор VT 1 или VT 2 соответственно откроется. На выходе установится напряжение низкого уровня (логический ноль). Видно, что данная схема реализует логическую функцию ИЛИ—НЕ.

б) КМДП, если на оба входа поданы сигналы низкого уровня, то транзисторы VT 3 и VT 4 будут открыты, так как имеют канал с проводимостью р-типа, а транзисторы VT 1 и VT 2 — закрыты, так как имеют канал с проводимостью n -типа. Таким образом, на выходе установится напряжение высокого уровня (логическая единица). При подаче напряжения высокого уровня хотя бы на один из входов соответствующий транзистор VT 3 или VT 4 закроется, т.е. ток через них не течет, а транзистор VT 1 или VT 2 соответственно откроется. На выходе установится напряжение низкого уровня (логический ноль). Видно, что данная схема реализует логическую функцию ИЛИ—НЕ.

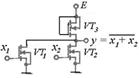

а) МДП, в двухвходовой схеме И-НЕ входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция

а) МДП, в двухвходовой схеме И-НЕ входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция  .

.

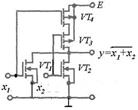

б) Устройство базового элемента И—НЕ как бы обратно устройству элемента ИЛИ—НЕ: параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа (см. рисунок 3.19). Работа данной схемы абсолютно идентична работе элемента ИЛИ—НЕ с тем исключением, что напряжение низкого уровня на выходе устанавливается только при одновременной подаче на оба входа элемента напряжения высокого уровня, а во всех остальных случаях на выходе будет присутствовать напряжение высокого уровня.

б) Устройство базового элемента И—НЕ как бы обратно устройству элемента ИЛИ—НЕ: параллельно соединены транзисторы с каналами р -типа, а последовательно — с каналами п- типа (см. рисунок 3.19). Работа данной схемы абсолютно идентична работе элемента ИЛИ—НЕ с тем исключением, что напряжение низкого уровня на выходе устанавливается только при одновременной подаче на оба входа элемента напряжения высокого уровня, а во всех остальных случаях на выходе будет присутствовать напряжение высокого уровня.

Мультиплексор, многовходовая КЛС с одним выходом, подключает единственную  общую выходную шину к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом. Мультиплексор применяется для преобразования параллельного кода в последовательный, сравнения кодов и т.д.

общую выходную шину к одному из входов в зависимости от управляющего сигнала, заданного двоичным кодом. Мультиплексор применяется для преобразования параллельного кода в последовательный, сравнения кодов и т.д.

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 1569; Нарушение авторских прав?; Мы поможем в написании вашей работы!