КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Исходные данные. 9 страница

|

|

|

|

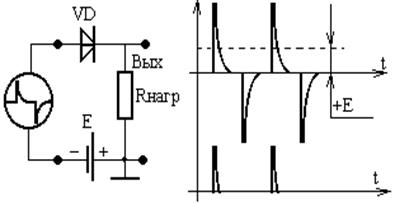

Диодные ограничители.

Ограничителями называют устройства, пропускающие на выход часть входного напряжения, расположенную выше или ниже так называемого уровня ограничения.

Под уровнем ограничения понимается определенное значение напряжения (положительное, отрицательное или нулевое), по отношению к которому ограничитель обладает способностью пропускать импульсы соответствующего знака и амплитуды.

Различают ограничение двухстороннее, снизу и сверху.

Простейшими ограничителями являются диодные ограничители последовательного и параллельного типа.

|

Последовательный ограничитель снизу (см.рис.а) пропускает на выход ту часть входного напряжения, которая способна создать прямой ток в диоде VD (положительный импульс), а параллельный (см.рис.б)- ту часть, при которой диод VD запирается обратным напряжением.

Указанные схемы обеспечивают ограничение напряжения снизу на нулевом уровне, пропуская на выход только импульсы положительной полярности. При импульсах отрицательной полярности на входе выходное напряжение Uвых на выходных зажимах отсутствует, так как в первом случае к диоду приложено обратное напряжение, диод заперт и ток через резистор нагрузки Rнагр не протекает. Во втором случае диод VD шунтирует резистор Rнагр. В обоих случаях не происходит идеального ограничения и при входных отрицательных импульсах на выходе образуются небольшие отрицательные импульсы, что объясняется следующим.

В последовательном ограничителе наличие отрицательного напряжения на входе сопровождается прохождением обратного тока диода и Rнагр, что вызывает некоторое снижение напряжения на величину IобрRнагр на выходе. Эффект ограничения увеличивается с уменьшением обратного тока диода и уменьшением Rнагр.

Однако чрезмерное уменьшение сопротивления недопустимо, так как это увеличивает нагрузку источника Uвх и понижает амплитуду выходного сигнала при положительном импульсе на входе.

В параллельном ограничителе остаточное напряжение на выходе при отрицательном напряжении Uвх будет равно прямому падению напряжения в диоде DUпр и практически не зависит от сопротивления нагрузки. При положительном импульсе на входе часть положительного входного напряжения теряется в резисторе Rогр, предназначенного для защиты диода и источника входного напряжения от чрезмерного тока при отрицательном импульсе на входе.

Во избежание понижения амплитуды выходного напряжения необходимо выполнение условия Rнагр>>Rогр.

Последовательные ограничители применяют при низкоомных нагрузках, а параллельные- при высокоомных.

При необходимости ограничения на уровне, равном нулю, в схему диодного ограничителя вводят источник смещающего напряжения.

|

Схема обеспечивает ограничение на уровне +Е снизу. Источник смещающего напряжения включен встречно по отношению к направлению проводимости диода VD, поэтому на выход проходит только та часть входного напряжения, которая способна создать прямой ток в диоде выше уровня напряжения смещения. Когда диод заперт отрицательным входным напряжением- выходное напряжение равно нулю.

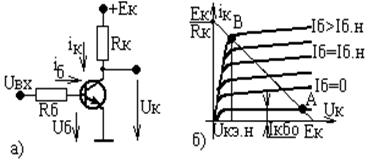

Ключевой режим транзистора.

Отличительной особенностью импульсных схем является широкое применение электронных ключей. Через идеальный разомкнутый ключ не протекает ток. Напряжение на идеальном замкнутом ключе равно нулю.

|

Наиболее широкое применение в качестве электронных ключевых элементов находят транзисторные каскады, в первую очередь каскад с ОЭ. Рассмотрим работу такого каскада в ключевом режиме. При рассмотрении воспользуемся графическим методом расчета транзисторных цепей.

Рисунок 1. Транзисторный ключ: а- простейшая схема,

б- траектория рабочей точки.

На рисунке (б) приведена выходная характеристика транзистора, на которой нанесена нагрузочная линия, пересекающая оси координат в точках: Uк=Ек, при iк=0 и Uк=0, при iк=Ек/Rк.

В ключевом режиме транзистор может находится в двух основных состояниях:

1. Состояние (режим) отсечки ("ключ разомкнут"). При этом через транзистор протекает минимальный ток. Это состояние соответствует точке А на выходной характеристике (рис.1,б), iк=Iкбо»0, напряжение на транзисторе Uк»Ек.

|

Рисунок 2. Схемы замещения транзистора в режимах отсечки (а) и насыщения (б).

Транзистор в режиме отсечки может быть представлен следующей схемой замещения (рис.2,а), содержащей только один источник тока Iкбо, включенный между базой и коллектором.

Для того, чтобы транзисторный ключ находился в разомкнутом состоянии, необходимо выполнить условие отсечки: сменить в обратном направлении эмиттерный переход транзистора или для n- p- n транзистора выполнить условие:

Uб<0. (1)

Мощность, теряемая в режиме отсечки на транзисторном ключе Рк=iкUк мала, так как мал ток.

2. Состояние (режим) насыщения ("ключ замкнут"). Минимальное напряжение на транзисторе Uк=UКЭ,Н»0 соответствует точке В на выходной характеристике (рисю1,б). Ток через транзистор ограничен резистором R и определяется:

Iк,н=(Ек-UКЭ,Н)/Rк»Ек/Rк (2).

В режиме насыщения оба перехода транзистора смещены в прямом направлении, поэтому напряжения между электродами транзистора малы. Транзистор в режиме насыщения представлен схемой замещения (см.рис. 2, б), которая соответствует короткому замыканию между всеми электродами транзистора (говорят, что "транзистор стянут в точку").

Режим насыщения достигается уже при

iБ=IБ,Н=IК,Н/h21Э.

Дальнейшее увеличение тока базы iБ>IБ,Н не изменяет тока в коллекторной цепи. Таким образом, условие насыщения транзистора записывается в виде:

iБ >>IБ,Н=IК,Н/h21Э (3)

где IК,Н»Ек/Rн.

Для надежного насыщения транзистора необходимо, чтобы условие (3) выполнялось при h21Э= h21Эmin. Величина Sн= iБ/IБ,Н>>1 называется коэффициентом насыщения транзистора.

Как и в режиме отсечки, в режиме насыщения мощность, теряемая на транзисторном ключе Рк=iкUк мала, так как мало напряжение. Напряжение UКЭ,Н приводится в справочниках, для создания электронных ключей следует выбирать транзисторы с малым UКЭ,Н<<Ек.

При работе транзисторного ключа переключение из открытого состояния в разомкнутое и обратно происходит скачком, потери мощности при этом, как правило, незначительны. Таким образом, работа транзистора в ключевом режиме характеризуется малыми потерями мощности и высоким КПД, что является важным преимуществом по сравнению с полупроводниковыми устройствами.

ТРИГГЕРЫ.

Триггером называют электронное переключающее устройство, применяемое в автоматике, телемеханике, вычислительной технике для выполнения различных операций, хранения различной информации, отсчета импульсов и т.д.

Триггер обладает двумя устойчивыми состояниями равновесия, которые сохраняются сколь угодно долго до воздействия управляющего импульсного сигнала достаточной амплитуды и длительности. Процесс перехода триггера из одного устойчивого состояния в другое называется переключением, которое сопровождается изменением потенциалов на выходных зажимах триггера.

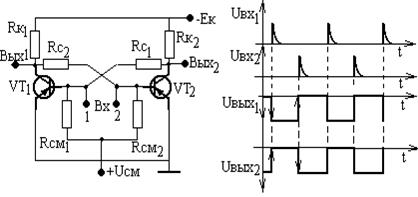

Рассмотрим принцип действия симметричного триггера по схеме, приведенной на рисунке.

|

Триггер состоит из двух усилительных каскадов, собранных по схеме с ОЭ, у которых коллекторы соединены с базами через резисторы Rc1 и Rc2. Коллекторы усилителей одновременно являются выходами триггера. Выходы непосредственно связаны со входами (базами). Триггер с одинаковыми параметрами называется симметричным. Рассмотрим процесс образования устойчивого состояния триггера.

При подаче напряжения Ек оба транзистора частично откроются, т.к. на базах Б1 и Б2 через резисторы RК2RС1 и RК1RС2 подаются одновременно отрицательные потенциалы. Пусть коллекторный ток транзистора VT1 получит хотя бы небольшое приращение по сравнению с коллекторным током транзистора VT2 (это может быть из- за несимметрии схемы ввиду неодинаковости параметров ее элементов). Когда увеличится падение напряжения на RК1 и соответственно повысится потенциал коллектора VT1 (точка К1), которое через резистор связи RС2 передается на базу Б2 транзистора VT2 и он начинает закрываться. Это вызывает уменьшение коллекторного тока и падение потенциала коллектора К2 транзистора VT2, что соответственно передается через резистор связи RС1 на базу Б1 транзистора VT1 и приведет к увеличению тока базы транзистора VT1 и дополнительному росту его коллекторного тока. Развивающийся лавинообразный процесс открытия транзистора VT1 и закрытия транзистора VT2 заканчивается выводом транзистора VT1 в режим насыщения (полного открытия). При полном открытии транзистора VT1, пренебрегая падением напряжения в нем, которое составляет 0,2-0,3 вольта, можно считать, что коллектор К1 находится под нулевым потенциалом (+Ек). Следовательно, на концах цепи: эмиттерный переход транзистора VT2- резистор RС2- коллектор К1 транзистора VT1, будет практически отсутствовать разность потенциалов, исчезнет ток в цепи базы транзистора VT2, и он окончательно закроется.

Для переключения триггера в состояние, противоположное, показанному, надо либо закрыть транзистор VT1, подав положительный импульс в цепь его базы, либо открыть транзистор VT2 отрицательным импульсом, поданным на вход второго транзистора. Длительность и амплитуду управляемого импульса выбирают такими, чтобы они были достаточными для перевода системы через положение неустойчивого равновесия в противоположное состояние, после чего процесс завершится самостоятельно.

Управление триггерами.

Управление триггерами осуществляется короткими управляющими импульсами в промежутках между которыми источник сигналов не должен оказывать активного воздействия на триггерную схему, т.е. не должен изменять естественных потенциалов баз транзисторов. Если на базы транзисторов подавать вместо коротких- длинные управляющие импульсы, то триггер может потерять способность сохранять одно из состояний устойчивого равновесия, в следствии чего управляющие сигналы нельзя подавать непосредственно с выходов других триггерных ячеек или импульсных усилителей. Поэтому часто на входы триггеров ставят так называемые формирователи коротких импульсов, в качестве которых используют дифференцирующие цепи или дифференциальные трансформаторы в сочетании с ограничителями сигналов.

В зависимости от назначения выполняемых операций в каком- либо электрическом устройстве применяют различные способы переключения (запуска) триггеров- раздельно по индивидуальным входам и по общему (счетному) входу.

Рисунок. Пример триггера со счетным входом.

К внутренним входам 1 и 2 присоединены дифференцирующие RC- цепи с диодными ограничителями VD. Внешние S и R соединены между собой и представляют собой общий счетный вход. В исходном состоянии транзистор VT2- открыт, VT1- закрыт. Рассмотрим процесс переключения триггера в противоположное состояние. При подаче прямоугольного управляющего импульсы от генератора сигналов, на фронте этого импульса происходит заряд конденсаторов C1 и С2 дифференцирующих цепей обоих входов. В точках А и В на резисторах R1 и R2 образуются положительные потенциалы. Однако с резисторов через диоды поступают положительные потенциалы на базы не обоих транзисторов, а только на базу одного из них- открытого транзистора. Это объясняется следующим: для правильного изменения состояния триггера положительный управляющий импульс выбирают такой величины, чтобы он всегда был меньше положительного потенциала коллектора открытого транзистора. Поэтому в изображенном на рисунке состоянии триггера потенциал точки К2 открытого транзистора VT2 выше потенциала точки А и тока из точки А в К2 не может быть. Следовательно, не может образоваться и падение напряжения и на резисторе RC1, положительный потенциал с которого подавался бы на запирание закрытого транзистора VT1. Иначе обстоит дело с дифференцирующей цепью R2C2. Между точкой Б, имеющей положительный потенциал, и точкой К1 коллектора закрытого транзистора VT1 с отрицательным потенциалом существует разность потенциалов, под действием которого пройдет ток через резистор RC2. На этом резисторе образуется падение напряжения, положительный потенциал с которого поступает на базу Б2 транзистора VT2 и закрывает его. На коллекторе транзистора VT2 в точке К2 появится отрицательный потенциал, который поступит на базу Б1 транзистора VT1, в результате чего он откроется. После изменения состояния триггера не поступит в точку Б1 положительного потенциала от дифференцирующей цепи R1C1, так как к этому времени закончится зарядка конденсатора С1, прекратится ток через резистор R1 и падения напряжения на нем не будет. Коллекторный ток транзистора VT1 образует падение напряжения на резисторе RК1, в точке К1 будет положительный потенциал, который закроет транзистор VT2. Так закончится процесс переключения триггера.

На срезе управляющего импульса происходит разряд конденсаторов С1 и С2 через генератор управляющих сигналов (подготовка к приему очередного управляющего импульса)в направлении противоположном процессу заряда.

При поступлении на общий вход следующего положительного импульса, аналогично рассмотренному, закроется транзистор VT1 и откроется VT2. Временные диаграммы показывают временные соотношения входных и выходных импульсов. Переключение триггера из одного состояния в другое происходит на фронте положительного прямоугольного импульса, а на срезе этого импульса осуществляется подготовка схемы к приему очередного управляющего импульса. Отрицательный входной импульс не вызывает переключение триггера, и он остается в таком положение, в которое перевел его предыдущий положительный управляющий импульс, до поступления следующего положительного управляющего импульса.

Таким образом, одному периоду выходного импульсы tвых соответствуют два периода входного импульса tвх, поэтому триггер, управляемый по общему входу, выполняет роль делителя частоты.

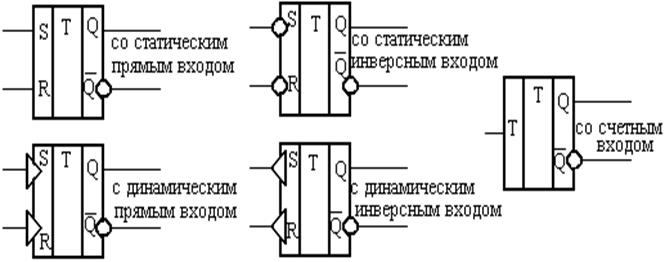

Условные графические обозначения.

В настоящее время имеется большое разнообразие триггеров по схемным исполнениям: триггеры на биполярных и полевых транзисторах, симметричные и не симметричные триггеры, с раздельным и счетным входом и т.д.

Условное графическое обозначение триггера, применяемое в структурных схемах, представляет собой прямоугольник, у которого слева показаны входы, а справа- выходы. Входы: S и R - являются информационными. Обозначение входов происходит от английских слов set- устанавливать и reset- восстанавливать. Триггер с такими входами получил наименование RS- триггера.

Полярность сигналов на входах и выходах, а так же состояние триггера, принято обозначать в двоичной логике. Двоичная логика имеет дело с переменными, которые могут иметь два логических состояния- состояние "логическая1" и состояние "логический 0". В двоичной логике не требуется знание абсолютного значения величины, поэтому физическая величина идентифицируется (обозначается) просто как более положительная- Н, и менее положительная (отрицательная)- L. Эти два значения называются логическими уровнями. Соответственно, между данными понятиями устанавливаются следующие соотношения.

Соглашение положительной логики. Более положительное значение физической величины (логический уровень Н) соответствует состоянию "логическая 1", менее положительное (отрицательное) значение физической величины (логический уровень L) соответствует состоянию "логический 0".

Соглашение отрицательной логики. Менее положительное (отрицательное) значение физической величины (логический уровень L) соответствует состоянию "логическая 1", более положительное значение физической величины (логический уровень Н) соответствует состоянию "логический 0".

Здесь и далее сигналы на входах и выходах триггеров и других электронных устройств приняты в основном по соглашению отрицательной логики: сигнал положительной полярности- "логический 0", сигнал отрицательной полярности- "логическая 1".

Триггер имеет два выхода с противоположной полярностью сигналов. Один из выходов является основным и обозначается Q, другой- инверсным и обозначается  .

.

О состоянии триггера судят по состоянию основного выхода. Если Q=1, то триггер находится в состоянии единицы.

Информационные входы бывают прямыми и инверсными. Входы, с помощью которых выполняется установка триггеров в состояние 1 и 0 при поступлении сигнала 1, называются прямыми соответственно S и R входами. Входы, по которым устанавливают триггер в состояние 1и 0 с помощью сигнала 0, называются инверсными соответственно  и

и  входами. Инверсные входы и статические инверсные входы обозначаются светлыми кружками на сторонах прямоугольника с соответствующими буквенными обозначениями. Верхние выходы Q являются основными, нижние выходы- инверсные

входами. Инверсные входы и статические инверсные входы обозначаются светлыми кружками на сторонах прямоугольника с соответствующими буквенными обозначениями. Верхние выходы Q являются основными, нижние выходы- инверсные  . Динамические прямой и инверсный S и R входы обозначают треугольниками на сторонах прямоугольников: прямой вход- вершиной к условному обозначению, инверсный- вершиной от условного обозначения.

. Динамические прямой и инверсный S и R входы обозначают треугольниками на сторонах прямоугольников: прямой вход- вершиной к условному обозначению, инверсный- вершиной от условного обозначения.

Триггер со счетным входом именуют Т- триггером и обозначают, как показано.

Термин "счетный" означает, что совокупность таких триггеров применяется для счета импульсов.

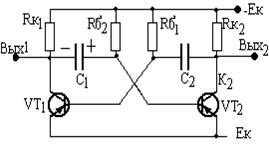

МУЛЬТИВИБРАТОР.

Запуск мультивибратора.

Мультивибратор (GN) представляет собой генератор импульсов, выходное напряжение которого является периодической функцией времени и характеризуется скачкообразными перепадами напряжения. Мультивибраторы применяют в качестве генераторов импульсов заданной периодичности в передающих и приемных узлах телемеханических устройств, в блоках программного автоматического управления и т.п.

|

Как и триггер, мультивибратор состоит из двух усилительных каскадов на транзисторах VT1 и VT2 с нагрузками в коллекторных цепях RК1 и RК2. Отличие мультивибратора от триггера состоит в том, что его коллекторно- базовые связи выполняют емкостями С1 и С2 вместо резисторов, а базы транзисторов присоединены через резисторы RБ1 и RБ2 к отрицательному полюсу источника коллекторного питания - Ек.

При одинаковых параметрах каскадов, когда RК1=RК2 и RБ1 = RБ2 и С1 = С2, мультивибратор называют симметричным. При подаче на схему напряжения питания оба транзистора одновременно открываются, т.к. на их базы поступает отрицательное напряжение смещения. Однако при этом токи в эмиттерно- базовых и коллекторных цепях и зарядные токи конденсаторов С1 и С2 не будут одинаковыми (IБ1¹ IБ2, IК1¹ IК2, IЭ1¹ IЭ2), так как элементы схемы изготовленные в пределах действующих допусков, нарушают абсолютную симметрию мультивибратора. Поэтому, у одного из двух транзисторов токи в цепях будут нарастать быстрее, у другого- медленнее. Допустим, что приращение коллекторного тока транзистора VT1 больше приращения коллекторного тока транзистора VT2 на DiК1. В следствии этого потенциал коллектора транзистора VT2 изменится (точка К2) на величину DiК1RК1. В момент открывания транзисторов конденсаторы С1 и С2 (до этого разряженные) не могут мгновенно зарядится, поэтому под положительными потенциалами коллекторов будут находится обкладки конденсаторов С1 и С2 как соединенные с коллекторами, так и соединенные с базами транзисторов VT1 и VT2, вызывая запирание этих транзисторов. Положительный потенциал коллектора VT1 выше положительного потенциала коллектора транзистора VT2 на величину DiК1RК1, поэтому запирающее действие коллекторного напряжения транзистора VT1 на транзистор VT2 будет сильнее, чем коллекторного напряжения VT2 на транзистор VT1. Это вызывает уменьшение базового и коллекторного тока транзистора VT2 и соответственно понижение потенциала в коллекторе (точка К2), в следствии чего больше возрастет разница коллекторных напряжений в пользу транзистора VT1. При этом условии потенциал базы транзистора VT1 по отношению к заземленному эмиттеру понижается и транзистор VT1 открывается еще больше. Потенциал базы транзистора VT2 по отношению к эмиттеру повышается, что ведет к еще большему закрытию транзистора VT2. Процесс разряда конденсатора С2 и заряда С1 происходит лавинообразно и заканчивается выводом транзистора VT1 в режим насыщения при закрытом транзисторе VT2 и при полностью заряженном конденсаторе С1 и разряженном С2. Однако, в отличие от триггерной схемы это состояние мультивибратора является неустойчивым, т.к. конденсатор С2 разрядится через резистор RБ2, источник напряжения питания Ек и транзистор VT1, то при отсутствии разрядного тока не будет падения напряжения на резисторе RБ2 и не будет посылаться положительного потенциала, запирающего базу Б2 транзистора VT2. На базу транзистора VT2 поступает отрицательное напряжение от -Ек. Транзистор VT2 откроется и его положительный потенциал на коллекторе (точка К2) вызовет разряд конденсатора С1 через резистор, источник напряжения питания Ек и транзистор VT2. Положительный потенциал с резистора RБ1 закроет транзистор VT1. В последующем будет происходить периодическая смена состояний транзисторов и конденсаторов с образованием на выходе 1 и 2 импульсов противоположной полярности: положительный импульс на выходе открытого транзистора, отрицательный- на выходе закрытого транзистора.

Процессы при установившихся колебаниях мультивибратора.

|

|

Пусть в некоторый момент времени t1 открыт транзистор VT1, а до этого был открыт VT2 и конденсатор C2 заряжен до +Ек. Цепь заряда конденсатора С2: (+Ек)-(переход эмиттер- база VT2)-(C2)-(RК1)-(-Ек). Так как падение напряжения на транзисторе в режиме насыщения незначительно (около 0,3 В), то при полностью открытом транзисторе VT1 напряжение на его коллекторе К1 можно принимать равным нулю (UК1»0); перепад напряжения на коллекторе VT1 от (-Ек) до 0 (+Ек) для момента t, показанном на рисунке (д). Так как транзистор VT1 открылся, то на левой обкладке конденсатора С2 зафиксируется положительный потенциал, который вызовет разряд конденсатора С2 током по цепи: (+Ек)-VT1-С2-RБ2-(-Ек). К резистору RБ2 будет приложена сумма двух напряжений- напряжение источника питания и напряжение конденсатора С2. На базе транзистора VT2 (рис.в) образуется скачок напряжения UБ2 от 0 до +Ек, как результат падения напряжения на резисторе RБ2 при прохождении тока iр. В течении времени t1-t3 разряда конденсатора С2 на базу Б2 транзистора VT2 подается положительный потенциал, в следствии чего потенциал базы Б2 выше потенциала эмиттера, транзистор VT2- закрытый и ток в цепи его базы iб2 (рис.г) равен нулю. В это же время происходит заряд конденсатора С1 током iз через открытый транзистор VT1 по цепи: (+Ек)-(эмиттерно- базовый переход транзистора VT1)-С1-RК2- (-Eк). На выходе 2 образуется импульс отрицательной полярности UК2 (рис.д). В интервале времени t1-t3 напряжение на выходе 2 сначала (до полного заряда конденсатора С1) изменяется по экспоненте, а затем становится равным (-Ек). Таким образом в интервале времени t1-t3 на коллекторе открытого транзистора VT1 (выход1) образуется положительный прямоугольный импульс (рис.з), а на коллекторе закрытого транзистора VT2 (выход2) образуется отрицательный импульс, который приблизительно можно принять так же прямоугольным. Ток в цепи базы открытого транзистора VT1 состоит из слагаемых: постоянного в течении рассматриваемого полупериода (t1-t3) тока Iбо=Ек/Rб и изменяющегося по экспоненциальному закону зарядного тока iз конденсатора С1. Ток Iбо протекает по цепи: (+Ек)-(переход эмиттер- база VT1)- RБ1- (-Ек).

В результате разряда конденсатора С2 потенциал базы транзистора VT2 в момент времени t3 станет равным нулю (рис.в). Этого достаточно, чтобы открылся транзистор VT2 и ток в цепи его базы изменился скачком от 0 до Iб мах (рис.г). Это объясняется тем, что конденсатор С2 разряжен полностью, и величина зарядного тока iз ограничена только резистором RК1. Ток в цепи базы VT2, так же, как в цепи базы VT1, имеет две составляющие Iбо и iз в интервале времени t3-t4, а затем от t4 до t5 только Iбо (рис.г). Положительный (нулевой) потенциал на коллекторе открытого транзистора VT2 вызывает разряд конденсатора C1 и скачок напряжения UБ1 от 0 до +Ек на Б1 транзистора VT1 (t3 на рис.е). В результате чего ток базы iб1 (t3-t5) становится равным нулю (рис.ж). Все процессы для второго полупериода аналогичны процессам первого полупериода. Разрядные и зарядные токи, токи базы и коллектора показаны на схеме, следует только отметить, что в интервале времени t3-t5 изменилась полярность сигналов на выходах: положительный на выходе 2 (0), и отрицательный на выходе 1.

Торможение мультивибратора может быть осуществлено подачей положительного напряжения смещения в цепь базы одного из транзисторов или размыканием одной из эмиттерной цепи.

ОДНОВИБРАТОР.

Одновибратор представляет собой генератор, возбуждающийся короткими входными импульсами, при каждо запуске одновибратора генерируется одиночный выходной импульс заданной длительности. Одновибратор состоит из двух инвертеров с перекрестными коллекторно- базовыми связями, из которых одна является резисторной, а вторая- емкостной, при соответственно положительном и отрицательном смещении в базовых цепях транзисторов.

|

|

Благодаря этому в одновибраторе сочетаются свойства триггера и мультивибратора. Иногда одновибратор называют заторможенным мультивибратором. Одновибратор может принимать два устойчивых состояния равновесия, однако, одно из них- длительно устойчиво, а другое- временно устойчиво.

При подаче напряжения на одновибратор немедленно открывается транзистор VT1 и закрывается транзистор VT2. Такое состояние одновибратора, являющееся длительно устойчивым, объясняется следующим. Транзистор VT1 открывается раньше транзистора VT2 потому, что его база связана с (-Ек) через резистор Rб, RК2 и конденсатор С. В цепи базы VT1 протекает два тока: Iбо1 (+Ек,VT1,Rб,-Ек) и iз (+Ек,VT1, С,RК2,-Ек). Зарядный ток конденсатора iз формирует открытие транзистора VT1, так как в момент подачи напряжения он разряжен и сопротивление его близко к нулю, ток iз ограничивается только резистором Rк2<<Rб. Транзистор VT2 остается в закрытом состоянии под действием положительного напряжения смещения и напряжения на коллекторе К1 транзистора VT1, подаваемого на базу Б2 транзистора VT2 через резистор связи Rc. Ток iз прекращается при истечении времени, остальные токи, показанные на рисунке а, остаются постоянными до очередного пуска одновибратора. Пуск одновибратора осуществляется коротким импульсом с нулевым основанием при положительной полярности входного управляющего импульса, его нужно подавать на базу открытого транзистора, а при отрицательной полярности- на базу закрытого транзистора.

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 1460; Нарушение авторских прав?; Мы поможем в написании вашей работы!