КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Режими роботи контролера К580 ВТ 57

|

|

|

|

Структурна схема контролера К580 ВТ 57.

Програмований контролер прямого доступу до пам’яті К 580 ВТ 57.

2.5.1 Загальна характеристика. *

Режим прямого доступу до пам’яті (ПДП) застосовується в МПС для швидкого обміну масивами даних між ОЗП та ЗП. При роботі в цьому режимі МП відключається від МПС і спеціальний пристрій прямого доступу до пам’яті бере на себе функцію керування системними ША і ШУ. Робота такого пристрою синхронізується тактовими сигналами F1 або F2 ГТІ МПС. При обміні масивом даних пристрій, що реалізує ПДП, при кожному зверненні до пам’яті формує необхідні сигнали керування, а сам обмін даними здійснюється шляхом звернення до послідовних чарунок пам’яті МПС. По завершенні передачі масиву даних пристрій ПДП повинен автоматично відмикаєтся від МПС, даючи тим самим МП можливість знову керувати роботою МПС. Запит на початок режиму ПДП подається пристроєм на вхід HOLD МП, а сам процес ПДП починається при наявності одиничного рівня сигналу МП підтвердження захвату HLDA від МП.

У будь-якому пристрої ПДП функціонально можна виділити чотири групи виводів:

- для формування сигналів ШУ МПС та керуючих сигналів для ЗП;

- для формування адресних сигналів ША МПС;

- для підключення пристрою до ШД МПС;

- допоміжні сигнали.

ШД пристрою ПДП безпосередньо в обміні даними не приймає участі, а по ній здійснюється лише програмування мікросхеми.

Програмований контролер ПДП К 580 ВТ 57 являє собою 4-х канальний програмований пристрій, який дозволяє здійснити двонаправлений обмін масивами даних, обсягом до 16 Кбайт, між ОЗП та будь-яким із 4-х ЗП без участі МП. При одночасному надходженні запитів від ЗП програмована логіка контролера дозволяє вибрати найвищий по пріоритету канал ПДП. Початок режиму обміну по каналу ПДП ініціюється подачею сигналу запиту на захват HOLD на відповідний вхід МП. Після отримання контролером сигналу підтвердження захвату HLDA він бере на себе функції керування ШУ та системною ША.

|

|

|

Структурна схема контролера наведена на мал. 2.13 і включає в себе чотири канали ПДП (К0ёК3) кожний з яких складається з двох 16-ти розрядних регістрів: регістра адреси (РА) ПДП та регістра кінця рахунку (РКР).

В процесі виконання програми ініціалізації (або початкового встановлення) до РА повинна бути записана початкова адреса пам’яті, до якої буде звертатися ЗП по каналу ПДП. До молодших 14-ти розрядів (ДФ0ёД13) регістра кінця рахунку (РКР) записується число, на одиницю менше довжини передаваємого масиву даних, тобто N-1, де N – число елементів масиву даних. Старші два розряди РКР (Д14ёД15) використовуються для завдання режиму роботи каналу ПДП. Вміст регістра адреси (РА) автоматично збільшується, а вміст РКР зменшується на одиницю. Таким чином, якщо N – довжина передаваємого масиву, то при передачі N-1 елемента даних по каналу ПДП в РКР буде нуль. Старші два розряди даних РКР в процесі обміну даними не змінюються, а їх вміст змінюється тільки при початковому встановленні контролера, яке здійснюється між циклами обміну даними по каналах ПДП.

Основні входи/виходи контролера мають таке призначення:

DRQ 0ёDRQ 3 – входи запитів на ПДП по відповідному каналу (К0ёК3), коли логічний рівень “1” свідчить про готовність ЗП до обміну даними.

D0ёD7 – двонаправлена ШД, по якій здійснюється обмін інформацією між МП і контролером при запису до останнього слів ініціалізації, читанні вмісту його внутрішніх програмно-доступних регістрів. Крім цього по ШД у циклі ПДП виводяться старші вісім розрядів А15-А8 адреси пам’яті, але в самому обміні даними ШД не приймає участі.

|

|

|

А0ёА3(вх/вих) – молодші розряди двонаправленої ША, які використовуються як входи при запис слів ініціалізації і читанні вмісту внутрішніх регістрів. При роботі в циклі ПДП ними виводяться молодші чотири розряди адреси пам’яті.

А7ёА4 (вих) – однонаправлена ША з трьома станами, по якій виводяться розряди А7ёА4 адреси пам’яті.

(вх/вих) – двонаправлений керуючий вхід/вихід, який використовується як вхід для отримання відповідного сигналу

(вх/вих) – двонаправлений керуючий вхід/вихід, який використовується як вхід для отримання відповідного сигналу  від ШУ МПС при читанні вмісту внутрішніх регістрів контролера.

від ШУ МПС при читанні вмісту внутрішніх регістрів контролера.

Мал. 2.12. Структурна схема контролера ПДП.

де: БШД – буфер шини даних;

Сх. К. Вв/Вив – схема керування вводом/виводом;

ПК і РР – пристрій керування і регістр режиму;

Сх. К.П – схема керування приорітетами.

При роботі в циклі ПДП він служить для видачі сигналу, що дозволяє зчитування даних із ЗП до пам’яті.

(вх/вих) – функціонально подібний до

(вх/вих) – функціонально подібний до  , але призначений для керування записом до внутрішніх регістрів при ініціалізації контролера і передачею даних з пам’яті до ЗП в циклі ПДП.

, але призначений для керування записом до внутрішніх регістрів при ініціалізації контролера і передачею даних з пам’яті до ЗП в циклі ПДП.

,

,  (вих) – виходи, які призначені для формування сигналів керування читанням та записом даних до пам’яті в циклі ПДП відповідно.

(вих) – виходи, які призначені для формування сигналів керування читанням та записом даних до пам’яті в циклі ПДП відповідно.

HRQ(вих), HLDA(вх) – вихідний сигнал запиту на захоплення контролером системних шин і вхід для прийому від МП сигналу дозволу на ці дії відповідно.

DACK 0ёDACK 3 (вих) – вихідні сигнали контролера, які підтверджують вибір того чи іншого ЗП в поточному циклі ПДП.

READY(вх) – керуючий вхід, який використовується для часового узгодження при роботі з повільно працюючим ЗП. Нульовий рівень цього сигналу переводить контролер у стан очікування.

AEN(вих) – сигнал дозволу адреси, по якому всі системні шини МПС відключаються від МП і дозволяється запис старшої півадреси ПДП до зовнішнього буфера адреси (БА). Крім цього цим сигналом відключається схема вибору ЗП.

AD STB(вих) – строб адреси, по якому вісім старших розрядів А15-А7 ПДП записується до БА.

MARK (вих) – сигнал, одиничний рівень якого вказує, що поточний цикл ПДП є 128-м при передачі масиву даних, так званий маркер 128-го циклу.

ТС (вих) – сигнал, одиничний рівень якого вказує ЗП, що поточний цикл обміну ПДП є останнім при передачі масиву даних, так званий кінець рахунку.

CKL (вх) – вхід синхросигналів F2.

|

|

|

(вх) – сигнал вибору контролера, коли логічний рівень “0” формується зовнішнім дешифратором адреси (ДША) по значенню розрядів А4ёА15 ША МПС. Цей вхід автоматично відключається при роботі контролера у циклі ПДП.

(вх) – сигнал вибору контролера, коли логічний рівень “0” формується зовнішнім дешифратором адреси (ДША) по значенню розрядів А4ёА15 ША МПС. Цей вхід автоматично відключається при роботі контролера у циклі ПДП.

RESET(вх) – сигнал початкового встановлення контролера, коли логічний рівень “1” обнуляє всі програмно-доступні регістри, що в свою чергу відключає всі канали ПДП К0ёК3.

При роботі з МП схема керування вводом/виводом (Сх. К. Вв/Вив) контролера дешифрує значення молодших розрядів А3ёА0 адреси і в залежності від сигналів  та

та

забезпечує запис або читання програмно-доступних регістрів мікросхеми. В циклі ж ПДП логіка Сх. К Вв/Вив попарно формує сигнали

забезпечує запис або читання програмно-доступних регістрів мікросхеми. В циклі ж ПДП логіка Сх. К Вв/Вив попарно формує сигнали  ,

,  або

або  ,

,  на відповідних виходах контролера забезпечуючи часове керування процесом обміну даними між ЗП та пам’яттю.

на відповідних виходах контролера забезпечуючи часове керування процесом обміну даними між ЗП та пам’яттю.

Враховуючи те, що старші вісім розрядів адреси А15ёА8 повинні бути записані до зовнішнього буферна адреси (БА), то контролер ВТ-57 належить підключати до МПС разом з будь-яким буферним регістром, наприклад К589 ИР12

Ініціалізація контролера здійснюється записом відповідної інформації до 3-х програмно-доступних регістрів: 16-ти розрядного регістру адреси (РА), 16-ти розрядного регістру кінця рахунку (РКР) і 8-ми розрядного регістру режиму (РР). Спочатку заноситься вміст РА, а сам запис провадиться, починаючи з молодших 8-ми розрядів. Другим записується вміст РКР. Останнім записується вміст РР, формат якого має наступний вигляд (мал. 2.14)

Молодші розряди D0ёD3 визначають передачу даних по відповідному каналу К0ёК3. Розряд D4 встановлює порядок (пріоритети) обслуговування запитів на передачу даних по каналах К0ёК3. Розряд D5 визначає тривалість процесу запису (нормальний або здовжений), коли в останньому завершення обміну даними визначається нульовим рівнем сигналу READY від ЗП.

Мал. 2.14. Формат регістра режиму (РР).

20. Загальна характеристика.

МП К1810 ВМ 86 являє собою однокристальний 16-и розрядний МП з 20-и розрядною адресною шиною і 16-и розрядною ШД, який призначений для роботи як в одно-, так і в багатопроцесорних системах.

|

|

|

Ефективність роботи даного МП суттєво підвищена за рахунок введення до системи команд додаткових, по відношенню до МП ВМ 80, арифметичних операцій множення та ділення 8-и та 16-и розрядних чисел, побітової обробки чисел, команд обробки масивів даних, розширення типів переривань, а також реалізації конвеєрного виконання команд в самому МП. МП такого типу може працювати з пам’яттю до 1Мб, обмінюватися інформацією з 64т. ЗП і має 256 типів різних переривань.

21.Структурна схема МП.

Як відомо, процес виконання програм в МП включає в себе наступні етапи:

1) вибірка коду команди з пам’яті системи;

2) виконання команди та запис результату, якщо це потрібно.

Всі ці етапи в МП виконуються послідовно, що призводить до недостатнього завантаження у часі шин МП. В даному МП процес виконання команд складається з таких же етапів, однак реалізується у 2-х роздільних процесорних блоках, а саме:

1) EU (Exection Unit) – блоці виконання команд;

2) BIU (Bus Interfase Unit) – блоці сполучення з шинами, що дозволяє подати структурну схему МП у наступному вигляд (Мал. 1.1.)

До функцій блоку BIU входять вибірка коду команди та її операндів, запис результатів виконання команд, а блоку EU – виконання команди.

Ці блоки мають наступний функціональний склад і працюють таким чином:

1) Блок виконання команд EU складається з 16-и розрядного арифметично-логічного пристрою (АЛП), регістрів загального призначення (РЗП) і регістрів флагів (F), схеми керування СК1.Він не має зв’язків із зовнішніми (системними) шинами, а коди команд поступають до нього з конвеєра команд (КК), що входить до складу блока BIU. Якщо в результаті дешифрації коду команди з’ясовується, що АЛП необхідно отримати один, або декілька операндів по зовнішнім (системним) шинам, то блок EU звертається до блоку BIU із запитом на отримання необхідних даних, або їх розміщення в пам‘яті.

Незважаючи на те, що всі адреси, з якими оперує блок EU є 16-й розрядні, блок BIU виконує необхідне перетворення адрес так, щоб EU мав можливість звертатися до всього адресного простору МПС, обсягом в 1Мб.

2) Блок сполучення з шинами BIU, що включає в себе блок сегментних регістрів (БСР), суматор адреси (СА), регістр покажчика команд (ІР – Instruction Pointer), буфер адреси/стану (БА/С), буфер адреси/даних (БА/Д), конвеєр команд (КК) та схему керування (СК2) і виконує усі необхідні пересилки даних і кодів для блоку ЕU. В той час, коли блок EU виконує поточну команду, блок BIU отримує код наступної команди з пам‘яті і зберігає її в конвеєрі команд КК, до якого може бути записано шість кодів команд. Це дозволяє блоку BIU видавати до EU команди, що в нього є, по потребі, без завантаження зовнішніх шин МП. Блок BIU організує отримання нового коду команди одразу, як тільки 2 байти з КК будуть передані до EU, а за один цикл запису коду команди до блоку BIU заноситься з ШД два байти команди.

3) Регістри загального призначення, (РЗП) складаються з 8-ми 16-и розрядних регістрів, із яких: АХ – акумулятор; ВХ- регістр бази; СХ- лічильних циклів; ДХ- регістр даних; SP-покажчик стеку; ВР- покажчик бази; SI- індекс джерела даних; DІ- індекс приймача даних. Перші чотири з них (т.т. АХёDХ) використовуються для зберігання даних, як двох байтових, так і однобайтових, т.т. як AL, BL, CL, DL, або AH, BH, CH, та DH, а решта (т.т. SPёDI) – для зберігання адресної інформації.

4) Блок сегментних регістрів (БСР) складаються з кодового (СS), стекового (SS) сегментів, сегменту даних (DS), додаткового сегменту (ES) і призначенні для збереження базових адрес пам‘яті. В даному МП є два типи адреси: фізична і логічна. Перша має 20 розрядів і визначає одну з 1Мб чарунок пам’яті з діапазоном значень від 00000 до FFFFF, а друга ж є 16-ти розрядною і застосовується у конкретній програмі для запису команд без попереднього значення місця у пам’яті, де ці команди будуть розміщенні. Фізична адреса складається з 2-х 16-ти розрядних складових частин: значення бази сегменту та значення зміщення в сегменті. При зверненні блоку BIU до пам’яті відповідна фізична адреса формується за наступним принципом: значення бази сегменту зсувається ліворуч на 4-и розряди, а до отриманого таким чином 20-и розрядного числа з 4-ма нулями в молодших розрядах додається значення зміщення в сегменті (мал.1.2.).

Мал. 1.2. Принцип формування фізичної адреси.

Таким чином, значення бази сегменту з чотирма нулями у молодших розрядах задає в пам’яті сегмент довжиною у 64Кбайт. При цьому кодовий сегмент СS використовується для завдання області розміщення кодів команд; стековий сегмент SS – для розміщення команд роботи зі стеком; сегмент даних DS – для розміщення команд роботи зі стеком; сегмент даних DS – для розміщення постійних або змінних даних в командах. Відповідне зміщення в кодовому сегменті CS для тієї чи іншої команди команди задається відповідним вмістом покажчика команд ІР, в стековій області – вмістом покажчика стеку SP, в області даних – вмістом відповідного індексного регістру SI або DI.

5) Характерною особливосттю МП ВМ 86 є можливість часткової реконфігурації апаратної частини для забезпечення роботи у двох режимах: мінімальному та максимальному.

В першому режимі МП формує усі сигнали керування системними пристроями в однопроцесорній системі, а в другому – сигнали керування формуються системним контролем (СК) на основі кодів, які поступають з МП для функціонування багатопроцесорної системи, коли в ній є додаткові, спеціалізовані процесори, так звані сопроцесори. В максимальному режимі у МП змінюються функції восьми виводів, а сигнали, які формуються при цьому наведені на структурній схемі МП у дужках.

6) Даний МП включає в себе 3-и групи регістрів:

1) РЗП (АХёDX), які використовуються для зберігання проміжних результатів;

2) група покажчиків та індексних регістрів (SPёDI), які призначені для організації розміщення та вибору даних з обраного сегменту пам’яті, коли вміст цих регістрів визначає значення зміщення в сегменті при формуванні фізичної адреси;

3) блок базових або сегментних регістрів (CSёES) включає в себе регістри, що задають початкові (базові) адреси самих сегментів пам’яті.

Крім цього є ще два 16-ти розрядних регістра:

- IP(Instruction Pointer) - покажчик команд, (подібний до РС МП ВМ 80), який вміщує значення зміщення адреси в сегменті поточного коду CS;

- FR(Fead Register) - флаговий регістр, що вміщує в собі дев’ять флагових(Flay) розрядів, які відображають стан АЛП при виконанні ним розрядних команд і керування його роботою.

Формат флагового регістру має наступний вигляд (Мал. 1.3.), і включає в себе:

– молодший піврегістр (молодший байт) FL, що повністю відповідає флаговому регістру МП ВМ 80;

– старший піврегістр (старший байт) FH, який вміщує чотирі додаткові флаги, які відсутні в ВМ 80, а саме:

F(Flag Register)

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| OF | DF | IF | TF | SF | ZF | AF | PF | CF |

|

|

Мал.1.3. Формат флагового регістра FR.

OF (Overflow Flag) - флаг переповнення, який свідчить про втрату старшого біта результату додавання або віднімання у зв‘язку з переповненням розрядної сітки при роботі зі знаковими числами.

DF (Direction flag) - флаг напрямку (або керування напрямком) в строкових операціях. При DF=1 індексні регістри, які приймають участь в строкових операціях, автоматично декрементуються на число байтів операнда, а при DF=0 - інкрементуються, чим забезпечується відповідний порядок обробки ланцюжків, а саме при DF=1- від більших адрес до менших, при DF=0 - навпаки.

IF (Interrupt-enable Flag) - флаг дозволу переривань.

TF(Trap Flag) - флаг трасування (флаг покрокового режиму). При TF=1 МП переходить до покрокового виконання команд.

7) В МП ВМ 86 для скорочення необхідного числа виводів молодші 16-ть адресних ліній (А15-АÆ) мультиплексовані у часі з лініями даних і створюють єдину шину адреси / даних (ШАД). Чотири старші адресні лінії (А19-А16) подібним чином мультиплексовані з лініями стану S6ёS3. Надалі, з метою роздільного використання сигналів вказані шини демультиплексуються, т.т. розділяються за допомогою зовнішніх схем.

8). Призначення виводів МП залежать від його режиму роботи і вісім його виводів мають подвійне позначення. Наведені на структурній схемі МП сигнали мають таке призначення:

AD15ёAD0 (вх/вих) – мультиплексована двонаправлена шина адреси/даних, на якій у першому такті циклу шини (т.т. циклу звернення до пам’яті або ЗП) формується 16-ть розрядів адреси пам’яті (або повна адреса ЗП). Ця адреса повинна бути обов’язково зафіксованою і збереженою на протязі усього циклу для чого використовується зовнішній регістр, куди записується адресна інформація за допомогою строба адреси ALE.

У другій половині циклу шини по лініям AD15ёAD0 передаються дані або байти команди, які супроводжуються стробом DEN.

А19/S6ёA16/S3 (вих) – мультиплексовані вихідні лінії адреси / стану. У першому такті на ці лінії видаються старші чотири розряди адреси пам’яті (А19ёА16), а при адресації до ЗП – нулі. У решті тактів циклу шини МП видає на ці лінії сигнали стану S6ёS3. Коди на лініях S4, S3 визначають сегментний регістр, який приймає участь в формуванні фізичної адреси пам’яті. При зверненні до ЗП, коли сегментні регістри не приймають участі, S4=1, S3=0. Сигнал S5 відповідає флагу IF і коли IF=1 – переривання по входу NMI дозволяється, а при IF=0 – забороняються. Цей сигнал подібний виходу дозволу переривань INTE МП ВМ 80. Сигнал S6 не використовується і дорівнює нулю.

(вих) - дозвіл старшого байту формується в 1-му такті циклу шини одночасно з адресною інформацією. BHE=0 означає, що по старшій половині AD15ёAD8 ШАД передається 8-м бітів і використовується як додатковий, адресний строб для фіксації в зовнішньому регістрі адреси доступу до старшого банку пам’яті.

(вих) - дозвіл старшого байту формується в 1-му такті циклу шини одночасно з адресною інформацією. BHE=0 означає, що по старшій половині AD15ёAD8 ШАД передається 8-м бітів і використовується як додатковий, адресний строб для фіксації в зовнішньому регістрі адреси доступу до старшого банку пам’яті.

ALE(вих) – строб адреси, який видається на початку кожного циклу шини і використовується для запису адреси до регістра адреси, т.т. для демультиплексування ШАД.

DEN(DE) (вих) – строб даних, який свідчить про дозвіл передачі даних і видається у циклах читання і запису.

– використовується для розділу адресного простору пам’яті і вводу/ виводу, коли

– використовується для розділу адресного простору пам’яті і вводу/ виводу, коли  = 1 свідчить про звернення до пам’яті, а

= 1 свідчить про звернення до пам’яті, а  = 0 – до ЗП.

= 0 – до ЗП.

, визначає напрямок передачи по ШАД, коли DT /

, визначає напрямок передачи по ШАД, коли DT /  = 1 свідчить про запис даних з МП до пам’яті або ЗП, а DT /

= 1 свідчить про запис даних з МП до пам’яті або ЗП, а DT /  = 0 – читання даних з пам’яті або ЗП до МП. Даний сигнал призначений для керування формувачами шин і діє на протязі усього циклу шини. Він тотожній сигналам

= 0 – читання даних з пам’яті або ЗП до МП. Даний сигнал призначений для керування формувачами шин і діє на протязі усього циклу шини. Він тотожній сигналам  , але має більшу тривалість.

, але має більшу тривалість.

NMI (вх) – немасковане переривання, яке розпізнається МП по завершенню поточної команди незалежно від значення флагу дозволу переривань IF. Даний вхід призначений для сигналізації про деякі критичні ситуації, наприклад, аварійне відключення живлення.

INTR (вх) – запит переривань (маскований), аналізується МП в кінці виконання кожної команди і якщо переривання дозволені (IF=1), то цей запит фіксується у внутрішньому тригері. Звичайно, що на вихід INTR подається запит від ПКП, і якщо IF=0, то запит по входу INTR ігнорується.

INTA (вих) – підтвердження дозволу на переривання, формується у відповідь на прийнятий запит переривань INTR. На відміну від аналогічного сигналу INTA МП ВМ 80, в даному випадку при підтвердженні переривання видається два сигнали (або так звані цикли), із яких перший є підтверджуючим (інформаційним) про дозвіл переривання, а другий стробує зчитування вектора (покажчика адреси) переривань.

визначає режим роботи МП, коли логічний рівень 1 відповідає мінімальному, а 0 – максимальному режимам, коли при останньому змінюються значення восьми керуючих сигналів.

визначає режим роботи МП, коли логічний рівень 1 відповідає мінімальному, а 0 – максимальному режимам, коли при останньому змінюються значення восьми керуючих сигналів.

використовується разом з командою WAIT, виконуючи яку МП перевіряє рівень сигналу

використовується разом з командою WAIT, виконуючи яку МП перевіряє рівень сигналу  . Якщо

. Якщо  = 0, то МП переходить до виконання наступної по порядку команди, а якщо

= 0, то МП переходить до виконання наступної по порядку команди, а якщо  = 1, то МП видає холості такти Т1 і періодично з інтервалом в 5T перевіряється значення сигналу

= 1, то МП видає холості такти Т1 і періодично з інтервалом в 5T перевіряється значення сигналу  .

.

RESET (вх) – (скидання) переводить МП в початковий стан, коли скидаються усі сегментні регістри (крім CS, усі розряди якого встановлюють в 1), покажчик команд IP, всі флаги, регістри черги команд в конвеєрі команд (КК), всі внутрішні тригери в схемі керування (СК1). Стан РЗП не змінюється і робиться це тільки програмним шляхом. Всі виводи МП, які мають три стани переходять у третій (високо-імпедансний) стан, а ті що мають тільки два стани – до пасивного (неактивного).

В максимальному режимі, в результаті зміни функцій восьми керуючих сигналів, діють такі сигнали:

1).  , які подаються до контролера шини і інформують його про тип виконуємого МП циклу шину. Значення цих сигналів і їм відповідний тип циклу шини подані в табл.1.1. Таблиця 1.1

, які подаються до контролера шини і інформують його про тип виконуємого МП циклу шину. Значення цих сигналів і їм відповідний тип циклу шини подані в табл.1.1. Таблиця 1.1

|

|

| Тип циклу шини |

| Підтвердження переривання. Читання ЗП. Запис до ЗП. Зупинка. Вибірка команди. Читання памўяті. Запис до памўяті. Циклу шини не має. |

Сигнал S2 подібен сигналу М /  , а S1 – сигналу DT /

, а S1 – сигналу DT /  .

.

2). QS1ёQS0 (вих) (стан черги) характеризує стан внутрішньої шести байтової черги команд МП згідно з табл.1.2. Таблиця 1.2.

| QS1 | QS2 | Операції над чергою в КК |

| Операцій немає. В останньому такті не було вибірки з черги. З конвеєру вибраний перший байт команди. Черга пуста. КК очищений командою передачі керування. З черги вибраний наступний байт команди. |

3).  . Дві одинакові двонаправлені лінії, які використовуються для передачі імпульсних сигналів запиту / дозволу доступу до локальної шини при роботі сопроцесорів. Ці лінії незалежні одна від одної, однак

. Дві одинакові двонаправлені лінії, які використовуються для передачі імпульсних сигналів запиту / дозволу доступу до локальної шини при роботі сопроцесорів. Ці лінії незалежні одна від одної, однак  має більш високий пріоритет ніж

має більш високий пріоритет ніж  при одночасній появі запитів. Ці лінії подібні парі ліній HOLD та HLDA, які застосовуються у мінімальному режимі.

при одночасній появі запитів. Ці лінії подібні парі ліній HOLD та HLDA, які застосовуються у мінімальному режимі.

4).  , який інформує усі пристрої МПС, що доступ до системної шини заблокований на час виконання команди по однобайтовому префіксу LOCK.

, який інформує усі пристрої МПС, що доступ до системної шини заблокований на час виконання команди по однобайтовому префіксу LOCK.

26. Загальна характеристика мікроконтролерів (МК)

МК – це відповідні комп’ютерні системи, які містять в собі процесор, пам'ять, пристрої вводу/виводу даних та інші допоміжні схеми та пристрої, що розміщені в одному корпусі (на одному кристалі).

Використання однокристалевих вбудованих МК (Embedded Control Products) дозволяє:

1. суттєво підвищити їх техніко-економічні властивості;

2. знизити витрати та скоротити терміни розробки і виготовлення мікропроцесорних виробів;

3. полегшити модифікацію та зсунути строки їх морального старіння.

Основні типи МК:

· 8-розрядні МК, що займають 48% обсягу ринку мікропроцесорів;

· 16-, 32-розрядні – 24%;

· цифрові сигнальні процесори DSP (Discrete Signal Processors), які обробляють аналогові сигнали в реальному часі – 28%.

Поняття «архітектури» родини МК трактується як сукупність внутрішніх і зовнішніх програмно доступних ресурсів, системи команд, системи переривань, функції вводу/виводу та протоколу обміну по магістралі. Архітектура родини реалізується виробником у вигляді набору зв’язаних між собою функціонально-топологічних модулів, а кожен МК родини подається як певна комбінація цих модулів, основою якої є операційне ядро (CORE).

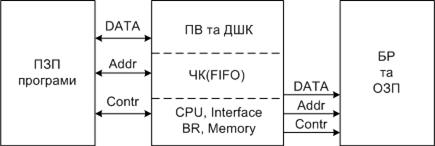

Основна особливість архітектури однокристалевих МК – використання гарвардського принципу організації обчислювального середовища, який припускає наявність розділеної пам’яті програм і даних, що умовно можна подати у такому вигляді (Рис.1).

ПВ – пристрій вибірки

ДШК – дешифратор команд

ЧК – черга команд

БР/BR – блок регістрів

Memory – пам'ять

Рис. 1. Розділення пам’яті програм і даних

Перевагою гарвардського принципу є наступне:

1) завдяки розподілу пам’яті вдається об’єднати виконання поточної команди із вибіркою наступної, що заощаджує час і щільніше завантажує шини;

2) усі команди реалізуються за однакову кількість тактів;

3) спрощується реалізація пристрою (блоку) вибірки команд.

Типовий МК будь-якого покоління включає в себе такі блоки:

1. ЦПЕ – центральний процесорний елемент(далі просто ЦП);

2. генератор тактових імпульсів (ГТІ) і схема початкового запуску (Reset);

3. базова (резидентна) пам'ять даних (РПД/RDM) – тип пристрою ОЗП (RAM);

4. базова (резидентна) пам'ять програм (РПП/RPM) – тип пристрою ПЗП (ROM);

5. засоби вводу/виводу(I/O Ports);

6. таймери (Timers) – фізичні пристрої відліку часу.

Більш складні контролери мають:

1. система пріоритетних переривань (СПП);

2. аналоговий ввід/вивід (аналого-цифрове (АЦ), цифро-аналогове (ЦА) перетворення);

3. послідовний ввід/вивід(синхронний/асинхронний) – RS-232C, USB;

4. вбудований монітор-відладчик програм;

5. внутрішні засоби програмування пам’яті.

Існують основні два класи МК відносно виду пам’яті:

– МК з вбудованою (резидентн) програмною пам’яттю – on-board ROM;

– МК, які не мають програмної пам’яті на кристалі – ROM-less/CPU only.

Intel створила цілу низку МК, основні серед яких наступні:

1. MCS-48 – родина 8-розрядних МК(1974-1977рр.)

2. MCS-51 – родина 8-розрядних МК(1980р.)

3. MCS-96 – родина 16-розрядних МК(1983р.)

4. MCS-251 – родина 16-розрядних МК(1985р.)

5. Intel 9060 family – 32-розрядні (1991р.)

Найбільш поширеними і широко використованими є моделі MCS-51, контролери випускаються більш ніж 20-ма фірмами(Phillips, Intel, Atmel, Dallas, Silicon System, Oki). Існує більш ніж 200 модифікацій МК родини MCS-51.

Базовий МК родини MCS-51(i8051) має наступні параметри:

1) розрядність АЛП – 8 біт;

2) булевий процесор (однобітові операції);

3) резидентна пам'ять програм – 4 кб;

4) резидентна пам'ять даних – 128 б;

5) 21 регістр спеціальних функцій(SFR);

6) 36 ліній вводу/виводу:

– 4 паралельні порти (P0, P1, P2, P3);

– дуплексний послідовний порт

– 4 тестованих входи;(INT0, INT1, T0, T1);

T0 – таймер 0;T1 – таймер 1;

7) лінії вводу: дві 16-розрядні лінії – TC0, TC1;

8) канал послідовного синхронного/асинхронного вводу/виводу – USART;

9) розширення пам’яті програм – до 64 кб;

10) додаткова зовнішня пам'ять даних – до 64 кб;

11) тактова частота осцилятора FOSC – до 12 МГц.

Вказані пристрої і характеристики формують так зване ядро CORE-51 Intel родини MCS-51.

|

|

|

|

|

Дата добавления: 2015-05-08; Просмотров: 912; Нарушение авторских прав?; Мы поможем в написании вашей работы!