КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Типовые логические элементы дтл, ттл, ЭСЛ, иил, кмоптл

|

|

|

|

Схемы смещения уровня и Дарлингтона в аналоговых микросхемах.

Отражатель тока в аналоговых интегральных микросхемах.

Операционный усилитель как универсальная аналоговая микросхема (структура, функции).

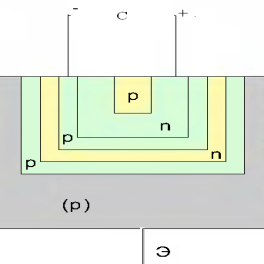

Полупроводниковые интегральные микросхемы.

Основой полупроводниковой ИМС является подложка из кремния обычно p - типа проводимости. В основе изготовления полупроводниковых ИМС лежит диффузионно-планарная или эпитаксиально-планарная технология. Оба этих метода предусматривают создание внутри полупроводника (т. е. в подложке) островок с чередующимися слоями p - и n - типа проводимости.

Rmax=20 кОм. Для повышения номинала внедряют примеси методом диффузии. Cmax=10…100 пФ. Индуктивность в полупроводниковой структуре изготовить нельзя.

Операционным усилителем назыв. Устр-во,предн для выполнения математ.операций с аналоговыми сигналами, имеющее исключительно высокий коэф. усиления,очень большое вход-е и малое выходное сопрот-е и выполненное в микроэлектронном исполнении.

Операц. усилитель включает в свой состав 1 или несколько дифференциальных каскадов УПТ, генератор стабильного тока для питания этих каскадов и выходные эмиттерные повторители для увеличения входного и уменьшения выходного сопротивления.

Пример маркировки ОУ: К553УД2.

Пример маркировки ОУ: К553УД2.

Вход A – инвертирующий вход.

Вход B – неинвертирующий вход.

Входы C – для подключения двуполярного ИП.

Входы D – выводы для подключения цепей коррекции.

ОУ подразделяются по следующим признакам:

1. ОУ общего применения

2. Мощные ОУ

3. ОУ с управляемыми параметрами

4. Быстродействующие ОУ

К основным параметрам ОУ относятся следующие:

1.  Напряжение ИП

Напряжение ИП

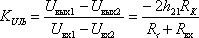

2. Коэффициент усиления

|

|

|

3. Входное сопротивление

4. Потребляемый от ИП ток или потребляемая мощность

5.  Коэффициент ослабления синфазного сигнала [дБ]

Коэффициент ослабления синфазного сигнала [дБ]

6. Скорость нарастания вых. напряжения. Она показывает быстродействие ОУ СИ[В/мкс].

Т.кОУ имеет очень большой коэфф. усиления и сложную схему, то при работе на опред частотах возможно появление нежелательных фазовых сдвигов,приводящих к образованию положительных ОС и, как следствие, к самовозбуждению усилителя.Для устранения этих возможностей применяются цепи коррекции, представляющие различные RC-цепочки.Цепи коррекции могут быть как внешними, то есть при помощи навесных элементов, так и внутренними, то есть внутри корпуса микросхемы. Причём цепи коррекции разрабатываются на этапе проектирования ОУ и являются индивидуальными для каждого конкретного типа ОУ.

На основе ОУ собирают схемы сумматора, интегратора, дифференциатора и др.

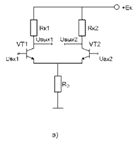

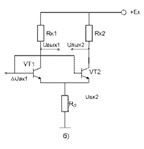

30. Дифференциальный усилительный каскад как составной элемент аналоговой микросхемы.

| Рис.1 а) базовая схема, б) схема при подаче синфазного сигнала. |

Предположим, что каскад абсолютно симметричен, т.е. сопротивления резисторов, входящих в каждое плечо и параметры транзисторов VT1 и VT2 одинаковы. В этом случае при равных входных сигналах Uвх1 и Uвх2 токи транзисторов VT1 и VT2 равны между собой, а именно IК1=IК2, IЭ1=IЭ2, IБ1=IБ2. Пусть входные напряжения получат одинаковые приращения разных полярностей 0,5∆Uвх:

|

|

|

В результате ток одного транзистора увеличится на ∆Iк, а другого на столько же уменьшится:

В результате ток одного транзистора увеличится на ∆Iк, а другого на столько же уменьшится:

При этом результирующий ток через резистор Rэ останется без изменения. Постоянным будет и падение напряжения на нем Изменения коллекторных токов вызывают изменение напряжений на коллекторах транзисторов. Напряжение Uк1=Eп1 – Iк1Rк уменьшается, что вызывает приращение - DUк1, Напряжение Uк2=Eп1-Iк2Rк возрастает, что создает соответственное приращение напряжения DUк2.

Сигнал, снимаемый с обоих коллекторов, называют дифференциальным и он будет равен:

Если входное напряжение изменить только на одном входе на ∆Uвх, т.е.  , это приведет к изменению тока через соответствующий транзистор. Но увеличение падения напряжения на Rэ приведет к уменьшению разности потенциалов между базой и эмиттером транзистора VT2 и ток его уменьшится, причем изменение тока транзистора VT2 будет таково, что приращения напряжений эмиттер-база обоих транзисторов будут одинаковы. Следовательно при увеличении Uвх1 на ∆Uвх потенциал эмиттера увеличится на ∆Uвх/2, что эквивалентно увеличению тока через резистор Rэ на ∆Iк. При этом приращение напряжения база-эмиттер для VT1 равно ∆Uвх/2, а для транзистора VT2 – ∆Uвх/2. Ток каждого плеча изменится на ∆Iк. Очевидно, что независимо от того как на вход каскада подаются напряжения, токи транзисторов меняются одинаково.

, это приведет к изменению тока через соответствующий транзистор. Но увеличение падения напряжения на Rэ приведет к уменьшению разности потенциалов между базой и эмиттером транзистора VT2 и ток его уменьшится, причем изменение тока транзистора VT2 будет таково, что приращения напряжений эмиттер-база обоих транзисторов будут одинаковы. Следовательно при увеличении Uвх1 на ∆Uвх потенциал эмиттера увеличится на ∆Uвх/2, что эквивалентно увеличению тока через резистор Rэ на ∆Iк. При этом приращение напряжения база-эмиттер для VT1 равно ∆Uвх/2, а для транзистора VT2 – ∆Uвх/2. Ток каждого плеча изменится на ∆Iк. Очевидно, что независимо от того как на вход каскада подаются напряжения, токи транзисторов меняются одинаково.

Коэффициент усиления дифференциального каскада при холостом ходе (Rн=¥) определяется как отношение разности выходных напряжений к разности входных:

Коэффициент усиления дифференциального каскада при холостом ходе (Rн=¥) определяется как отношение разности выходных напряжений к разности входных:

Коэффициент усиления дифференциального каскада равен коэффициенту усиления каскада с ОЭ, идентичному одному плечу дифференциального каскада.

Выходное сопротивление каскада, если пренебречь сопротивлением коллекторного перехода в 2 раза выше чем у соответствующего каскада с ОЭ: Rвых≈2Rк.

Значения коэфф-та ослабления синфазного сигнала могут достигать несколько тысяч.

Дифференциальные усилительные каскады широко применяют для построения усилителей постоянного тока и логических элементов.

Токовое зеркало — генератор тока, управляемый током. Чаще всего выходной ток равен управляющему или отличается от него в целое число раз.

Токовое зеркало — генератор тока, управляемый током. Чаще всего выходной ток равен управляющему или отличается от него в целое число раз.

|

|

|

Токовые зеркала на транзисторах чрезвычайно широко используются в аналоговых интегральных схемах благодаря своей простоте (требуются всего два согласованных транзистора) и эффективности. Токовые зеркала обычно используются для того, чтобы «скопировать» один управляющий ток на множество каскадов, и тем самым задать их ток покоя.

33. Логические операции: конъюнкция, дизъюнкция, инверсия, реализуемые в цифровых интегральных микросхемах.

1. Конъюнкция, или логическое умножение. Элемент, реализующий функцию конъюнкции, называется И.

Элементы НЕ, ИЛИ, И представляют собой функционально полный набор логических элементов. Только при помощи этих элементов можно выполнить любую сколь угодно сложную функцию.

Элементы НЕ, ИЛИ, И представляют собой функционально полный набор логических элементов. Только при помощи этих элементов можно выполнить любую сколь угодно сложную функцию.

Схема И. Элементы И-НЕ и ИЛИ-НЕ реализуются подключением на выход диодной

матрицы транзисторного инвертора (Рис 171). R >> Rпр.

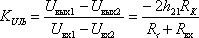

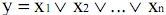

2. Вторая наша логическая функция называется дизъюнкцией, или логическим сложением.

2. Вторая наша логическая функция называется дизъюнкцией, или логическим сложением.

Элемент, реализующий функцию дизъюнкции, называется ИЛИ.

Элемент, реализующий функцию дизъюнкции, называется ИЛИ.

В простейшем случае реализуется на полупроводниковых диодах (рисунок 169). Необходимым условием для работы является:

В простейшем случае реализуется на полупроводниковых диодах (рисунок 169). Необходимым условием для работы является:

1) Uвх1 > Uип; 2) R >>Ri.пр.

1) Uвх1 > Uип; 2) R >>Ri.пр.

3. Логическое отрицание (или инверсия). Записывается эта функция так  . Данная функция реализуется логическим элементом, который называется инвертором или же элементом НЕ (рис. 153).

. Данная функция реализуется логическим элементом, который называется инвертором или же элементом НЕ (рис. 153).

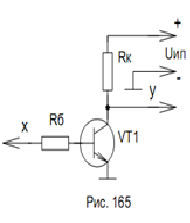

Элемент НЕ (рис 166 - 168). В общем случае представляет транзисторный ключ на полевом или биполярном транзисторе.

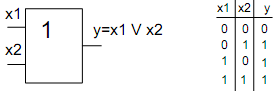

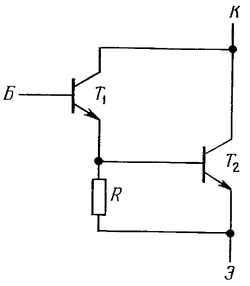

| Составной транзистор Дарлингтона |

|

|

|

В транзисторе Дарлингтона падение напряжения между базой и эмиттером в два раза больше обычного, а напряжение насыщения равно по крайней мере падению напряжения на диоде (так как потенциал эмиттера транзистора Т1 должен превышать потенциал эмиттера транзистора Т2, на величину падения напряжения на диоде). Кроме того, соединенные таким образом транзисторы ведут себя как один транзистор с достаточно малым быстродействием, так как транзистор T1 не может быстро выключить транзистор Т2. С учетом этого свойства обычно между базой и эмиттером транзистора Т2 включают резистор (рис. 2.61). Резистор R предотвращает смешение транзистора Т2 в область проводимости за счет токов утечки транзисторов Т1 и Т2. Сопротивление резистора выбирают так, чтобы токи утечки (измеряемые в наноамперах для малосигнальных транзисторов и в сотнях микроампер для мощных транзисторов) создавали на нем падение напряжения, не превышающее падения напряжения на диоде, и вместе с тем чтобы через него протекал ток. малый по сравнению с базовым током транзистора Т2. Обычно сопротивление R составляет несколько сотен ом в мощном транзисторе Дарлингтона и несколько тысяч ом в малосигнальном транзисторе Дарлингтона.

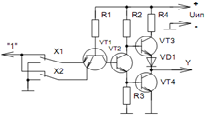

ТТЛ со сложным инвертором.

| Повышение скорости выключения в составном транзисторе Дарлингтона |

Если хотя бы на одном из входов будет действовать логический ноль, соответствующий эмиттерный переход будет открыт, и через него будет протекать ток по цепи от плюса ИП, через R1, база-эмиттер VT1, общий провод, минус ИП. В цепи коллектора VT1, а следовательно, и в цепи базы VT2 ток будет отсутствовать, VT2 будет находиться в режиме отсечки, ток через транзистор VT2, а значит, ток базы VT4 будут близки к нулю. Транзистор VT4 также будет находиться в режиме отсечки, и на выходе будет высокий уровень напряжения логической единицы. При этом напряжение на коллекторе VT2 и на базе VT3, будет максимальным, и VT3 будет находиться в полностью открытом состоянии. При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, переход база-коллектор VT1 на базу VT2. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы VT4 будет максимальным, и транзистор VT4 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе VT3 будет близко к нулю и VT3 перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT3.

Если хотя бы на одном из входов будет действовать логический ноль, соответствующий эмиттерный переход будет открыт, и через него будет протекать ток по цепи от плюса ИП, через R1, база-эмиттер VT1, общий провод, минус ИП. В цепи коллектора VT1, а следовательно, и в цепи базы VT2 ток будет отсутствовать, VT2 будет находиться в режиме отсечки, ток через транзистор VT2, а значит, ток базы VT4 будут близки к нулю. Транзистор VT4 также будет находиться в режиме отсечки, и на выходе будет высокий уровень напряжения логической единицы. При этом напряжение на коллекторе VT2 и на базе VT3, будет максимальным, и VT3 будет находиться в полностью открытом состоянии. При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, переход база-коллектор VT1 на базу VT2. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы VT4 будет максимальным, и транзистор VT4 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе VT3 будет близко к нулю и VT3 перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT3.

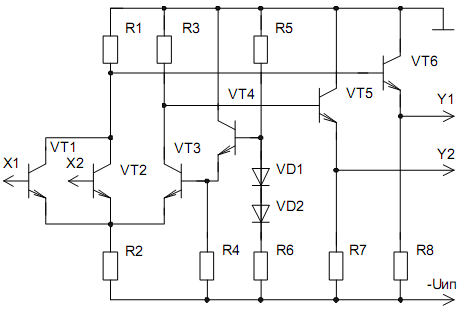

Базовый элемент ЭСЛ серии К500.

Базовый элемент ЭСЛ серии К500.

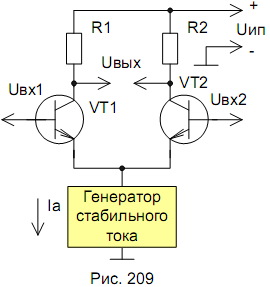

ЭСЛ является самой быстродействующей из всех типов логики. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения или отсечки. Основой ЭСЛ является дифференциальный эмиттерный каскад, изображённый на рисунке 209.

Особенность ЭСЛ: разница уровней логической единицы и нуля очень мала, следовательно, помехоустойчивость плохая. Чтобы повысить помехоустойчивость, в ЭСЛ используется схема, при которой в цепи коллектора – соединение с общим проводом, а в цепь эмиттера подаётся минус напряжения ИП. Это приводит к тому, что все уровни напряжения отрицательны и ЭСЛ плохо согласуются с другими типами логики. Для увеличения коэффициента разветвления по выходу на выходе схемы включают эмиттерные повторители.

|

|

|

|

|

Дата добавления: 2015-06-04; Просмотров: 2764; Нарушение авторских прав?; Мы поможем в написании вашей работы!