КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Асинхронні лічильники

|

|

|

|

В асинхронних лічильниках відсутня загальна для всіх розрядів синхронізація і перехід розрядів у нові стани відбувається послідовно розряд за розрядом, починаючи від вхідного, на який надходять рахункові імпульси. У цих лічильниках кожен наступний тригер (і + 1) розряду запускається від інформаційних виходів  попереднього тригера 7-го розряду. Якщо розглянути послідовність станів, наприклад, четирьохразрядного підсумовуючого двійкового лічильника (табл. 6. 1), то ознакою зміни станів кожного з розрядів лічильника є переключення попереднього розряду зі стану "1" у "ПРО". Саме так поводяться двоступінчасті тригери. Таким чином, послідовний лічильник, що працює згідно табл. 6. 1, можна виконати у виді ланцюжка Т-тригерів, для кожного з яких рахунковий імпульс формується тригером сусіднього молодшого розряду.

попереднього тригера 7-го розряду. Якщо розглянути послідовність станів, наприклад, четирьохразрядного підсумовуючого двійкового лічильника (табл. 6. 1), то ознакою зміни станів кожного з розрядів лічильника є переключення попереднього розряду зі стану "1" у "ПРО". Саме так поводяться двоступінчасті тригери. Таким чином, послідовний лічильник, що працює згідно табл. 6. 1, можна виконати у виді ланцюжка Т-тригерів, для кожного з яких рахунковий імпульс формується тригером сусіднього молодшого розряду.

Таблиця 6.1

| Хсч | Q4 | Q3 | Q2 | Q1 | Хсч | Q4 | Q3 | Q2 | Q1 |

Схема асинхронного підсумовуючого трьохрозрядного лічильника на двоступінчастих Т-тригерах з послідовним переносом приведена на мал. 6.2,а, а тимчасова діаграма його роботи - на мал.: 6.2,6.

Розглянемо роботу цього лічильника. У такому лічильнику можна реалізувати рахункову послідовність від 0 до 23 - 1 = 7. Послідовність чисел може бути задана сукупністю трьохразрядних чисел: 000, 001, 010,011, 100, 101, 110, 111.

|

|

|

Поставимо у відповідність кожному розряду числа вихід тригера Qt. У трьохразрядному лічильнику з виходами Q1, Q2, Q3 буде реалізовуватися рахункова послідовність від 0 до 7 (мал.6.2,б). У схемі лічильника вихідний стан встановлюється подачею сигналу "Встан. у 0". Тригери Т змінюють свій стан із закінченням вхідного сигналу, тобто після переходу від рівня 1 до 0. Вхідний сигнал подається на рахунковий вхід тригера 1.

До надходження першого вхідного сигналу лічильник знаходився в нульовому стані. Це відповідає наявності рівня0 на виходах Q1, Q2, Q3. Знадходженням вхідних сигналів X" на рахунковий вхід першого тригера починається робота лічильника.

З приходомпершого сигналу тригер 1 переходить у стан 1 і найого виході встановлюється рівень Q1 = 1. Оскільки на рахункових входах тригерів 2 і 3 не відбувається зміни рівня з 1 на 0, ці тригери зберігаютьстани Q2 =0, Q3 =0. З приходом іншого сигналу тригер 1 переходить у стан 0 (відповідно до роботи Т-триггера). У момент зміни рівня на його виході з Q1= 1 на рівень Q1 = 0 тригер 2 переходить у

Рис. 6.2. Схема асинхронного підсумовуючого трьохрозрядного

лічильника на Т-тригерах з послідовним переносом (а)

і тимчасові діаграми його роботи (б)

стан 1 і на його виході встановлюється рівень Q2 = 1. Стан тригера З залишається незмінним. Тригер 3 перейде в стан 1 лише при надходженні на рахунковий вхід тригера 1 четвертого за рахунком сигналу (див. мал. 6.2,б). При цьому тригер 1 перейде зі стану 1 у стан 0. Перехід від стану 1 до стану 0 викликає зміна рівнів від 1 до 0 на рахунковому вході 2. У результаті тригер 2 також перейде зі стану 1 у стан 0. Такий перехід спричиняє зміна рівня від 1 до 0 на рахунковому вході 3. У результаті на виході Q3 тригера З установлюється рівень 1. При цьому на виходах Q1 і Q2 тригерів 1 і 2 будуть рівні 0. Отже, у лічильнику буде зафіксоване число 4 у двійковому представленні. Це відповідає фіксації моменту надходження четвертого сигналу.

|

|

|

До моменту приходу восьмого за рахунком сигналу на виходах тригерів Q1,Q2,Q3 буде встановлений рівень 1. Надходження восьмого сигналу на рахунковий вхід тригера 1 викликає зміна його стану з 1 на 0. У свою чергу, зміну стану тригера 1 викликає зміна стану тригера 2, а зміна стану тригера 2 приведе до зміни стану тригера 3. У результаті всі тригери лічильника перейдуть у стан 0. Лічильник буде підготовлений до рахунку нової послідовності з восьми сигналів.

На мал. 6.3 показаний асинхронний підсумовуючий чотирьохрозрядний лічильник на JK-тригерах з послідовним переносом

Рис. 6.3. Схема асинхронного підсумовуючого чотирьохрозрядного лічильника на JK-тригерах з послідовним переносом

Рахунковий режим JK-тригера має місце у випадку J = ДО = 1. На мал. 6.3 на входи J і До подаються рівні, що відповідають "1". Рахункові імпульси подаються на вхід синхронізації.

Основними перевагами лічильників з послідовним переносом є мінімальні витрати мікросхем і мінімум електричних зв'язків, що спрощує розведення ліній зв'язку і підвищує перешкодозахищеність схеми. Головний недолік - низька швидкодія, що тим нижче, чим більше коефіцієнт рахунку Kсч =2n і чим більше в лічильнику розрядів n.

На тимчасовій діаграмі (мал. 6.4) показана послідовність переключення тригерів з обліком їх tз. Необхідно це мати на увазі і правильно вибирати Т -період проходження рахункових імпульсів. У загальному випадку при n-розрядному лічильнику час затримки встановлення коду буде

tз.n.=ntз,

а здатність лічильника, що дозволяє, повинназадовольняти умові Т ≥ nt3.

Рис. 6.4. Послідовність переключення

тригерів з урахуванням їх затримок

У лічильниках, що віднімають, із приходом чергового рахункового сигналу попередній результат зменшується на одиницю. У двійковому n-розрядному лічильнику, що віднімає, реалізується рахункова послідовність чисел, починаючи с 2n - 1 і закінчуючи 0. Чергове число в цій послідовності виходить вирахуванням одиниці з попереднього числа. Після одержання значення 0 послідовність повторюється. Порядок зміни станів лічильника, що віднімає, може бути описаний табл. 6.2.

Таблиця 6.2

| X | Q3 | Q2 | Q1 |

|

|

|

З табл.6.2 випливає ще одна відмінність лічильника, що віднімає, від підсумовуючого: тригер кожного наступного розряду переходить в інший стан при сигналі позики, зворотному сигналу переносу в підсумовуючому лічильнику. Тому віднімаючий лічильник на відміну від підсумовуючого будується так, що з входом кожного наступного тригера з'єднується інверсний вихід попереднього тригера. Схема лічильника, що віднімає, з послідовним переносом на JK-тригерах приведена на мал. 6.5,а, а тимчасові діаграми його роботи - на мал. 6.5,б.

Лічильники з керованим напрямком рахунку називають реверсивними. Для побудови реверсивного лічильника необхідно між розрядами включити логічну схему, що забезпечує зв'язок рахункового входу другого і наступного розрядів з виходами Q (підсумовування) чи Q ( вирахування) тригерів попередніх розрядів. Нехай напрямок рахунку задається сигналом Е так, що при Е = О виконується рахунок Хсr з підсумовуванням, а при Е = 1 - вирахування. Тоді сигнал переносу в і-й розряд Рі визначається логічним рівнянням

(6.1)

(6.1)

Рис. 6.5. Схема трьохрозрядного лічильника, що віднімає

JK-тригерах з послідовним переносом (а) і тимчасова діаграма його роботи (б)

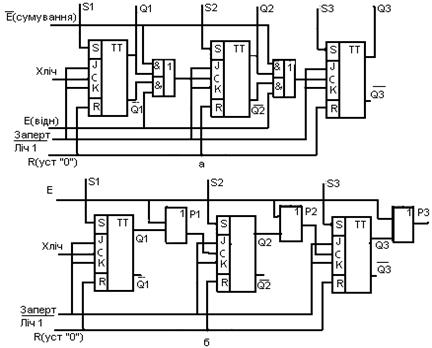

Відповідно тотожним виразом (6.1) можна реалізувати різні схемні варіанти ланцюгів переносу в реверсивних лічильниках (мал. 6.б).

Рис. 6.6. Схема трьохрозрядного реверсивного лічильника на JK-тригерах з послідовним переносом з міжрозрядною логікою керування рахунку на елементах I-АБО (а) і що виключають АБО(6) АБО.

На мал. 6.6,а приведена схема асинхронного реверсивного лічильника з послідовним переносом.

У лічильнику використовуються JK-тригери. У залежності від режиму роботи в реверсивному лічильнику присутній постійний керуючий сигнал "Підсумовування" чи постійний керуючий сигнал Е - "Вирахування". На вхід з першого розряду лічильника подається серія вхідних сигналів. Реверс досягається тим, що в ланцюгах межрфзряднОДх зв'язків відбувається передача сигналу переносу або з прямих виходів Qi, або сигналу позики з інверсних виходів Qi тригерів. Для завдання початкового стану лічильника в ньому передбачені ланцюги рівнобіжного прийому інформації. Дозвіл на роботу лічильника визначається сигналом "Заборона(0)/Рахунок(1)и, подаваним на входи JK-тригерів.

|

|

|

На мал. 6,6 показаний реверсивний лічильник з ланцюгами переносу на елементах " Що Виключає АБО".

Включення додаткових логічних елементів між розрядами збільшує час установлення лічильника tycT. і знижує максимальну частоту зміни станів що реєструються.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 3958; Нарушение авторских прав?; Мы поможем в написании вашей работы!