КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Синхронні лічильники

Для підвищення швидкодії лічильники виконують синхронними з паралельним переносом. Особливість таких лічильників у тому що виходи всіх попередніх розрядів подаються на входи тригера наступного (старшого) розряду, тому тривалість перехідного процесу (час установки коду) у такому лічильнику визначається тривалістю перехідного процесу одного розряду і не залежить від кількості п тригерів.

Завдяки такій організації досягається мінімальний час установлення лічильника tycT. сч, яке не перевищує час встановлення одного тригера tyCT T. Тим самим забезпечується максимальна частота зміни станів лічильника

де tuex - тривалість рахункових імпульсів.

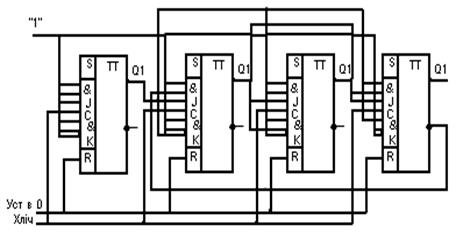

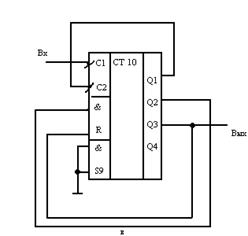

Схема найпростішого підсумовуючого синхронного лічильника показана на мал. 6.7. Тут на інформаційні входи тригерів подаються сигнали, що є логічною функцією стану лічильника і визначальні конкретні тригери, що змінюють свій стан при даному вхідному імпульсі. Принцип стробування імпульсу на вході  даного тригера для розглянутого тут способу рахунку в прямому двійковому коді випливає з тимчасової діаграми на мал. 6.2,6. Він зводиться до наступного: тригер змінює свій стан при надходженні чергового імпульсу синхронізації, якщо всі попередні тригери знаходилися в стані логічної одиниці.

даного тригера для розглянутого тут способу рахунку в прямому двійковому коді випливає з тимчасової діаграми на мал. 6.2,6. Він зводиться до наступного: тригер змінює свій стан при надходженні чергового імпульсу синхронізації, якщо всі попередні тригери знаходилися в стані логічної одиниці.

Рис.6.7. Чотирьох розрядний підсумовуючий лічильник з паралельним переносом

Синтез двійкового лічильника з паралельним переносом, як кінцевого автомата, може бути реалізованим за загальною методикою. Синтез такого лічильника на ИМС К155ТВ1 розглянутий у прикладі,

ПРИКЛАД. Зробити синтез двійкового лічильника, що віднімає, з Ксч =8 на JK- тригерах.:

1. Визначаємо кількість тригерів. Для синтезу лічильника необхідні Iog2 8 = 3 тригери.

2. Оскільки в лічильнику, що віднімає, номер наступного стану на одиницю менше номера попереднього, те кодована таблиця переходів лічильника на тригерах JK-типу буде мати вид табл. 6.3..

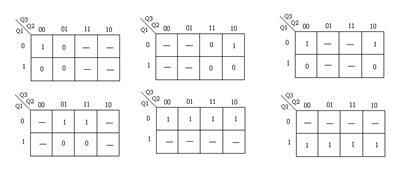

3. Визначаємо за допомогою карт Карно (мал. 6.8) МДНФ функції J3, К2, J2, К2, аргументів Q3, Q2, Q1.

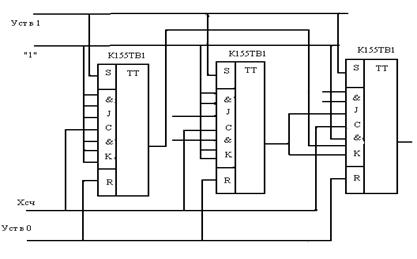

4. Будуємо функціональну схему лічильника (мал. 6.9) на тригерах JK-типу К155ТВ1 по системі функцій:

J3=K3 =  , J2=K2=

, J2=K2=  , J1=K1=''1”.

, J1=K1=''1”.

Таблиця 6.3

| Номер набору | t | t+1 | t | |||||||||

| Q3 | Q2 | Q1 | Q3 | Q2 | Q1 | J3 | K3 | J2 | K2 | J1 | K1 | |

| - | - | - | ||||||||||

| - | - | - | ||||||||||

| - | - | - | ||||||||||

| - | - | - | ||||||||||

| - | - | - | ||||||||||

| - | - | |||||||||||

| - | - | - | ||||||||||

| - | - | - |

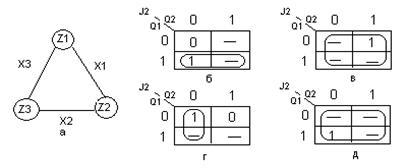

Рис. 6.8. Карти Карно функцій збудження лічильника: а -для J3; 6 - для К3; в -для J2; г- для К2; д- для J1; є- для K1.

На практиці часто виникає необхідність у побудові лічильників з довільним коефіцієнтом рахунка (Ксч Ф 2").

Принцип побудови таких лічильників складається у виключенні деяких стійких станів звичайного двійкового лічильника, що є надлишковими для лічильника з Ксч = 2n. Надлишкові стани виключаються за допомогою зворотних зв’язків усередині лічильника. Зворотні зв’язки реалізують уведенням додаткових логічних ланцюгів, що з'єднують входи і виходи відповідних тригерів. У різних варіантах схем тим самим десятковим числам можуть відповідати різні чотирьох розрядні кодові комбі-нації в залежності від виключених станів, тобто лічильники працюють у різних двійково десяткових кодах (8421, 2421, 4221, 5211 і ін.).

Рис. 6.9. Двійковий лічильник, що віднімає, з паралельним переносом на тригерах К155ТВ1.

Розглянемо особливості побудови таких лічильників на прикладі десяткового лічильника.

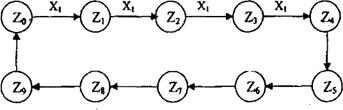

ПРИКЛАД. Виконати синтез десяткового лічильника, що працює в коді 8421, заданого графом (мал. 6.10). Ці лічильники будуються на основі чотирьох тригерних двійкових лічильників виключенням шести надлишкових станів.

Рис.6.10.Граф десяткового лічильника.

1. Оскільки в підсумовуючому лічильнику номер наступного стану на одиницю більше номера попереднього, токодована таблиця переходів лічильника на JK-тригерах буде мати вид табл. 6.4. Функції збудження J4K4, J3K3, J2K2, J1K1 визначаємо використовуючи матрицю переходів JK -тригера.

Таблиця 6.4

| Номер рядка | t | t+1 | t | |||||||||||||

| Q | Q | Q | Q | Q | Q | Q | Q | J | к | J | к | J | к | J | к | |

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - | |||||||||||||

| - | - | - | - |

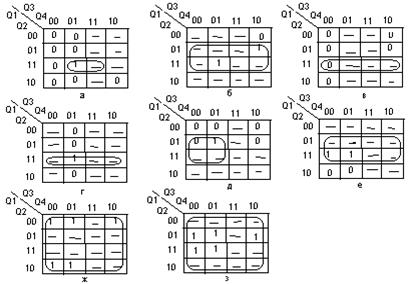

2. Визначаємо за допомогою карт Карно (мал. 6.11,) мінімальні ДНФ функції J4,K4,J3f,K3,J2,K2,J1,K1 аргументів Q4t,,Q3 t, Q2t,Q1t.

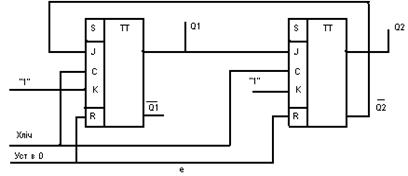

3. Будуємо структурну схему лічильника (мал. 6.12) на JK-тригерах типу К155ТВ1 по системі функцій:

J4=Q3Q2Q1,K4=Q1,J3=Q2Q1,K3=Q2Q1,

J2=  Q1,K2=Q1,J1=1,K1=1.

Q1,K2=Q1,J1=1,K1=1.

Принцип побудови десяткового лічильника можна використовувати при побудові лічильників з будь-яким коефіцієнтом рахунка. Такі лічильники використовуються як дільники частоти. У дільниках частоти вхідна періодична послідовність сигналів на виході формує періодичну послідовність з частотою в п раз менше.

Рис. 6.11. Карти Карно функцій збудження лічильника:

а - для J4; б - для К4; в - для J 3; г- для К3; д - для J2; е - для К2; ж - для J1; з - для К1.

Рис. 6.12. Схема десяткового лічильника на тригерах К155ТВ1.

Послідовність станів дільника частоти може бути довільною важливо лише забезпечити заданий період рахунка Ксг.

ПРИКЛАД. Зробити синтез лічильника по mod 3, заданого графом (мал. 6.13) на JK-тригерах.

Рис. 6.13. Граф лічильника з Ксг (а);картиКарнофункцій збудження J2 (б); К2 (в); J1 (г); К1(д); схема лічильника (є)

1. Визначаємо число тригерів, необхідне для побудови лічильника l=|log2Kcr|=|log23|=2.

2. Робимо кодування станів лічильника. З можливих станів лічильника виключимо, наприклад, стан Qt = Q2= 1 і закодуємо стану лічильника в такий спосіб

Z1=00, Z2=01, Z3=10

3.Складаємо кодовану таблицю переходів лічильника (табл. 6.5). Функції збудження J2, К2, Ji, Kj визначаємо, використовуючи матрицю переходів JK-тригера.

Таблиця 6.5

| хсч | t | t+1 | t | |||||

| Q2 | Qi | Q2 | Qi | h | K2 | J. | K, | |

| - | - | |||||||

| і | - | - | ||||||

| - |

4. Визначаємо за допомогою карт Карно (мал. 6.13, б, у, м, д) мінімальні ДНФ функції J2, K2, J1, K1, аргументів Q2, Q1.

5.Будуємо структурну схему лічильника на JK-тригерах по системі функцій: J2=Q1, K2=1, J1=  , K1=1.

, K1=1.

Каскадні лічильники-дільники виходять у результаті послідовного з'єднання лічильників-дільників з коефіцієнтами розподілу N1, N2,...,Nk для зменшення частоти проходження вхідних сигналів у N1, N2,...,NK раз. Нехай потрібно побудувати лічильник-дільник з N = 72, Для побудови лічильника-дільника з N=12 необхідно з'єднати послідовно три каскади лічильників-дільників з N1=3, N2 =6, N3 =4 (мал. 6.14,а) чи два каскади лічильників-дільників N1= 8, N2=9 (рис. 6.14,6) і т.д.

Рис. 6.14. Лічильник дільник з N = 3 • 6 • 4 = 72 (а)

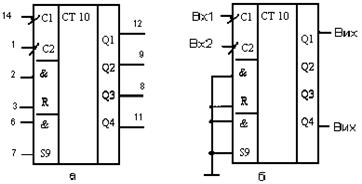

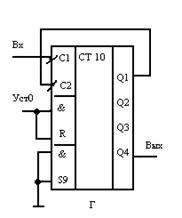

В даний час широке поширення отримали дільники частоти проходження імпульсів з використанням лічильників на інтегральних мікросхемах середнього ступеня інтеграції. Наприклад, використовуючи мікросхему К155ИЕ2 (мал. 6.15), що має Ксч =10, можна одержати дільники з різним коефіцієнтом діленням. У схему лічильника входять чотири тригери, перший з який працює як дільник на два, а три наступних утворять дільник на п'ять. Вихід першого тригера - Q1 його вхід Q. Для організації лічильника - дільника на десять виходів Qx підключають до рахункового входу дільника на п'ять С2. У лічильнику передбачена можливість попереднього асинхронного запису коду 1001. Для цього використовують входи S9. Мікросхема К155ИЕ2 може працювати не тільки як лічильник з Ксч =10. Використовуючи два входи S9 і два входи R можна одержати дільники з. іншими коефіцієнтами розподілу. Одержання різних коефіцієнтів ділення за допомогою мікросхеми К155ИЕ2 приведено в табл. 6.6. На мал. 6.15,6 показаний дільник на 2 і 5, на мал. 6.15,у - дільник на 6, а на мал. 6.15,м -дільник на 10. З'єднання інтегральних мікросхем ИЕ2 у багатокаскадний лічильник показаний на мал. 6.16.

Таблиця 6.6

| Коефіцієнт ділення | Номер виводів | Зовнішні з'єднання виводів мікросхеми | |

| N | вхід | вихід | |

| 2 або 3 к 10 (загальний) | |||

| 8к2;9кЗ | |||

| 11 к2иЗ | |||

| 2 абоЗ к 10 | |||

| 12 к 1;9к2;8кЗ | |||

| 11 к 14; 12к2;9кЗ | |||

| 12 к 1; 11 к2иЗ | |||

| 12 к 1 и 2; 11 к З | |||

| 12к1;2або3к 10 |

Рис. 6.15. Чотирьох розрядний лічильник ДО133-; ДО155-; ДО555-; ДО1533ИЕ2 (а), дільник на 2і 5 (б), дільник на 6 (в), дільник на 10 (г).

Лічильники з попередньою установкою можуть встановлюватися в початковий стан, рівний будь-якому числу від 0 до Ксч = 1. Ця операція здійснюється паралельним записом у лічильник коду необхідного числа. Рахунок (чи додавання вирахування) буде починатися вже не з нуля, а з установленого числа. Лічильники з попередньою установкою звичайно є універсальними і можуть працювати в режимах додавання, вирахування, установки заданого коду, установки нуля (скидання). Це мікросхеми К155ИЕ6, К155ИЕ7, К564ИЕ11, К564ИЕ14.

Рис. 6.16. З'єднання інтегральних мікросхем ДО155ИЕ2 у лічильник з Ксч =1000.

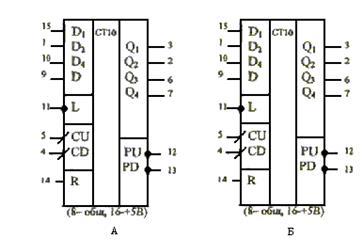

На мал. 6.17,а показана мікросхема К155ИЕ6, яка є двійково-десятковим синхронним реверсивним лічильником. Лічильник має три основних режими: паралельне асинхронне завантаження двійково-десяткового коду по входах D, режим підсумовування і режим вирахування. У двох останніх режимах рахункові імпульси подають на різні входи: при підсумовуванні на вхід CU (Clock-UP), при вирахуванні на вхід CD (Clock-Down). Виходи переносу в зазначених режимах також різні: PU (Propagation-UP) при підсумовуванні і PD (Propagation-Down) при вирахуванні. Мікросхема К155ИЕ7 (мал. 6.17,6) є чотирьох розрядним синхронним реверсивним лічильником. Інтегральна схема ИЕ7 відрізняється від ИЕ6 лише коефіцієнтом перерахування, рівним у даному випадку шістнадцяти. Режими роботи лічильників задає табл. 6.7. Сигнали переносу PU і позики PD формуються по вираженнях

що дозволяє нарощувати розрядність лічильника простим каскадуванням.

На мал. 6.17,6 показаний 12-розрядний лічильник, побудований на трьох ІМС ИЕ7. Установка в нуль і прийом слова здійснюється по асинхронних настановних входах, унаслідок цього їх не можна використовувати для введення зворотного зв'язку з виходів ІМС на її входи.

Рис. 6.17. Двійково-десятковий синхронний реверсивний лічильник

К155ИЕ6 (а), чотирьохрозрядний синхронний реверсивний лічильник

К155ИЕ7 (б), схема каскадного об'єднання лічильників ИЕ6 і Ие7 (в)

Таблиця 6.7

| R | L | cu | CD | Режим |

| X | X | X | Установка в 0 | |

| X | X | Прийом коду з входів | ||

| 0/1 | 0/1 | Збереження | ||

| Прямий рахунок | ||||

| Зворотний рахунок |

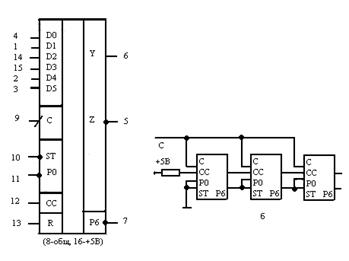

Становить інтерес мікросхема К155ИЕ8 (мал. 6.18,а) - шестиразрядний двійковий дільник числа вхідних імпульсів з коефіцієнтом ділення, що перебудовується, чи, як її ще називають, програмуючий перетворювач коду в число імпульсів.

Рис. 6.18. Умовне позначення мікросхеми К155ИЕ8 (а), схема каскадного об'єднання лічильників-дільників К155ИЕ8

Одна мікросхема забезпечує будь-який коефіцієнт ділення в межах від 64:1 до 64:63 із кроком в одиницю. У загальному випадку коефіцієнт ділення визначається виразом

N = 64/(25D5 + 24D4+ 23D3 + 22D2 + 21D1, + 2°D0),

де D = (D5,D4,D3,D2,D1,Do) - керуючий двійковий позиційний код, у якому тільки один з розрядів може приймати значення "I".

У противному випадку, тобто, якщо одночасно кілька розрядів приймуть значення рівні "1",ІС буде функціонувати не як дільник частоти, а як дільник числа імпульсів - на виході ИС одержимо неперіодичну послідовність імпульсів. Коефіцієнт ділення буде число дробове і вихідна частота, обумовлена формулою:

характеризує середню частоту за кілька циклів.

Припустимі комбінації D, а також залежність коефіцієнта розподілу від D представлені в табл. 6.8.

Таблиця 6.8

| D5 | D4 | D3 | D2 | D, | Do | N |

Для запуску дільника на керуючих входах установлюють наступні логічні рівні:

Для запуску дільника на керуючих входах установлюють наступні логічні рівні:  = ST = R = О, СС = 1 і D відповідно до необхідного коефіцієнта ділення. Зміна станів внутрішніх тригерів відбувається в моменти формування позитивних фронтів на інформаційному вході С.

= ST = R = О, СС = 1 і D відповідно до необхідного коефіцієнта ділення. Зміна станів внутрішніх тригерів відбувається в моменти формування позитивних фронтів на інформаційному вході С.

Виходи Y і Z є комплементарними. Причому вихід Z використовується при каскадуванні для з'єднання з входом СС наступного каскаду (мал. 6.18,6).

Обнуління дільника асинхронне і настає при R = 1. Лічильники можна використовувати при побудові дільників імпульсів. У цьому випадку необхідно використовувати ще і дешифратор для виділення, а також і керування вихідними ланцюгами. Схема на двійковому лічильнику з використанням дешифратора приведена на мал. 6.19(F - формувач).

Рис. 6.19. Дільник імпульсів.

У цій схемі вихідні сигнали з'являються періодично на виходах Y1 Y2,...,Y2k. При цьому в кожен момент вихідний сигнал з'являється тільки на одному з виходів Y1Y2,...,Y2k.

|

|

Дата добавления: 2015-06-27; Просмотров: 6400; Нарушение авторских прав?; Мы поможем в написании вашей работы!