КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Организация ИМС динамической памяти

|

|

|

|

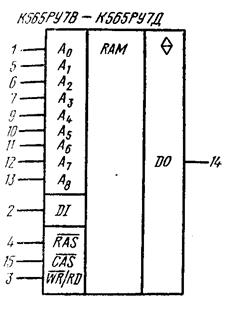

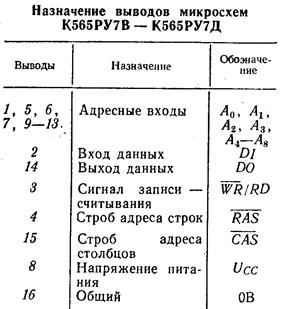

УГО ИМС динамической памяти К565РУ7 и назначение её выводов приведены на рисунке 5.2.3. Эта ИМС представляет собой синхронное оперативное ЗУ с произволь-ной выборкой, ёмкостью 256Кбит и организацией 256Кбит×1 разряд. ИМС построена на основе nМОП-структур, потребляет в режиме обращения мощность 360 мВт при напряжении питания 5 В и имеет выход с тремя состояниями.

Рисунок 5.2.4 – ИМС К565РУ7: условное графическое обозначение

и назначение выводов

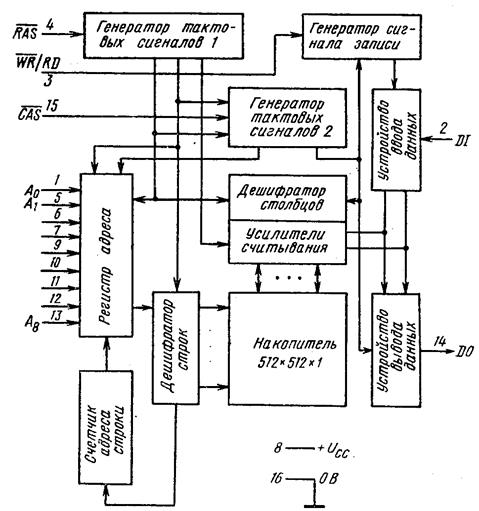

В состав микросхемы (см. рисунок 5.2.5) входят: накопитель из однотранзисторных запоминающих элементов 512 строк×512 столбцов; усилители считывания, дешифраторы строк и столбцов; устройства ввода и вывода данных; регистр адреса; генераторы тактовых сигналов и сигналов записи; счётчик адреса строк.

Рисунок 5.2.5 – Структурная схема микросхемы К565РУ7

В ДОЗУ количество входов адреса уменьшают два раза по сравнению с количест-вом разрядов адреса, применяя мультиплексирование. При этом полный адрес делится на два полуадреса, один из которых – адрес строки, а другой – адрес столбца матрицы запоминающих элементов.

Полуадреса подаются на одни и те же выводы ИМС поочерёдно. Адрес строки подаётся при действии строба RAS = 0 (Row Address Strobe), а адрес столбца – при действии строба CAS = 0 (Column Address Strobe).

Сокращение числа внешних выводов ИМС уменьшает суммарную ёмкость запо-минающих элементов и стоимость ИМС. Кроме того, во многих ИМС при регенера-ции адрес столбца не требуется. Поэтому мультиплексирование упрощает использо-вание ИМС динамической памяти.

5.2.4 Увеличение ёмкости ОЗУ

Одна ИМС обычно не обеспечивает требования по ёмкости и разрядности ОЗУ. По-этому ИМС памяти совместно с регистрами, дешифраторами, устройствами управле-ния объединяют в модули ОЗУ.

|

|

|

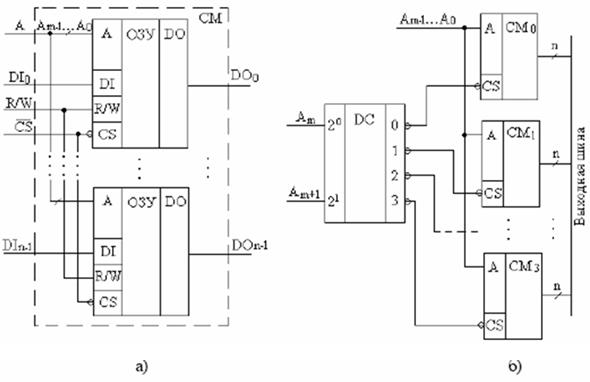

Наращивают разрядность субмодулей СОЗУ, объединяя одноимённые адресные и управляющие входы, как это показано на рисунке 5.2.6, а. Данные по входам DI n-1- DI0 и выходам DО n-1- DО0 записывают и считывают всеми разрядами одновременно

при наличии на входах выбора микросхемы CS сигнала логического нуля. При нали-чии на входах CS сигнала логической единицы субмодуль СОЗУ находится в режиме хранения и не реагирует на адресные и управляющие сигналы.

Для наращивания числа хранимых слов ИМС объединяют в субмодуль, соединяя одноимённые выводы ИМС за исключением выводов выбора микросхемы CS (см. рисунок 5.2.6, б). Эти выводы подключаются к выходам дешифратора кода адреса, на входы которого подают старшие разряды кода адреса.

Рисунок 5.2.6 – Увеличение ёмкости ОЗУ: а) увеличением разрядности;

б) увеличением разрядности шины адреса

При использовании ИМС ДОЗУ (см. рисунок 5.2.5) разрядность субмодулей увели-чивают так же, как и СОЗУ, объединяя дополнительно выводы RAS и CAS. Для наращивания числа хранимых слов потребуется два дешифратора для формирования сигналов выбора микросхем CS. Эти сигналы должны подаваться на входы CS микросхем через двухвходовые схемы логического умножения, на вторые входы которых подаются сигналы RAS и CAS.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 2098; Нарушение авторских прав?; Мы поможем в написании вашей работы!