КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Общая характеристика регистров

|

|

|

|

Лекция 7. Регистры

Тема III. Последовательностные (накапливающие) устройства

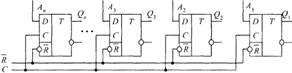

Регистром называется типовой функциональный узел цифрового устройства, предназначенный для приема, временного хранения, преобразования и выдачиn - разрядного двоичного слова. Регистр содержит регулярный набор однотипных триггеров, в каждом из которых хранится значение одного двоичного разряда машинного слова. Наиболее часто используют триггеры типов RS, JK и D (рис. 3.23).

Рис. 3.23. Схема регистра на D-триггерах

Регистры, предназначенные только для приема (записи), хранения и передачи информации, называются элементарными или фиксаторами. Регистры, в которых хранение данных совмещается с микрооперациями сдвига, называются сдвиговыми. Элементарные регистры строят на одноступенчатых триггерах, а сдвиговые — на двухступенчатых или D -триггерах с динамическим управлением. Логическая функция регистра обозначается буквами RG (register). Регистры обеспечивают хранение команд, адресов памяти, результатов операций, индексов и т.д.

Регистры классифицируют по следующим признакам:

Ø способу управления записью — асинхронные и синхронные;

Ø способу записи и выдачи двоичных слов — параллельные, последовательные и универсальные. В параллельных регистрах запись и выдача слов производится одновременно всеми разрядами, а в последовательных — разряд за разрядом в направлении от младших разрядов к старшим или наоборот; универсальные регистры обеспечивают как параллельный, так и последовательный обмен информацией;

Ø числу линий для представления значения одного разряда слова (бита информации) — однофазные и парафазные. При однофазном представлении значение каждого разряда слова передается по одной линии связи, а при парафазном — по двум линиям (одновременно отображается прямое и инверсное значение разряда);

|

|

|

Ø числу тактов для записи слова — одно -, двух - и многотактные;

Ø составу выполняемых микроопераций — установочные, записи, считывания, поразрядные логические и сдвига, а также преобразования последовательного кода в параллельный и наоборот;

Ø направлению сдвига — односторонние (левый или правый сдвиг) и двухсторонние (реверсивные);

Ø типу используемых триггеров;

Ø элементной структуре — потенциальные, импульсные и потенциально - импульсные.

7. 1. 1. Установочные микрооперации.

Однофазный и парафазный способ записи информации. Установочные микрооперации служат для переключения регистров в определенное состояние. Например, установка регистра в состояние “0” или “1”; установка парных разрядов в состояние “0”, а непарных — в состояние “1”; запись в регистр некоторой константы или обнуление некоторых байтов и т.д. Установочные микрооперации преимущественно используют асинхронные входы регистра, например, вход сброса  для схемы, изображенной на (рис. 3.23).

для схемы, изображенной на (рис. 3.23).

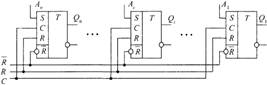

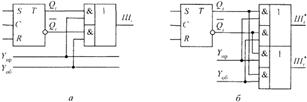

В регистрах на RS - или JK -триггерах возможен однофазный или парафазный способ записи информации. При однофазной записи значение каждого разряда слова A = An An –1,... Ai,... A 1 поступает по одной линии связи на вход S (или J) соответствующих триггеров. После считывания записанной информации регистр должен обнулиться по общему R -входу (рис. 3.24). Таким образом, при однофазной записи частота обмена информацией уменьшается, поскольку процессы ввода и сброса чередуются.

Рис. 3.24. Схема регистра с однофазной записью данных

При парафазной записи информации значение каждого разряда слова A передается по двум линиям связи. При этом прямое значение Ai поступает на вход S (или J) соответствующих триггеров, а инверсное значение  i — на вход R (или K). В этом случае не требуется предварительного сброса регистра в состояние “0”, потому что такую функцию выполняет сигнал

i — на вход R (или K). В этом случае не требуется предварительного сброса регистра в состояние “0”, потому что такую функцию выполняет сигнал  i (рис. 3.25).

i (рис. 3.25).

|

|

|

Рис. 3.25. Схема регистра с парафазной записью данных

В регистрах на D -триггерах, имеющих один информационный вход, возможен только однофазный способ записи информации. С приходом очередного синхроимпульса записывается новая информация или, при отсутствии данных на входной шине, состояние регистра автоматически обнуляется (см. рис. 3.23).

При необходимости сохранения информации на несколько тактов в регистрах на D -триггерах следует использовать разрешающий V -вход, или блокировать прохождение синхроимпульса на C -вход.

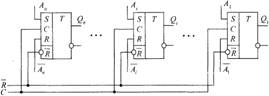

Запись информации от двух источников. Для записи информации от нескольких источников (направлений) на входе каждого триггера ставят дополнительные комбинационные схемы, образующие входную логику регистра. Каждое направление имеет свою совокупность электрических линий (шину), по которым передаются сигналы, отображающие значения разрядов слова. Если n -разрядное слово передается однофазным кодом, то шина имеет n линий связи, а если парафазным кодом — то 2 n линий. Запись каждого слова инициируется соответствующим управляющим сигналом Y 1, Y 2 и т.д.

Для записи в регистр на RS -триггерах однофазным кодом слов A и B требуется реализовать следующие поразрядные функции возбуждения входа Si:

Si = Y 1 Ai  Y 2 Bi, (3.12)

Y 2 Bi, (3.12)

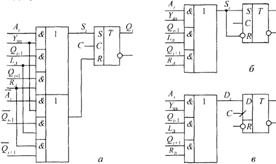

где Ai и Bi — двоичные разряды слов A и B; Y 1 и Y 2 — сигналы управления приема слов A и B соответственно. Схема входной логики i -го разряда регистра на основе уравнения (3.12) показана на (рис. 3.26 а).

Рис. 3.26. Схемы разряда регистра с записью слов от двух источников:

а — однофазным кодом; б — парафазным кодом

Для записи в регистр на JK -триггерах парафазным кодом слов A и A требуется реализовать следующие поразрядные функции возбуждения входов Ji и Ki.

Ji = Y 1 Ai  Y 2 Bi; Ki = Y 1

Y 2 Bi; Ki = Y 1  i

i  Y 2

Y 2  i. (3.13)

i. (3.13)

Схема входной логики i -го разряда регистра на основе уравнений (3.2) показана на (рис. 3.26 б).

Считывание информации. Информация, хранимая в регистрах, может передаваться во внешние схемы однофазным или парафазным способом в прямом или обратном коде. Для реализации микроопераций считывания к выходам каждого триггера подключаются комбинационные схемы, образующие выходную логику регистра.

|

|

|

Схемы выходной логики строятся на основе следующих поразрядных логических уравнений:

для считывания однофазным прямым или обратным кодом

Шi = Y пр Qi  Y об

Y об  i; (3.14)

i; (3.14)

для считывания парафазным прямым или обратным кодом

= Y пр Qi

= Y пр Qi  Y пр

Y пр  i;

i;  = Y об

= Y об  i

i  Y об Qi; (3.15)

Y об Qi; (3.15)

где Y пр и Y об — управляющие сигналы выдачи соответственно прямого или обратного кода; Qi и  i — прямое и инверсное значение, выхода i -го разряда регистра; Шi — разряд однофазной шины данных;

i — прямое и инверсное значение, выхода i -го разряда регистра; Шi — разряд однофазной шины данных;  и

и  — разряды парафазной шины данных.

— разряды парафазной шины данных.

Очевидно, что управляющие сигналы Y пр и Y об не должны совпадать во времени. Например, при считывании информации парафазным обратным кодом получим:

Y пр = “0”; Y об = “1”;  =

=  i;

i;  = Qi.

= Qi.

Схемы выходной логики для i -го разряда на основе уравнений (3.14) и (3.15) показаны на (рис. 3.27).

Рис. 3.27. Схемы выходной логики i -го разряда регистра для считывания информации:

а — однофазным кодом; б — парафазным кодом

7. 1. 2. Логические микрооперации в регистрах. В регистрах могут выполняться следующие поразрядные (без переносов) логические микрооперации над словами A и B: логическое сложение и умножение: RG 1 = A  B; RG 1 = A

B; RG 1 = A  B; сложение по модулю два и его отрицание: RG 1 = A

B; сложение по модулю два и его отрицание: RG 1 = A  B; RG 1 =

B; RG 1 =  ; инверсия слова: RG 1 =

; инверсия слова: RG 1 =  .

.

Логические микрооперации предполагают наличие первого слова A в регистре. С учетом этого логическое сложение слов A и B в регистре на RS - или JK -триггерах с однофазной записью выполняется вводом слов B без предварительного сброса. Логическое умножение реализуется подачей инверсных значений разрядов слова B на входы R (или K) триггеров регистра. Действительно, если значение Bi = “0”, то  i = “1” и соответственно триггеры обнуляются, что и требуется для поразрядного логического умножения.

i = “1” и соответственно триггеры обнуляются, что и требуется для поразрядного логического умножения.

Микрооперации сложения по модулю два и его отрицания реализуются в регистрах на T -триггерах. Вначале записывается слово A, а затем без предварительного сброса по счетному входу вводится слово B. После этого на прямых выходах триггеров фиксируется результат операции Q = A  B, а на инверсных выходах —

B, а на инверсных выходах —  =

=  . Микрооперация инвертирования состоит в подаче импульса на все T -входы триггеров регистра, в которых хранится слово A. В итоге на прямых выходах триггеров устанавливается результат согласно соотношению Qi = Ai

. Микрооперация инвертирования состоит в подаче импульса на все T -входы триггеров регистра, в которых хранится слово A. В итоге на прямых выходах триггеров устанавливается результат согласно соотношению Qi = Ai  1 =

1 =  i.

i.

|

|

|

Микрооперации сдвига. Сдвиг — это одновременное пространственное перемещение двоичного слова в разрядной сетке с сохранением порядка следования нулей и единиц. Регистры, предназначенные для выполнения микроопераций сдвига, называются регистрами сдвига или сдвиговыми.

Микрооперации сдвига используют в процессе выполнения команд умножения, деления и нормализации. Кроме того, с помощью сдвига осуществляется преобразование параллельного кода в последовательный или наоборот (например, при обмене информацией с магнитными лентами и дисками).

Сдвиг слова может выполняться вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Обозначим одноразрядные микрооперации сдвига вправо и влево символами R и L соответственно. Различают правый и левый арифметический (R a, L a), логический (R л, L л) и циклический (R ц, L ц) сдвиги слова.

Пусть в регистре A записано слово AnAn –1,... A 2,... A 1, где A 1 — младший разряд; An — старший разряд. Символически микрооперации сдвига записываются следующим образом:

арифметические сдвиги (знаковый разряд не сдвигается):

RGA; = R a (A) = An 0 An –1,... A 2; RGA; = L a (A) = AnAn –2,... A 1 0;

логические сдвиги (одновременно сдвигаются все разряды):

RGA; = R л (A) = 0 AnAn –1,... A 2; RGA; = L л (A) = An –1 An –2,... A 1 0;

циклические сдвиги (между старшим и младшим разрядами имеется кольцевая связь):

RGA; = R ц (A) = A 1 AnAn –1,... A 2; RGA; = L ц (A) = An –1 An –2,... A 1 An.

Арифметические и циклические сдвиги преимущественно используют при выполнении команд в процессорах, а логические сдвиги обеспечивают преобразование последовательного кода в параллельныйи наоборот в устройствах связи с магнитными лентами и дисками.

Сдвиговые регистры проектируют на двухступенчатых RS - (или JK) или D -триггерах с динамическим управлением по фронту. Такие триггеры обеспечивают разделение во время процессов приема новой информации в каждом разряде и выдачи (сдвига) старой.

Примем, что в реверсивном регистре должны выполняться параллельная запись слова A по сигналу управления Y зп и сдвиги информации влево и вправо под воздействием управляющих сигналов L л и R л. Функции возбуждения Si и Ri для каждого разряда регистра сдвига на двухступенчатых RS -триггерах имеют вид:

Si = Y зп Ai  R л Qi +1

R л Qi +1  L л Qi –1; Ri = Y зп

L л Qi –1; Ri = Y зп  i

i  R л

R л

L л

L л  . (3.16)

. (3.16)

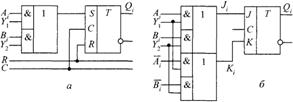

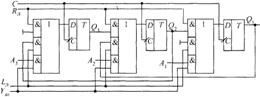

Схема одного разряда регистра сдвига на RS -триггерах согласно уравнениям (3.16) показана на (рис. 3.28 а).

Экономичная схема разряда регистра, в которой функция на R -входе триггера образуется инвертированием сигнала Si, показана на (рис. 3.28 б). Однако в этом случае время записи данных увеличивается за счет задержки инвертора.

Для регистра сдвига на D -триггерах функции возбуждения имеют вид:

Di = Y зп Ai  R л Qi +1

R л Qi +1  L л Qi –1. (3.17)

L л Qi –1. (3.17)

Схема разряда регистра сдвига на D -триггерах согласно уравнению (3.17) показана на (рис. 3.28 d).

Рис. 3.28. Схема разряда регистра сдвига:

а — на RS-триггере; б — с инвертором на входе R; в — на D-триггере

Пример построения реверсивного трехразрядного регистра сдвига на D -триггерах с динамическим управлением представлен на (рис. 3.29).

Рис. 3.29. Схема реверсивного регистра сдвига на D-триггерах:

Реверсивный регистр сдвига работает следующим образом. При значении сигнала Y зп = “1” в регистр записывается информация параллельным однофазным кодом. При значении сигнала R л = “1” хранимая информация одновременно сдвигается в сторону младших разрядов, при этом разряд Q 3 обнуляется. При значении сигнала L л = “1” информация в регистре одновременно сдвигается в сторону старших разрядов, при этом разряд Q 1 обнуляется. Запись и сдвиг информации происходят по фронту синхроимпульса.

Преобразование последовательного кода в параллельный и наоборот. Схема четырехразрядного регистра сдвига вправо на JK -триггерах, которая обеспечивает преобразование кодов, показана на (рис. 3.30 а). Старший разряд регистра с помощью инвертора на K -входе работает в режиме D -триггера.

Рис. 3.30. Регистра сдвига:

а — схема; б, в — преобразование последовательного кода в параллельный и наоборот

Пусть от накопителей на магнитных дисках на вход регистра по линии D поступает последовательный код слова A = 1101 в направлении от старших разрядов к младшим. Значение разрядов слова поступает одновременно с синхроимпульсами, которые обеспечивают как прием кода в старший разряд, так и одновременный сдвиг содержимого регистра вправо (рис. 3.30 б). После прихода четырех синхроимпульсов на выходах регистра Q 4 - Q 1 устанавливается код 1101. Таким образом осуществляется преобразование последовательного кода в параллельный, часто называемое последовательным вводом слова в регистр.

Преобразование параллельного кода в последовательный также выполняется сдвигом хранимого слова. Процесс преобразования параллельного кода слова A = 1101 в последовательный в направлении от младших разрядов к старшим с помощью сдвига вправо показан на (рис. 3.30 в).

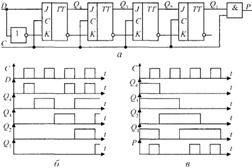

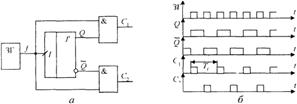

Распределители тактов. В системах синхронизации и устройствах управления используют распределители тактов (РТ), которые вырабатывают серии импульсов. Простейший способ построения распределителя тактов состоит в делении счетными триггерами частоты прямоугольных импульсов f от задающего генератора (ЗГ).

На прямом и инверсном выходах триггера с помощью схем совпадения образуются две последовательности импульсов фаз C 1 = fQ и C 2 = f  (рис. 3.31 а). Длительность такта синхронизации TC в два раза больше периода следования импульсов ЗГ (рис. 3.31 б).

(рис. 3.31 а). Длительность такта синхронизации TC в два раза больше периода следования импульсов ЗГ (рис. 3.31 б).

Рис. 3.31. Распределитель тактов: а — схема; б — временные диаграммы

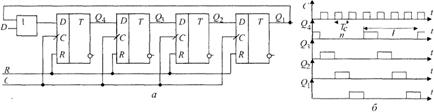

Распределители тактов строятся также на кольцевых регистрах, в которых выход младшего разряда соединен с информационным входом старшего, если реализован сдвиг вправо (рис. 3.32 а), или имеется связь от старшего разряда к младшему при сдвиге влево.

Кольцевой регистр в качестве распределителя тактов функционирует следующим образом. Вначале через схему ИЛИ в старший разряд Q 4 записывается единица. Затем по фронту каждого синхроимпульса единица сдвигается вправо и поочередно появляется на выходах Q 3, Q 2 и Q 1. С приходом четвертого синхроимпульса единица из младшего разряда Q 1 по кольцевой связи и через схему ИЛИ снова записывается в старший разряд. Число выходов распределителя тактов определяется количеством триггеров кольцевого регистра. В распределителе тактов на основе четырехразрядного кольцевого регистра формируются импульсы фаз C 1, C 2, C 3 и C 4, которые образуют машинный такт T длительностью в четыре периода синхроимпульсов, то есть T = 4 ТC (рис. 3.32 б).

Рис. 3.32. Кольцевой регистр: а — схема; б — временные диаграммы

Недостатком схемы, изображенной на (рис. 3.32 а), является возможность сбоя — появления лишних единиц в разрядах, например, 1100, 1001.

В кольцевом регистре с самовосстановлением после сбоя используется схема контроля, которая при неправильной работе автоматически возвращает регистр в исходное состояние.

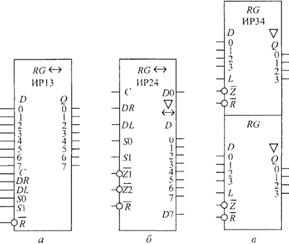

7. 1. 3. Регистры в микросхемах серии КР1533. Серия микросхем КР1533 содержит широкий набор регистров. Большинство регистров — восьмиразрядные с третьим состоянием выхода и одно- или двухсторонним сдвигом (рис. 3.33). Микросхема КР1533ИР13 (рис. 3.33 а) — это восьмиразрядный реверсивный сдвиговой регистр. Он имеет входы для параллельной записи данных D 0- D 7, синхронизации C, последовательного приема DR и DL, задания режимов работы S 1, S 0 и вход сброса  . Информация считывается с параллельных выходов Q 0- Q 7. Разряды нумеруются слева направо: Q 0 — старший разряд, Q 7 — младший.

. Информация считывается с параллельных выходов Q 0- Q 7. Разряды нумеруются слева направо: Q 0 — старший разряд, Q 7 — младший.

Рис. 3.33. Регистры серии КР1533: а — ИР13; б — ИР24; в — ИР34

Регистр обеспечивает четыре режима работы: S 1 ∙ S0 = “00” — хранение данных (блокировка); “01” — последовательный прием со сдвигом вправо по входу DR; “10” — последовательный прием со сдвигом влево по входу DL; “11” — параллельная запись по входу D 0- D 7. Запись и последовательный прием данных осуществляются по фронту синхроимпульса C. Во время записи последовательный ввод данных блокируется. При  = “0” все входы регистра устанавливаются в состояние “0”.

= “0” все входы регистра устанавливаются в состояние “0”.

Микросхема КР1533ИР24 (рис. 3.33 б) — это восьмиразрядный реверсивный сдвиговой регистр с двунаправленными выводами D 0- D 7 для приема и выдачи информации. Выводы D 0- D 7 имеют Z -состояния, в которые они переключаются при подаче сигнала лог. “1” хотя бы на один из входов  1 или

1 или  2. Регистр содержит также дополнительные выводы D 0 и D 7, которые связаны соответственно со старшим и младшим разрядами, но не имеют Z-состояний.

2. Регистр содержит также дополнительные выводы D 0 и D 7, которые связаны соответственно со старшим и младшим разрядами, но не имеют Z-состояний.

Регистр обеспечивает четыре синхронных режима работы в зависимости от сигналов на входах S 1 ∙ S 0: “00” — хранение (блокировка); “01” — последовательная запись по входу DR со сдвигом вправо; “10” — последовательная запись по входу DL со сдвигом влево; “11” — параллельный прием данных. Первые три режима реализуются при  1 =

1 =  2 = “0”; при этом информация передается на выводы D 0- D 7, а четвертый режим осуществляется независимо от значений сигналов на выходах

2 = “0”; при этом информация передается на выводы D 0- D 7, а четвертый режим осуществляется независимо от значений сигналов на выходах  1 и

1 и  2. Все операции выполняются по фронту сигнала синхронизации C.

2. Все операции выполняются по фронту сигнала синхронизации C.

Регистры ИР13, ИР24 серии КР1533 используют для временного хранения информации, преобразования данных из параллельной формы в последовательную и наоборот.

Микросхема КР1533ИР34 (рис. 3.33 в) — это два независимых четырехразрядных регистра с тремя состояниями на выходах Q 0- Q 3. Параллельная запись данных по входам D 0- D 3 выполняется при сигнале лог. “1” на входе разрешения L; если L = “0”, то регистр переходит в режим хранения. Высокий уровень сигнала на входе  переключает выходы регистра в третье состояние. Однако при этом в регистр могут записываться новые данные или сохраняться предыдущие. Микросхема обладает большой нагрузочной способностью, что в сочетании с тремя состояниями позволяет использовать регистр в магистральных структурах без дополнительных интерфейсных схем.

переключает выходы регистра в третье состояние. Однако при этом в регистр могут записываться новые данные или сохраняться предыдущие. Микросхема обладает большой нагрузочной способностью, что в сочетании с тремя состояниями позволяет использовать регистр в магистральных структурах без дополнительных интерфейсных схем.

Мощность потребления регистров ИР13, ИР24 и ИР34 серии КР1533 составляет примерно 200 мВт, а время записи информации — 15-20 нс.

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 4370; Нарушение авторских прав?; Мы поможем в написании вашей работы!