КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Таймери/лічильники

|

|

|

|

У початковій архітектурі MCS - 51 два 16-розрядні таймери/лічильника, Таймер 0 і Таймер 1. Кожен з них незалежно може бути запрограмований на роботу в якості або таймера(відлік часу через підрахунок внутрішніх імпульсів синхронізації), або лічильника(підрахунок подій на зовнішньому вході). У обох випадках перехід через заздалегідь встановлений рубіж призводить до формування запиту переривання.

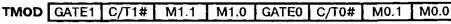

Вибір режиму роботи кожного з таймерів робиться бітами З/Тх# (х = 0,1) регістра TMOD. Підрахунок подій робиться за допомогою інкремента програмно доступного регістра даних, який з¬стоїть з регістра молодшого байта TLx і регістра старшого байта ТНх.

При роботі в режимі таймера(З/Тх# = 0) регістр TLx нарощується в кожному машинному циклі і частота рахунку рівна Fosc/12.

У режимі лічильника(З/Тх# = 1) регістр TLx нарощується при пері¬ході сигналу на вході Тх з " 1" в " 0". Входи опитуються під час фази S5P2 кожного машинного циклу. При виявленні високого рівня сигналу в одному циклі і низького рівня в наступному циклі лічильник инкрементируется. Нове значення в регістрі з'являється під час фази S3P1 циклу, що йде за тим, в якому був виявлений перехід. По¬скольку на розпізнавання переходу йде два машинні цикли, максимальна частота рахунку складає Fosc/24. Обмежень на шпаруватість вхідного сигналу немає, але для упевненої фіксації перепаду сигнал повинен утримуватися в кожному значенні принаймні один машинний цикл.

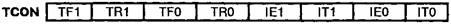

Лічильники/таймери обслуговуються регістром режиму TMOD і регістром управління TCON.

| Ім'я біта | Номер біта | Функція |

| GATE1 | TMOD.7 | Біт управління Таймером 1. При GATE 1=1 Таймер 1 працює завжди при TR1=1. При GATE1=0 для роботи потрібна умова TR1=1 і INT1#=1. |

| С/Т1# | TMOD.6 | Біт вибору типу подій для Таймера 1. При СД1#=1 він працює як лічильник, при СД1#=0 як таймер. |

| М1.1 | TMOD.5 | Біт 1 визначення режиму роботи Таймера 1. |

| М1.0 | TMOD.4 | Біт 0 визначень режиму роботи Таймера 1. |

| GATE0 | TMOD.3 | Біт управління Таймером 0. При GATE0=1 Таймер 0 працює завжди при TR0=1. При GATE0=0 для роботи потрібна умова TR0=1 і INT0#=1. |

| С/Т0# | TMOD.2 | Бит выбора типа событий для Таймера 0. При СД0#=1 он работает как счетчик, при как таймер. |

| М1.0 | TMOD.1 | Біт 1 визначення режиму роботи Таймера 0. |

| М0.0 | TMOD.0 | Біт 0 визначень режиму роботи Таймера 0. |

|

|

|

Біти Ml і МО таким чином визначають режими роботи таймерів/ лічильників:

| М1 | МО | Режим роботи |

| Режим 0. ТНх як 8-розрядний таймер/лічильник. TLx як 5-розрядного переддільника | ||

| Режим 1. 16-разрядный таймер/лічильник. ТНх і TLx включені послідовно | ||

| Режим 2. 8-разрядный таймер/лічильник TLx з автоперезавантаженням значенням з ТНх | ||

| Режим 3. TL0 як 8-розрядний таймер/лічильник, керований бітами управління Таймера 0. TH0 як 8-розрядний таймер/лічильник, керований бітами управління Таймера 1. Таймер 1 не працює. |

| Ім'я біта | Номер біта | Функція |

| TF1 | TCON.7 | Прапор переповнювання Таймера 1. Встановлюється під час переходу рахункового регістра таймера із стану FFH в стан ООН. Очищається при передачі управління на процедуру обробки переривання. |

| TR1 | TCON.6 | Біт запуску Таймера 1. При TR1=1 рахунок дозволений. |

| TF0 | TCON.5 | Прапор переповнювання Таймера 0. Встановлюється під час переходу рахункового регістра таймера із стану FFH в стан ООН. Очищається при передачі управління на процедуру обробки переривання. |

| TR0 | TCON.4 | Біт запуску Таймера 0. При TR0=1 рахунок дозволений. |

| IE1 | TCON.3 | Прапор запиту переривання по вхід INT1#. |

| IT1 | TCON.2 | Біт селектора типу активного сигналу на вході INT1#. При 1Т1=1 активним є перехід "Г - "0й, при 1Т1=0 активним являється низький рівень сигналу. |

| 1Е0 | TCON.1 | Прапор запиту переривання по вхід INT0#. |

| IT0 | TCON.O | Біт селектора типу активного сигналу на вході INT0#. При 1Т0=1 активним є перехід "Г - " 0", при 1Т0=0 активним являється низький рівень сигналу. |

|

|

|

Вибір типу підраховуваних подій для Таймера 0 і Таймера 1, тобто призначення їм функції таймера або лічильника, визначається значенням біта управління З/Тх# регістра TMOD. Таймери здатні працювати в трьох режимах, вибір режиму для кожного таймера робиться комбінацією бітів Mix, Мох того ж регістра.

Рахунок дозволяється бітом TRx, якщо біт GATEx = 0. Коли рахункове значення переходить із стану все " 1" в стан все " 0", встановлюється прапор запиту переривання TFx. Установка біта GATEx = 1 дає можливість управляти таймером від входу INTx# і вимірювати таким чином ширину імпульсів. Установка бітів запуску не очищає рахункові регістри.

Режим 0. У цьому режимі має місце 13-розрядний рахунковий регістр, в якому регістр ТНх працює як 8-розрядний лічильник, а регістр TLx використовується як 5-бітового переддільника.

Режим 1. Цей режим аналогічний режиму 0, але використовуються усі 16 розрядів регістрів ТНх і TLx.

Режим 2. У цьому режимі регістр TLx працює 8-розрядний рахунковий регістр. Після переповнювання він автоматично перезавантажується значенням з регістра ТНх, який при цьому свого заздалегідь запрограмованого значення не втрачає.

Режим 3. Таймер 1 в цьому режимі блокований, начебто біт TR1 був скинутий.

Таймер 0 в режимі 3 працює як два незалежні рахункові регістри, причому регістр TL0 управляється бітами управління Таймера 0, а регістр ТНО управляється бітами управління Таймера 1.

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 1814; Нарушение авторских прав?; Мы поможем в написании вашей работы!