КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

То есть к следующему фронту тактового сигнала должен закончить свою работу самый медленный из узлов, и тогда его выходной код будет записан в регистр правильно

Регистры также широко используются для организации конвейерной обработки, позволяющей существенно повысить тактовую частоту работы схемы. Ускорение при этом достигается за счет распараллеливания работы нескольких последовательно включенных узлов схемы.

Еще одно применение регистров связано с запоминанием нескольких последовательных значений изменяющегося входного кода. Это позволяет сравнивать предыдущее значение кода с последующим значением этого же кода или производить арифметические операции над несколькими последовательными значениями одного и того же кода.

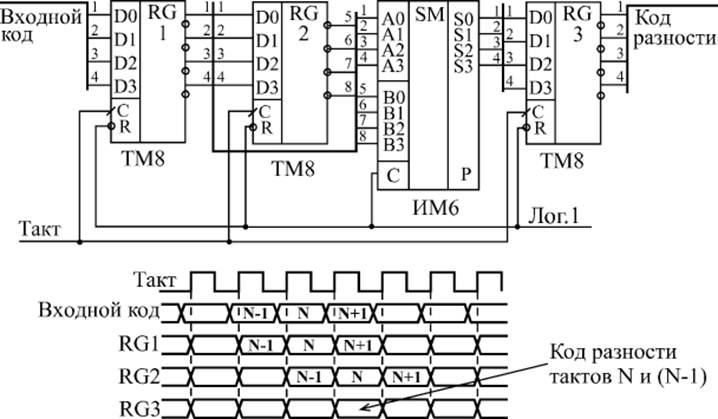

Для примера на рис. 8.4 показана схема вычисления разности двух последовательных значений входного кода. Такая задача возникает, в частности, при цифровой обработке аналоговых сигналов. Последовательные значения входного 4-разрядного кода сопровождаются тактовым сигналом, по положительному фронту которого производится запись в два последовательно включенных регистра. Когда на выходе регистра RG1 присутствует N-ое значение входного кода, на выходе регистра RG2 будет (N–1)-ое значение кода.

Рис. 8.4. Схема вычисления разности значений кодов в двух последовательных тактах

Подавая эти два кода с выходов регистров на 4-разрядный сумматор, включенный в режиме вычитания (см. рис. 8.4), мы получаем на выходе сумматора код разности между N-ым значением и (N–1)-ым значением. В данном случае очень удобен регистр ТМ8, имеющий инверсные выходы. Для обеспечения строго одновременного изменения выходных сигналов сумматора можно включить дополнительный выходной регистр RG3, тактируемый тем же самым общим тактовым сигналом. Правда, код разности при этом будет задержан на один такт.

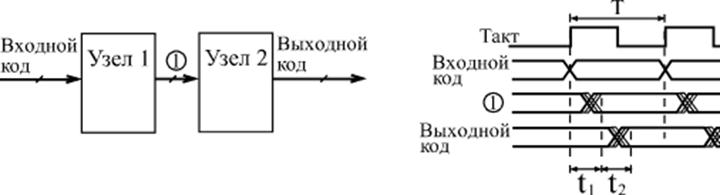

Пусть, например, последовательность входных кодов, следующих с периодом T, поступает на вход цепочки из двух узлов, производящих обработку или преобразование этих кодов (рис. 8.5). Узлы эти могут представлять собой комбинационные микросхемы (например, сумматоры) или более сложные устройства, включающие в себя микросхемы счетчиков или микросхемы памяти. Главное состоит в том, что выходные сигналы этих узлов выставляются не мгновенно, а в течение какого-то конечного времени, величина которого определяется внутренним строением узла. Пусть задержка установления выходного кода первого узла равняется t1, а задержка установления выходного кода второго узла составляет t2. Очевидно, что период T следования входных кодов не должен быть меньше, чем сумма этих двух задержек:

T> .

.

Рис. 8.5. Работа последовательной цепочки двух узлов

Иначе код на выходе цепочки может никогда не принять устойчивого значения, так как переходный процесс предыдущего такта будет сменяться переходным процессом следующего такта. То есть быстродействие узлов накладывает жесткое ограничение на тактовую частоту.

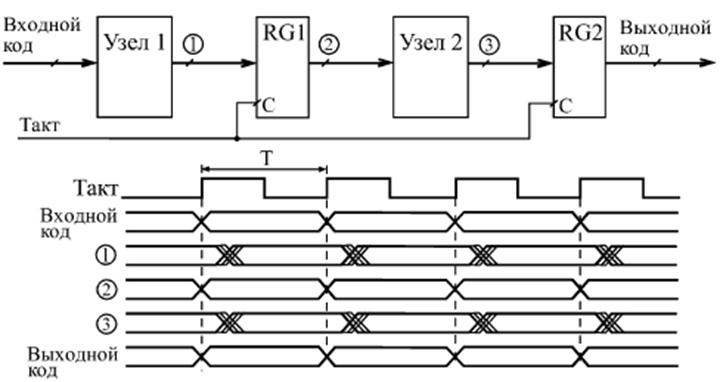

Однако можно обойти это ограничение, если воспользоваться принципом конвейера, заставить узлы работать не последовательно, а параллельно. Это достигается включением между узлами регистра, тактируемого входным тактовым сигналом. Еще один регистр целесообразно включить на выходе второго узла, что обеспечит длительность устойчивого кода на выходе всего устройства, равную длительности периода тактового сигнала Т (рис. 8.6). В результате ограничение на период тактового сигнала становится более мягким: Т не должно быть меньше максимальной из двух величин t1 и t2 с добавлением времени задержки регистра:

T>

Рис. 8.6. Конвейерная обработка с помощью регистров

Точно так же можно построить конвейер на любое количество последовательно включенных узлов. Конечно, в результате введения конвейера происходит задержка выполнения полной функции устройства на число тактов, равное числу введенных регистров. Однако в том случае, когда необходимо обрабатывать большие последовательности входных кодов, эта задержка наблюдается только один раз – в самом начале последовательности, а затем уже она не имеет значения.

Регистры могут также применяться в составе вычислителей, выполняя функцию накопителя результата вычисления. В данном случае мы уже имеем дело с более сложной обработкой информации, чем при чисто комбинационных схемах. С каждым тактом в регистре обновляется содержимое, являющееся результатом математической обработки входного кода и результата предыдущего вычисления.

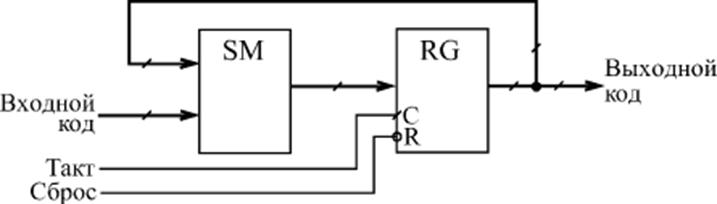

Рассмотрим пример такого вычислителя – накапливающий сумматор, применяющийся, например, в цифровых генераторах аналоговых сигналов. В самом названии схемы отражена ее функция: она суммирует и накапливает результат. Накапливающий сумматор (рис. 8.7) состоит из сумматора и выходного регистра, охваченных обратной связью.

Рис. 8.7. Структура накапливающего сумматора

На один вход сумматора подается код с выходов регистра, а на другой вход – входной код. В результате с каждым следующим фронтом тактового сигнала в регистр записывается код суммы входного кода с предыдущим содержимым регистра.

Например, если входной код равен 3, а в регистре записан код 6, то в следующем такте в регистр будет записан код 9 (то есть 6+3), в следующем такте – код 12 (то есть 9+3) и т.д. Получается, что на выходе накапливающего сумматора формируется равномерно увеличивающийся двоичный код, и шаг этого увеличения можно менять.

|

|

Дата добавления: 2014-01-03; Просмотров: 659; Нарушение авторских прав?; Мы поможем в написании вашей работы!