КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Код Грея

|

|

|

|

Код Грея

Серед незважених двійкових кодів спеціальне використання знаходять такі, в яких перехід до сусіднього числа супроводжується змінами тільки в одному розряді (коди з обмінною одиницею) - код Грея (табл.. 2.3).

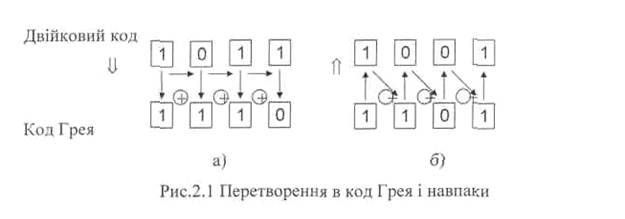

Перехід від двійкового коду до коду Грея і навпаки відбувається згідно правила (рис. 2.1., а): старші розряди співпадають, а будь-який наступний розряд

коду Грея дорівнює сумі по модулю 2 відповідного і попереднього розрядів двійкового коду (без урахування перенесення в старший розряд). При зворотному переході (рис. 2.1., б) старші розряди також співпадають, але кожен наступний розряд отримується в результаті додавання по модулю 2 отриманого попереднього розряду двійкового коду і відповідного розряду коду Грея.

Таблиця 2.3.

| Десяткові числа | Двійковий код | Код Грея |

2.1.6. Алфавітно - цифрові коди

Для відображення алфавітно - цифрової інформації в обчислювальній системі необхідно закодувати всі символи - цифри, літери, математичні та спеціальні знаки, управляючі та інші символи, що утворюють її алфавіт. Найбільш часто використовується стандарт ASCII (American Standart Code for Information Interchange), покладений в основу державного стандарту КОІ - 7 [4]. В табл.. 2.4. наведено 7-бітний код для обміну й обробки інформації (КОІ-7) в десятковій, вісімковій та шістнадцятковій системах числення. Стандартний код вміщує:

а) графічні символи (стовпчики з 3 по 8), до яких відносяться латинські літери, арабські цифри, знаки арифметичних і логічних операцій, розділові та інші знаки;

б) символи управління (1 та 2 стовпчики), які використовуються для управління апаратурою передачі даних, управління пристроями введення-виведення, а також поділу інформації на частини у відповідності з її логічним складом.

Кожен стовпчик таблиці ідентифікується шістнадцятковим числом, що відповідає першому символу в цьому стовпчику. Код будь-якого символу в таблиці визначається шістнадцятковим числом, що отримується додаванням номеру стовпчика і номеру стрічки. Наприклад, літера "К" знаходиться в стовпчику "40" і стрічці "В", тому її шістнадцятковий код дорівнює 4В.

Зліва від кожного символу вказаний код символу в інших системах числення: зверху - в десятковій, внизу - в вісімковій. Так символ "К" має код 75 в десятковій системі і 133 - в вісімковій.

КОІ-7

Таблиця 2.4.

| Шістн. число | Символи упр. | Графічні символи | ||||||||||||||

| ПУC | АР1 | 32 40 | _ | 64 100 | @ | P | 96 140 | ` | 112 160 | p | ||||||

| НЗ | 17 21 | СУ1 | 33 41 | ! | 65 101 | А | 81 121 | Q | 97 141 | а | 113 161 | q | ||||

| НТ | СУ2 | 34 42 | “ | 66 102 | В | 82 122 | R | b | 114 162 | r | ||||||

| КТ | СУ3 | # | С | S | с | s | ||||||||||

| КП | СУ4 | $ | 68 104 | D | 84 124 | T | 100 144 | d | 116 164 | t | ||||||

| КТМ | НЕТ | 37 45 | % | Е | 85 125 | U | e | 117 165 | u | |||||||

| ДА | 22 26 | СИН | 38 46 | & | 70 106 | F | V | 102 146 | f | 118 166 | v | |||||

| ЗВ | 23 27 | КБ | ‘ | 71 107 | G | 87 127 | W | 103 147 | g | 119 167 | w | |||||

| 8 10 | ВШ | 24 30 | АН | 40 50 | ( | Н | 88 130 | X | 104 150 | h | 120 170 | x | ||||

| 9 11 | ГТ | 25 31 | КН | 41 51 | ) | 73 111 | І | 89 131 | Y | 105 151 | i | 121 171 | y | |||

| А | 10 12 | ПС | ЗМ | * | : | 74 112 | J | 90 132 | Z | 106 152 | j | 122 172 | z | |||

| В | ВТ | 27 33 | АР2 | + | ; | 75 113 | K | [ | k | 123 173 | { | |||||

| С | 12 14 | ПФ | 28 34 | РФ | , | < | L | \ | l | | | ||||||

| D | 13 15 | ВК | РГ | 45 55 | - | = | 77 115 | M | ] | 109 155 | m | 125 175 | } | |||

| Е | 14 16 | ВИХ | 30 36 | РЗ | 46 56 | . | > | 78 116 | N | 94 136 | ^ | n | 126 176 | ~ | ||

| F | ВХ | РЕ | 47 57 | / | ? | 79 117 | O | _ | 111 157 | o | 127 178 | ЗБ |

2.2. Логічні основи цифрової техніки

2.2.1. Основні положення алгебри логіки

Аналіз і синтез логічних ланцюгів виконується за допомогою математичного апарата алгебри логіки або булевої алгебри [3, 5, 6, 7], в якій змінні можуть приймати тільки одне з двох значень: 0 або 1. Над змінними можуть виконуватись три основні дії: логічне додавання, логічне множення і логічне заперечення, що відповідає логічним функціям АБО, І, НІ.

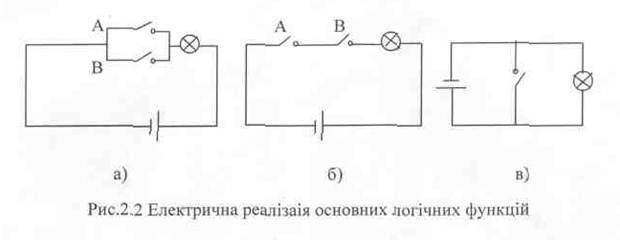

Логічне додавання (диз’юнкція) позначається символом "+" або V (перша літера латинського слова vel - або). В якості прикладу ланцюга, що реалізує функцію АБО, можна навести паралельне з'єднання замикаючих контактів декількох реле (рис. 2.2., а). Ланцюг, в яке входять ці контакти, буде замкнутий, якщо спрацює хоча б одне реле.

Таким чином, логічна сума дорівнює одиниці тоді, коли дорівнюють одиниці один або кілька додатків:

0+0=0; 0+1=1; 1+0=1; 1+1+....+1=1

Найбільш наглядно функція перетворення характеризується таблицею, в стрічках якої кожній комбінації вхідних змінних X відповідають значення вихідної змінної Y. Її називають таблицею істинності (табл. 2.5).

Основні логічні функції

| Таблиця2.5. |

| X1 | Х2 | АБО | І | НІ |

| Y = Х1+Х2 | Y = Х1*Х2 |  Y = Х1 Y = Х1

| ||

Логічне множення (кон'юнкція) позначається крапкою або в булевих формулах ніяк не позначається. Функцію І реалізують, наприклад, з'єднані послідовно замикаючі контакти декількох реле (рис. 2.2., б). Ланцюг в цьому випадку буде замкнутий тільки тоді, коли спрацюють всі реле:

| 0*0=0; 0*1=0; |

| 1*0=0; |

| 1*1=1. |

Логічне заперечення (інверсія) позначається лінією над позначенням аргументу. Моделлю, що реалізує функцію НІ, може бути схема на рис. 2.2., в, або розмикаючий контакт реле. При спрацюванні реле, ланцюг, в який входить такий контакт, розмикається. Таким чином, інверсія одиниці дорівнює нулю, а подвійна інверсія не змінює змінної:

| |||

| |||

0 = 1; 1 = 0; 0 = 0; 1 = 1

0 = 1; 1 = 0; 0 = 0; 1 = 1

Кон'юнкцію, диз’юнкцією і інверсією можна виразити будь-які більш складні функції; наведені в табл. 2.6.

Логічні функції

Таблиця 2.6.

| X1 | Х2 | Функція Шефера | Функція Пірса | Суми по модулю 2 |

Y = Х1*Х2 Y = Х1*Х2

|  Y=Х1+Х2 Y=Х1+Х2

| Y = X Х2 | ||

На основі вищевикладеного можна записати:

а+0=а; а+1=1; а+а+.....+а=а; а+а=1

а+0=а; а+1=1; а+а+.....+а=а; а+а=1

а*0=0; а*1=а; а*а*.....*а=а; а*а=0; а=а

а*0=0; а*1=а; а*а*.....*а=а; а*а=0; а=а

2.2.2 Основні закони алгебри логіки

Переміщувальний закон:

a+b=b+a Сполучний закон:

(а + b) + с = a+ (b + с); (а * b) * с = а * (b*c) Розподільний закон:

а * (b + c) = a * b + a * c; a + b * c = (a + b)*(a + c)

Закон поглинання:

a + a * b = a(1 + b) = a; a(a + b) = a + a * b = a;

Закон склеювання:

Закон склеювання:

a * b + a * b = a; (a + b)(a + b) = a;

Закон заперечення:

Закон заперечення:

а +b = а * b; а * b = а + b

а +b = а * b; а * b = а + b

а + b = а * b а * b = а + b

а + b = а * b а * b = а + b

Закон заперечення (його часто називають правилом де Моргана), справедливий для будь - якого числа змінних.

Закон заперечення (його часто називають правилом де Моргана), справедливий для будь - якого числа змінних.

а + b +..... + z = а * b *.....* z;

а + b +..... + z = а * b *.....* z;

а * b *.....* z = а + b +.....+z;

а * b *.....* z = а + b +.....+z;

2.2.3. Функціональна повнота

Система функцій, суперпозицією яких може бути наведена будь-яка функція, називається функціональною повнотою. З переглянутого вище, комбінація найпростіших функцій - кон'юнкції, диз’юнкції і інверсії, являється функціонально повною. Наприклад: функцію а * b + а * b можна реалізувати за допомогою двох елементів НІ (вони потрібні, щоб отримати інверсії а і b), двох елементів І, необхідних для того, щоб отримати логічне множення а*b і а*b, елемент АБО, що додасть одержані значення.

Система функцій, суперпозицією яких може бути наведена будь-яка функція, називається функціональною повнотою. З переглянутого вище, комбінація найпростіших функцій - кон'юнкції, диз’юнкції і інверсії, являється функціонально повною. Наприклад: функцію а * b + а * b можна реалізувати за допомогою двох елементів НІ (вони потрібні, щоб отримати інверсії а і b), двох елементів І, необхідних для того, щоб отримати логічне множення а*b і а*b, елемент АБО, що додасть одержані значення.

Функціонально повні схеми можуть складатися з набору елементів, що реалізують логічні функції, відмінні від найпростіших. Функціонально повні схеми можуть складатись з елементів тільки одного типу, наприклад, реалізуючих функцію І-НІ або АБО-НІ. Переглянемо можливість побудови логічних ланцюгів, що реалізують найпростіші функції на основі елемента І-НІ. Функцію НІ, тобто інверсію змінної, можна реалізувати, якщо сигнал, що відповідає цій змінній, подати на один з входів ланцюга І-НІ, а на всі інші входи подати постійний сигнал, відповідний одиниці: а* 1 *...... * 1 = а. Для створення ланцюгу І достатньо ввімкнути послідовно ланцюг І-НІ і інвертор: а*b = а*b. Ланцюг АБО будується в відповідності з правилом де Моргана: а*b=а+b. Таким чином, ланцюги І-НІ дозволяють реалізувати інверсію, кон'юнкцію та

Функціонально повні схеми можуть складатися з набору елементів, що реалізують логічні функції, відмінні від найпростіших. Функціонально повні схеми можуть складатись з елементів тільки одного типу, наприклад, реалізуючих функцію І-НІ або АБО-НІ. Переглянемо можливість побудови логічних ланцюгів, що реалізують найпростіші функції на основі елемента І-НІ. Функцію НІ, тобто інверсію змінної, можна реалізувати, якщо сигнал, що відповідає цій змінній, подати на один з входів ланцюга І-НІ, а на всі інші входи подати постійний сигнал, відповідний одиниці: а* 1 *...... * 1 = а. Для створення ланцюгу І достатньо ввімкнути послідовно ланцюг І-НІ і інвертор: а*b = а*b. Ланцюг АБО будується в відповідності з правилом де Моргана: а*b=а+b. Таким чином, ланцюги І-НІ дозволяють реалізувати інверсію, кон'юнкцію та

диз’юнкцію, а відповідно на їх основі можна побудувати ланцюги для реалізації будь-яких складних функцій.

Елемент АБО-НІ також дозволяє реалізувати найпростіші функції. Для одержання інверсії однієї змінної достатньо подати сигнал, що відповідає цій змінній, на один вхід ланцюга АБО-НІ, а на інші входи - рівні логічного нуля. Функція АБО може бути реалізована інвертуванням вихідного сигналу ланцюгу АБО-НІ. Функція І реалізується за допомогою елементів АБО-НІ на основі

закону заперечення а + b=а*b.

закону заперечення а + b=а*b.

Можливість реалізації найпростіших логічних функцій свідчить про функціональну повноту логічних елементів І-НІ та АБО-НІ.

2.2.4. Стандартні форми

Будь-яку логічну функцію F(Х1,...., Хn) можна подати в досконалій диз'юнктивній нормальній формі (ДДНФ):

(2.2)

(2.2)

або в досконалій кон'юнктивній нормальній формі (ДКНФ):

(2.3)

(2.3)

де F(Аi) - значення функції (0 або 1), яке вона приймає на наборі Аi; Сi1 = Х1* Х2*......* ХN - мінтерм;

Сi0 = Х1 V Х2 V...... V ХN - макстерм.

Подання логічної функції проілюструємо згідно заданої таблиці відповідності (табл. 2.7)

Таблиця відповідності

Таблиця 2.7.

| аі | F(Аi) | ||

| Х1 | Х2 | Х3 | Х4 |

Для подання логічної функції в ДДНФ достатньо використовувати тільки ті набори змінних Аi, на яких F(Аi)=1, так як при F(Аi;)=0 кон'юнкція Сi1 *F(Аi)=0. Для подання в ДКНФ використовують ті набори змінних Аi, на яких F(Аi)=0, так як при F(Аi)=1 диз'юнкція [Сi0 V F(Аi)]=1, незалежно від значення Сi0. Через

|

|

ДДНФ:

ДДНФ:ДДНФ:

2.2.5 Синтез комбінаційних ланцюгів

Комбінаційні логічні ланцюги - це такі ланцюги, вихідні сигнали яких не залежать від передісторії і однозначно визначаються сигналами, присутніми на їх входах в даний момент часу. Інакше комбінаційні схеми - це ланцюги, в яких відсутні елементи пам'яті.

Синтез комбінаційних ланцюгів проводиться в такій послідовності. Спочатку складається таблиця функціонування логічного ланцюгу - таблиця істинності, виходячи з якої записується логічна функція, після чого проводиться її мінімізація і перетворення до вигляду, зручного до реалізації на логічних елементах заданого типу.

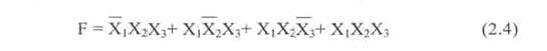

Розглянемо більш докладно процес синтезу комбінаційних ланцюгів на прикладі. Нехай необхідно побудувати мажоритарний елемент (елемент голосування) на три входи, тобто такий елемент, в якого сигнал на виході дорівнює одиниці тоді, коли більшість вхідних сигналів дорівнює одиниці.. Складемо спочатку таблицю істинності (табл. 2.8).

Таблиця істинності

Таблиця 2.8.

| N | X1 | Х2 | Х3 | F |

| Для мінімізації функції (2.4) використаємо основні закони алгебри логіки: |

Користуючись табл. 2.8, запишемо логічну функцію, для чого подамо її у вигляді суми логічних добутків (ДДНФ), що відповідають тим стрічкам табл. 2.8, для яких функція Р дорівнює одиниці:

Якщо використати для побудови логічного ланцюга елементи І-НІ, то необхідно перетворити функцію до вигляду

Як видно, отриманий кінцевий вираз явно простіше початкового.

2.2.6. Мінімізація за допомогою діаграм Вейча (або карт Карно)

В переглянутому прикладі для мінімізації функції ми використали шлях алгебраїчних перетворень. Цей шлях універсальний, але кінцевий результат залежить від кваліфікації фахівця, що проводить мінімізацію. Для функцій, що мають не більше п'яти-шести аргументів, зручно проводити мінімізацію за допомогою діаграм Вейча. Цей шлях мінімізації гарантує при виконанні невеликої кількості формальних правил найбільш простий кінцевий вираз.

Попередньо потрібно представити функцію в ДДНФ формі, заповнити прямокутну таблицю, ставлячи 1 в клітинки таблиці при рівності одиниці, відповідних кон’юнкцій початкової функції, і 0 в решту клітинок таблиці.

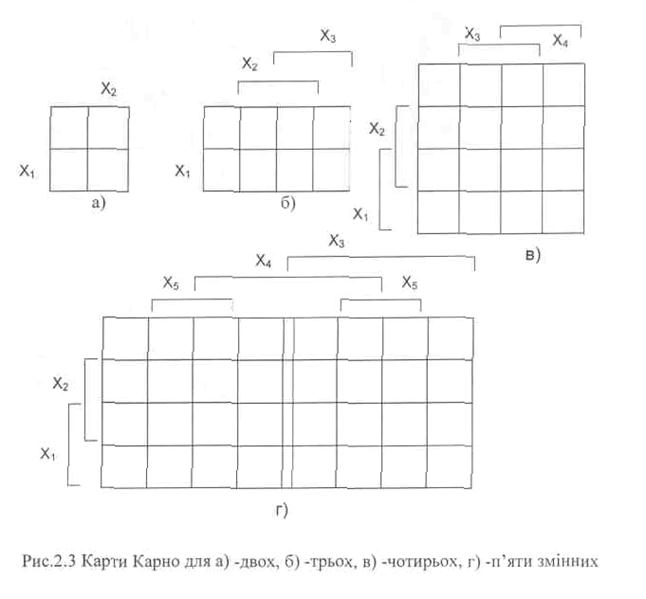

На рис. 2.3 подані карти Карно для функцій декількох змінних.

В заповненій таблиці обводять контурами всі одиниці, а потім записують мінімізовану функцію в вигляді суми логічних добутків, що описують ці функції. В середині контуру повинні знаходитись тільки клітинки, заповнені одиницями, число яких повинно бути цілою степінню числа 2, а одні і ті ж клітинки можуть входити в декілька контурів.

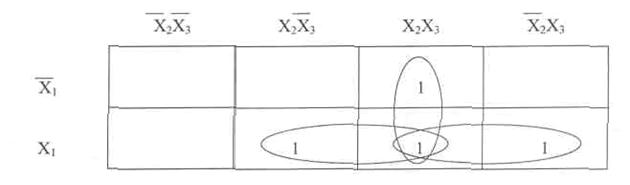

Мінімізуємо за допомогою карти Карно (табл. 2.9) функцію трьох змінних (2.4).

Мінімізація функції

Таблиця 2.9.

В даному випадку всі одиниці в табл. 2.9 можна охватити трьома контурами. Виписавши позначення цих контурів, отримаємо мінімізовану функцію

F = X1X2 + +X1X3 + X2X3

2.3. Елементи цифрової техніки 2.3.1. Основні типи цифрових ІС

Під цифровою електронікою ми маємо на увазі такі схеми, для кожної точки яких можна визначити, як правило, два стани: 0 і 1. Наприклад: 1 - замкнутий контакт, 0 - розімкнутий контакт; 1 - високий рівень; 0 - низький рівень. В якості параметра вибирають напругу, точні значення якої в цифровій електроніці не грають ролі. Задача заключається в тому, щоб розпізнати тільки рівні напруги (рис. 2.4)

В зв'язку з цим для кожного ряду цифрових мікросхем визначені допустимі значення високого та низького рівнів напруги. На рис. 2.5 наведені значення логічних рівнів для трьох широко розповсюджених рядів цифрових елементів:

- ТТЛ - транзисторно-транзисторної логіки;

- ЕЗЛ - емітерно-зв'язаної логіки;

- КМДН - логіки на комплементарних транзисторах зі структурою метал-діелектрік-напівпровідник.

Такі широкі діапазони вибрані для того, щоб виробник мікросхеми мав у своєму розпорядженні певний допуск, в межах якого параметри схеми можуть відхилятися за рахунок зміни температури, навантаження, напруги живлення а також під дією шуму.

В даний час в апаратурі можна зустріти різні варіанти мікросхем ТТЛ, перші розробки яких (серії К134, К155) активно замінюються на мікросхеми ТТЛШ, що мають у внутрішній структурі переходи з бар'єром Шоткі (серії К531, К555). Використання нових інтегральних транзисторів зі структурою, що носить назву "Ізопланар-1" з окисною (а не р-n переходами) ізоляцією між сусідніми транзисторами, дозволило перейти до перспективних ІС (КР 1531, КР 1533).

Більш розповсюдженими серіями КМДН ІС є: К 176, К 561, 564, КР 1561; ЕЗЛ ІС К 500, 700, К 1500.

При стиковці цифрових приладів, побудованих на мікросхемах різного типу, використовують перетворювачі (транслятори) рівнів логічних сигналів.

2.3.2. Основні параметри цифрових ІС

До основних параметрів відносяться рівні вхідних і вихідних струмів та напруги, значення потужності споживання, середній час затримки сигналу, який визначає швидкодію схеми, навантажувальна здатність, завадостійкість, надійність та ін. [8]. Кількісно навантажувальна можливість оцінюється коефіцієнтом розгалуження по виходу, тобто кількістю одиночних навантажень, котрі можливо одночасно підключати до виходу мікросхеми. Одиночним навантаженням вважається вхід основного логічного елементу даної серії. Однак при підвищенні навантажувальної здатності погіршуються інші параметри ІС, наприклад, збільшується потужність споживання. У зв'язку з цим у складі різних схем присутні елементи з підвищеною навантажувальною здатністю, тобто навантажувальна здатність в кілька разів більше, ніж у основних елементів. Для характеристики цифрових мікросхем використовують також параметр, який називається енергією переключення

An = P*tэ (2.5)

де Р - середня потужність споживання;

tэ - середній час затримки розповсюдження сигналу.

У таблиці 2.10. подані типові значення параметрів елементів різних серій. Порівнювальний аналіз показує, що найвища швидкодія у елементів ЕЗЛ та ТТЛШ, що дозволяє їм працювати з тактовою частотою 10-100 МГц (ЕЗЛ) та 5-10 МГц (ТТЛШ). Мінімальну потужність споживання мають елементи КМДН - 0.003-0.02 мВт/ел. Ці елементи мають саму низьку енергію переключення.

Типові значення параметрів елементів різних серій

Таблиця 2.10.

| Параметри | Типові значення параметрів елементів | ||||

| ТТЛ | ТТЛШ | ЕЗЛ | КМДН | ||

| Рівні вхідних струмів | I0вх, мА | -1.6 | -2.0 | 0.5 мкА | -0.1 мкА |

| I1вх, мА | 0.04 | 0.05 | 0.3 | 0.1 мкА | |

| Рівні вихідних напруг | U0вих, мА | ≤0.4 | ≤0.5 | ≤-1.6 | ≤1.5 |

| U1вих, мА | ≥2.4 | ≥2.7 | ≥ -0.98 | ≥3.5 | |

| Напруга живлення | Uж, В | 5.0 ± 10% | 5.0 + 10% | -5.2 + 10% | 5...15 + 10% |

| Потужність споживання | Р, мВт | 1... 10 | 2...20 | 25...40 | 0.003... 0.02 |

| Час затримки | τ3, нс | 30-10 | 10-3 | 2-0.75 | 200-50 |

| Енергія переключення | Ап, пДж | 30-100 | 20-60 | 50-30 | 0.6-1 |

| Коефіцієнт розгалужень по виходу | Кроз | ≤ 100 |

2.3.3. ЛОГІЧНІ ЕЛЕМЕНТИ

Логічний елемент - це електронний пристрій, що реалізує одну з логічних функцій. У склад серій входить велика кількість логічних елементів. На принциповій схемі логічний елемент відображають прямокутником, всередині якого ставиться зображення показника функції. Лінії з лівої сторони прямокутника показують входи, з правої - виходи елемента. Графічне

зображення більш поширених вентилів подані у таблиці 2.11 (інверсні входи і виходи позначаються кружками).

Найбільш використовувані вентилі

Таблиця 2.11.

Продовження табл.2.11.

Функціональні можливості логічних елементів та їх фізичні параметри також залежать від вихідного каскаду елемента. Більш часто використовуються три типи вихідних каскадів.

Функціональні можливості логічних елементів та їх фізичні параметри також залежать від вихідного каскаду елемента. Більш часто використовуються три типи вихідних каскадів.

На малюнку 2.6, а поданий логічний елемент зі стандартним виходом.

Він складається з двох послідовно ввімкнених транзисторів, якими керує логічна частина елемента. Один з транзисторів завжди відкритий, а другий-закритий. Відкриті транзистори, маючи малий опір, швидко перезаряджають ємність навантаження і паразитну ємність монтажу, через це елементи такого типу знайшли широке використання.

В логічному елементі з відкритим колектором (рис. 2.6., б) у якості вихідного каскаду використовується транзистор, колектор якого не підключений до навантаження. Виходи таких елементів повинні бути підключені за допомогою зовнішнього резистору до джерела живлення.

На рис. 2.6, в поданий логічний елемент з трьома станами виходу: логічний елемент має управляючий вхід, одне з значень сигналу на якому переводить вихідні транзистори в закритий стан, що відповідає високоімпедансному стану виходу (сотні кілоом). Елементи з трьома станами розроблені спеціально для використання у якості вихідного управляючого буфера для підключення цифрових блоків до магістралей.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 726; Нарушение авторских прав?; Мы поможем в написании вашей работы!