КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Ядерные процессоры Istanbul

|

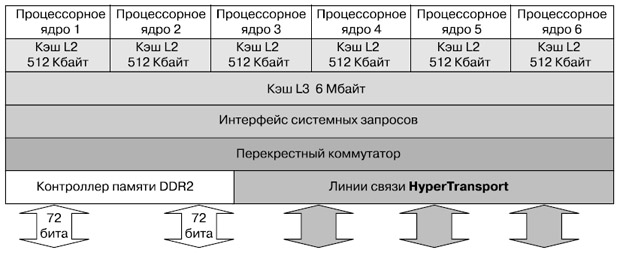

Структура шестиядерного процессора Istanbul приведена на рис. 23.

Рис. 23. Структура шестиядерного процессора Istanbul

Структура ядер процессора Istanbul, количество каналов оперативой памяти, контроллеров интерфейса Hyper Transport такие же как и у 4-х ядерного процессора Shanghai.

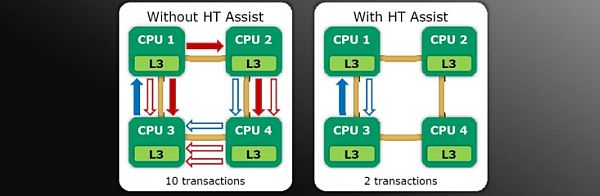

Реализованная в процессоре технология HT Assist, обеспечивает (рис. 24) оптимизацию потоков данных между процессорными ядрами.

Рис. 24. Преимущества технологии HT Assist.

Механизм действия технологии выглядит следующим образом. Когда одному кристаллу многопроцессорной системы необходимо обработать определенный массив данных, то сначала проводится процедура проверки, не присутствует ли необходимая информация в кэш-памяти ядер соседних процессоров. Если дан отрицательный ответ, то осуществляется чтение данных из оперативной памяти. В случае МВС, оснащенной сразу четырьмя процессорами, для проведения подобной проверки может потребоваться до десяти транзакций. Технология HT Assist как раз и призвана снизить их количество до минимума - каждый из процессоров теперь "знает", куда необходимо обратиться за порцией необходимых данных, и максимальное число транзакций снижается до двух. Разумеется, приходится занимать определенный объем кэш-памяти под хранение сервисной информации - в случае HT Assist для этого выделяется 1 Мб кэш-памяти третьего уровня для каждого из процессоров. Но повышение производительности системы вполне оправдывает затраченные средства.

Технология оптимизированной виртуализации AMD Virtualization™ (AMD-V™) позволяет добиться эффективной работы виртуальных машин и облегчает миграцию. AMD-V поддерживает виртуализацию на уровне ввода-вывода и возможности непосредственного управления устройствами виртуальной машиной. Это позволяет увеличить производительность благодаря прямому назначению устройств гостевым ОС, а также повысить изоляцию и степень защиты виртуальных машин.

|

|

|

Примеры структур несимметричных МВС с процессорами линии Opteron Barcelona, Shanghai, Istanbul

Процессоры Barcelona, Shanghai, Istambul с тройным интерфейсом HyperTransport позволяли создавать несимметричные 4-х и 8-ми сокетные вычислительные системы. Пример четырехсокетной вычислительной системы с процесорами Barcelona приведен на рис. 25, а 8-ми сокетной – на рис. 26.

Рис. 25. Структура 4-хсокетной вычислительной системы

Рис. 26. Структура 8-ми сокетной вычислительной системы

Сравнение структур МВС с процессорами Barcelona, Shanghai, Istanbul с МВС с процессорами со структурой Nehalem

Так как в микросхемах процессоров Barcelona, Shanghai, Istanbul имеется только три порта HT, то в 4-х сокетной МВС при обращении в наиболее удаленную оперативную память необходимо выполнить 2 перехода, вместо одного в идеальном варианте.

В микросхемах процессоров со структурой Nehalem имеется 4 порта QPI (аналог портов HT) и при обращении в наиболее удаленную оперативную память необходимо выполнить 1 переход (идеальный вариант).

В восьмисокетных МВС с процессорами Barcelona, Shanghai, Istanbul при обращении в наиболее удаленную оперативную память необходимо выполнить 3 перехода, в то время как в системах с процессорами со структурой Nehalem - только 2 перехода.

В процессорах Barcelona, Shanghai, Istanbul реализован только двухканальный контроллер оперативной памяти стандарта DDR2, в то время как в процессорах со структурой Nehalem имеется трехканальный контроллер оперативной памяти стандарта DDR3. Оперативная память стандарта DDR3 обеспечивает большую пропускную способность по сравнению с оперативной памятью стандарта DDR2.

В n -ядерной МВС с процессорами со структурой Nehalem одновременно может выполняться 2n потоков, так как в каждом ядре имеется технология Hyper Threading (в одном физическом ядре выполняются одновременно 2 потока).

|

|

|

В процессорах Barcelona, Shanghai, Istanbul отсутствует технология подобная технологии Hyper Threading. Это означает, что в n -ядерной МВС с одновременно может выполняться только n потоков.

Конечно, технология Hyper Threading не обеспечивает удвоения производительности отдельно взятого ядра. В зависимости от типов выполняемых потоков реальное ускорение может составлять от одного до несколько десятков процентов. Однако, даже такое ускорение обеспечивает превосходство МВС с процесорами линии Nehalem.

|

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 428; Нарушение авторских прав?; Мы поможем в написании вашей работы!