КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тема лекции 5. Запоминающие устройства (ЗУ). Иерархическая структура ЗУ. Статическое и динамическое ЗУ. Структура ЗУ. Постоянное и программируемые ЗУ

|

|

|

|

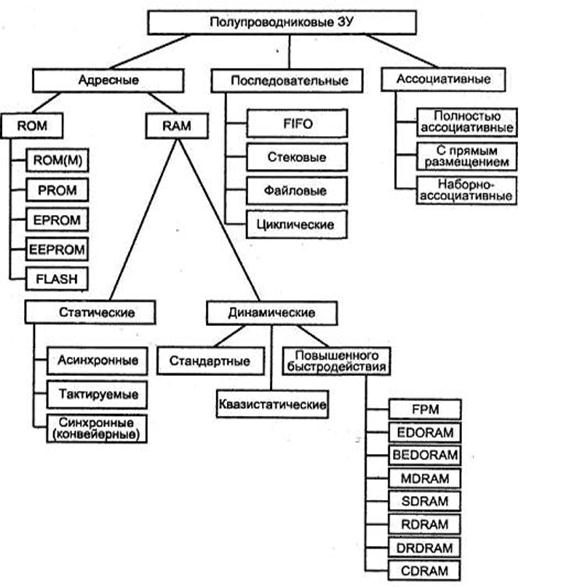

Память может быть внутренней и внешней. Внешней называют память на магнитных, оптических дисках, лентах и т.п. Внутренняя память выполняется, чаще всего, на микросхемах. Внутренняя или основная память может быть двух типов: оперативное запоминающее устройство (ОЗУ) или ЗУ с произвольной выборкой (ЗУПВ) и постоянное ЗУ (ПЗУ). ОЗУ, кроме того, обозначается - (RAM, Random Access Memory), а ПЗУ - (ROM, Read Only Memory). Получила также распространение Флэш(Flash) память, имеющая особенности и ОЗУ и ПЗУ и энергонезависимая память (Nonvolatile - NV) на батарейках. Последнее название условно, так как ПЗУ и Флэш память, также энергонезависимы. В ОЗУ коды в соответствии с решаемыми задачами постоянно изменяются и полностью пропадают при выключении питания. В ПЗУ хранятся управляющие работой ЭВМ стандартные программы, константы, таблицы символов и другая информация, которая сохраняется и при выключении компъютера. ОЗУ подразделяются на статическую память (SRAM), динамическую (DRAM), регистровую (RG). ПЗУ могут быть: масочными - запрограммированными на заводе изготовителе (ROM), однократно-программируемыми пользователем ППЗУ (PROM или OTP), многократно-программируемыми (репрограммируемыми) пользователем РПЗ У с ультрафиолетовым стиранием (EPROM) или c электрическим стиранием (EEPROM). Широкое распространение нашли также программируемые логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т.д.) с большим выбором логических элементов и устройств на одном кристалле.

Классификация ЗУ. ЗУ классифицируются по ряду признаков. По назначению они разделяются на:

- внешние ЗУ (ВЗУ), которые предназначены для хранения больших объемов информации с емкостью до нескольких десятков или сотен Мегабайт;

|

|

|

- оперативные ЗУ (ОЗУ), которые служат для хранения оперативной информации, емкость которых достигает несколько десятков миллионов байт;

- сверхоперативных ЗУ (СОЗУ), которые служат для хранения интенсивно используемой на текущем этапе решения задачи информации. Быстродействие СОЗУ соизмеримо с быстродействием процессора;

- буферные ЗУ (БЗУ), которые используются для временного хранения данных в целях согласования скоростей работы различных устройств (например, СОЗУ и ОЗУ, процессор и ОЗУ, канал и ОЗУ и т.п.).

По методам размещения и способу поиска информации различают адресную, магазинную (стековую) и ассоциативную память (или ассоциативное ЗУ АЗУ).

Общая классификация ЗУ приведена на рис 5.1.

Рис. 5.1. Классификация ЗУ

Адресная память. В простейшей ЭВМ и ее микропрограммном устройстве управления слова информации (данные, команды и микрокоманды) размещались в ячейках памяти разной длины и отыскивались по адресу (номеру) этих ячеек. Подобный способ размещения и поиска информации чаще всего использовали и используют при организации основной памяти ЭВМ. Но несмотря на то, что разные ЭВМ могут обрабатывать слова разной длины, основная их память обычно имеет байтовую организацию.

Стековая память. Она состоит из ячеек, связанных друг с другом разрядными цепями передачи слов. Обмен информацией между процессором и стековой памятью (стеком) всегда выполняется только через верхнюю ячейку - вершину стека. При записи нового слова (команды, числа, символы и т.п.) все ранее записанные слова сдвигаются на одну ячейку вниз, а новое слово помещается на вершину стека. Считывание возможно только с вершины стека и производится с удалением (после считывания все слова сдвигаются на одну ячейку вверх) или без удаления считываемого слова. Такую память часто называют памятью, работающей по принципу "последним вошел первым вышел" или типа LIFO (LAST-IN FIRST-OUT).

|

|

|

Стековая память очень удобна для упрощенного решения многих задач, возникающих при работе с подпрограммами, обслуживании прерываний, построении трансляторов и т.д. В качестве стека можно использовать часть адресной памяти, что позволяет менять емкость стека и экономит аппаратуру. В некоторых машинах также используется и внешний стек.

Ассоциативная память. Этот тип памяти обеспечивает возможность выбора информации по ее содержимому (по ассоциативному признаку или дескриптору). При использовании ассоциативной памяти время поиска резко сокращается. При чтении ассоциативные признаки опроса и код маски записываются соответственно в специальные регистры. Поиск производится по содержанию разрядов этих регистров. При совпадениииниц РгСВП, т.е. по одному коду этих регьстров вся информация может быть считана из нескольких ячеек основной памяти.

По способу выборки информации различают два основных типа запоминающих устройств: с произвольной выборкой и последовательной выборкой. Во-первых, время доступа к заданному слову не зависит от месторасположения этого слова в памяти, а во-вторых, зависит.

Память с произвольным доступом к словам, обычно называют оперативной памятью или оперативным запоминающим устройством (ОЗУ). Есть более дешевые элементы памяти, в которые единожды записывают 0 или 1 (при изготовлении или перед установкой в создаваемую ЭВМ). ЗУ, построенные на таких элементах, соответственно называют ПЗУ (постоянные запоминающие устройства) и ППЗУ (программируемые постоянные запо-минающие устройства). Одним из вариантов ППЗУ является СППЗУ (стираемое ППЗУ). Содержимое СППЗУ можно стереть в специальной установке, а затем вновь заполнить информацией.

В зависимости от типа ЗУ элементом памяти (ЭП) может быть: триггер, миниатюрный конденсатор, транзистор с "плавающим затвором", плавкая перемычка (или ее отсутствие). Упорядоченный набор ЭП образует ячейку памяти (ЯП).

ЗУ в основном, характеризуются емкостью и быстродействием. Емкость - максимальное количество единиц информации (машинных слов определенной разрядности или байтов), которые одновременно могут храниться в ЗУ. Временными параметрами ЗУ, по которым оценивается быстродействие, являются цикл записи и цикл считывания. Цикл считывания и цикл записи определяются как время с момента выдачи процессором адреса требуемой ячейки памяти и сигнала на считывание или запись до того момента, когда заканчиваются все действия, обязанные с выполняемой операцией, и память будет готова реализовать следующую операцию.

|

|

|

Полупроводниковые ЗУ с произвольной выборкой. Достижения в развитии полупроводниковых интегральных микросхем привели к созданию БИС полупроводниковых ЗУ. В настоящее время на основе БИС ЗУ строятся управляющая, оперативная память и БЗУ. Разрабатываются полупроводниковые ЗУ для использования их во внешних запоминающих устройствах. Запоминающий элемент в полупроводниковых ЗУ строится на биполярных и МОП транзисторах.

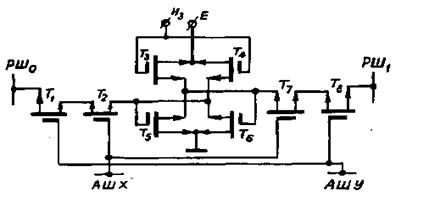

Рис.5.2. Запоминающий элемент на МОП транзисторах

В настоящее время промышленностью изготавливаются два основных типа ЗЭ: статические и динамические. Пример схемы статического ЗЭ на МОП транзисторах показан на рис. 5.2. ЗЭ состоит из триггера, реализованного на транзисторах T5 и T6. Транзисторы Т1, T2, Т7 и Т8 являются управляющими, посредством которых производится выборка ЭП по адресным шинам X (АШХ) и У (АШУ) подачей напряжений Uax, и Uay. Запись кода "0" и "1" осуществляется подачей напряжений Upo и Up1 на разрядные шины РШ0 и РШ1 при наличии напряжений выборки Uax и Uay. Считывание осуществляется также подачей напряжений выборки Uax и Uay. Состояние ЭП снимается с РШ0 и РШ1. Транзисторы Т3 и Т4 являются нагрузочными.

К памяти с последовательной выборкой относят внешние запоминающие устройства (ВЗУ).

Иерархическая организация ЗУ. Пользователи ЭВМ хотели бы иметь в своем распоряжении ЗУ неограниченной емкости и высокого быстродействия. Несмотря на непрерывное увеличение емкости и быстродействия, эти характеристики с учетом ограничений на стоимость ЗУ остаются противоречивыми. Поэтому в ЭВМ применяют несколько типов ЗУ, организованных по иерархическому многоуровневому принципу (рис.5.2).

|

|

|

Как видно из рисунка 5.3 в иерархии ЗУ можно выделить четыре основных типа ЗУ: сверхоперативные (СОЗУ), БЗУ типа КЭШ память, ОЗУ и ВЗУ на магнитных дисках (ЗУ МД) и на магнитных лентах (ЗУМЛ). СОЗУ строится на полупроводниковых интегральных схемах - регистрах.

Быстродействие СОЗУ составляет единицу наносекунд. БЗУ служит для временного хранения команд и операндов, интенсивно используемых на текущем этапе решения задач. Буферная память обычно "скрыта" от программиста, он не может ее адресовать и даже не знает об ее существовании. Поэтому такая память получила название Кэш-память (КЭШ от английского САСН - тайник).

Рис.5.3. Иерархическая структура ЗУ

При обращении процессора к ОП для считывания, в КЭШ передается блок информации, в котором находится нужное слово. При этом происходит опережающая выборка, т.к. высока вероятность того, что ближайшие обращения будут происходить к словам этого же блока. Это приводит к значительному уменьшению среднего времени, затрачиваемого на выборку данных.

Эффективность КЭШ зависит от ее емкости, размера блока, соотношения времени считывания слова из КЭШ (tКЭШ) и блока из ОЗУ (tОЗУБЛ). Обычно tКЭШ < tОЗУБЛ, и с увеличением частоты обращения КЭШ среднее время, затрачиваемое на выборку слов, уменьшается.

Постоянные запоминающие устройства. Постоянные запоминающие устройства служат для хранения постоянных или редко изменяющихся массивов информации. В ПЗУ в процессе работы осуществляется только считывание хранимой информации.

В настоящее время наибольшее распространение получили ПЗУ с транзисторными элементами памяти (биполярными и на МОП транзисторах). ПЗУ на МОП транзисторах имеет высокую плотность компонентов, и время обращения составляет 10-300 нс.

По способу записи информации различают ПЗУ, программируемые маской и программируемые пользователем. В ПЗУ, программируемых маской, информация записывается при изготовлении с помощью фотошаблонов. В ПЗУ, программируемых пользователем, информация записывается пользователем путем выжигания перемычек или пробоем р-п переходов под действием приложенного электрического напряжения или тока. Микросхемы ПЗУ, программируемые пользователем, подразделяются на ПЗУ с одноразовым программированием и репрограммируемые. В ПЗУ с одноразовым программированием информация, записанная в нем,не может меняться, и в режиме выборки происходит только ее считывание. В программируемом ПЗУ информации может быть перезаписана многократно. В настоящее время существуют несколько типов репрограммируемых ПЗУ, где в одних запись и стирание информации производится электрическим способом, а в других запись осуществляется электрическим, а стирание путем облучения ультрафиолетовыми лучами.

Рис.5.4. Запоминающий элемент ПЗУ

На рис. 5.4 показаны диодный и транзисторный элементы памяти ПЗУ. Выбор требуемого ЭП производится подачей сигнала выборки на адресную шину 5.4 а. При этом единичный уровень установится на тех разрядных шинах, которые связаны через диоды с данной адресной шиной. Запись информации в диодные ПЗУ осуществляется выжиганием ненужных диодов. На рис. 5.4 б показан элемент памяти на МДП транзисторах, который выполняется либо с тонким слоем под затвор, либо с толстым, в зависимости от того, какая информация должна храниться в данном элементе. При подаче напряжения на адресную шину, в элементах с тонким слоем под затвор образуется проводящий канал, а в элементах с толстым слоем проводящий канал не образуется.

В зависимости от числа адресных и разрядных шин (проводников), соединенных с одним запоминающим элементом (ЗЭ), различают ЗУ системы 2D, 3D, 2.DМ. ЗУ системы 2D представляет из себя плоскую матрицу из 3Э. Выборка каждого ЗЭ в матрице осуществляется одной адресной и одной разрядной шиной. ЗУ системы 3D состоит из n плоских матриц, и в каждой матрице имеются п ЗЭ. Выборка 3Э из каждой матрицы осуществляется с помощью двух адресных шин, а запись и чтение кода производится по третьей - разрядной шине. В ЗУ 2DМ чтение осуществляется по адресной и адресно-разрядной шинам, а съем выходного сигнала - по третьей шине. Запись кодов в ЗЭ производится двумя шинами: адресной и адресно-разрядной.

Адресные и разрядные линии носят общее название линий выборки. В зависимости от числа таких линий, соединенных с. одним ЗЭ, различают двух- и трехкоординатные ЗУ и т. д., называемые ЗУ типа 2D, 3D и т. д. (от английского dimention— размерность). Наибольшее распространение получили ЗУ типа 2D, 3D, 2,5D и их модификации.

Запоминающие устройства типа 2D. Организация ЗУ типа 2D обеспечивает двухкоординатную выборку каждого ЗЭ ячейки памяти. Основу ЗУ составляет плоская матрица из ЗЭ, сгруппированных по n-разрядов. Обращение к ячейке задается k-разрядным адресом, выделение разрядов производится разрядными линиями записи и считывания. Структура ЗУ типа 2D приведена на рис. 5.5.

Рис. 5.5. Структура ЗУ 2D

Адрес (k-разрядный) выбираемой ячейки I поступает на схему адресного формирователя АдрФ, управляемого сигналами чтения Чт и записи Зап. Основу АдрФ составляет дешифратор с 2к выходами, который при поступлении на его входы адреса формирует сигнал для выборки линии i, при этом под воздействием сигналов Чт и Зап из АдрФ выдается сигнал, настраивающий ЗЭ i-й линии либо на считывание (выдачу сигнала состояния), либо на запись. Выделение разряда j в i-м слове производится второй координатной линией. При записи по линии jот усилителя записи УсЗап поступает сигнал, устанавливающий выбранный для записи 33;, в состояние 0 или 1. При считывании на усилитель считывания УсСч по линии j поступает сигнал о состоянии ячейки.

Используемые здесь ЗЭ должны допускать объединение выходов для работы на общую линию с передачей сигналов только от выбранного ЗЭ. Такое свойство типично для современных ЗЭ и в дальнейшем всякий раз подразумевается.

Таким образом, каждая адресная линия выборки ячейки передает три значения сигнала: выборка при записи, выборка при считывании и отсутствие выборки. Каждая разрядная линия записи передает в ЗЭ записываемый бит информации, а разрядная линия считывания — считываемый из ЗЭ бит информации. Линии записи и считывания могут быть объединены в одну при использовании ЗЭ, допускающих соединение выхода со входом записи. Совмещение функций записи и считывания на разрядной линии широко используется в современных полупроводниковых ЗУ.

Запоминающие устройства типа 2D являются быстродействующими и достаточно удобными для реализации. Однако ЗУ типа 2D неэкономичны по объему оборудования из-за наличия в них дешифратора с 2k выходами. В настоящее время структура типа 2D используется в основном в ЗУ небольшой емкости.

Запоминающие устройства типа 3D. Некоторые ЗЭ имеют не один, а два конъюнктивных входа выборки. В этом случае адресная выборка осуществляется только при одновременном появлении двух сигналов. Использование таких ЗЭ позволяет строить ЗУ с трехкоординатным выделением ЗЭ.

Запоминающий массив ЗУ типа 3D выполнен в виде пространственной матрицы, составленной из п плоских матриц, представляющих собой ЗМ для отдельных разрядов ячеек памяти. Запоминающие элементы для разряда сгруппированы в квадратную матрицу из 2k рядов по j2k ЗЭ в каждом.

Структура матрицы k-го разряда в ЗУ типа 3D представлена на рис. 5.6. Для адресной выборки ЗЭ задаются две его координаты в 3Mj. Код адреса i-й ячейки памяти разделяется на старшую и младшую части (i' и I"), каждая из которых поступает на свой адресный формирователь. Адресный формирователь АдрФ1 выдает сигнал выборки на линию j, а АдрФ2 — на линию i".

Рис. 5.6. Структура ЗУ 3D

В результате в 3Mj оказывается выбранным ЗЭ, находящийся на пересечении этих линий (двух координат). Адресные формирователи управляются сигналами Чтение и Запись и в зависимости от них выдают сигналы выборки для считывания или записи. При считывании сигнал о состоянии выбранного ЗЭ поступает по линии считывания к УсСч (третья координата ЗЭ). При записи в выбранный ЗЭ будут занесены 0 и 1 в зависимости от сигнала записи, поступающего по линии от УсЗап (третья координата ЗЭ при записи). Для полупроводниковых ЗУ, как отмечалось выше, характерно объединение в одну линию разрядных линий записи и считывания.

Для построения n-разрядной памяти используется n матриц рассмотренного вида. Адресные формирователи при этом могут быть общими для всех разрядных ЗМ.

Запоминающие устройства типа 3D более экономичны, чем ЗУ типа 2D. Поэтому сложность двух адресных формирователей ЗУ типа 3D значительно меньше сложности адресного формирователя ЗУ типа 2D. В связи с этим структура типа 3D позволяет строить ЗУ большего объема, чем структура 2D. Структура типа 2D-M наиболее удобна для построения полупроводниковых ЗУ и широко используется в настоящее время как в оперативных, так и в постоянных ЗУ.

ОЗУ статического типа (SRAM). В качестве элемента памяти используется простейший D-триггер-защелка. В микросхеме 537РУ10 каждая ЯП состоит из восьми триггеров и располагаются ячейки на кристалле в виде прямоугольной матрицы.

На рисунке 5.7 приведены обозначения: n-адресных входов (A0.. An-1), DIO - двунаправленная восмиразрядная шина данных, вход разрешения выходов - OE, вход выбора микросхемы - CS и вход разрешения записи - WE, который часто обозначают по другому - WR/RD, подчеркивая этим, что при низком значении сигнала на этом входе производится запись байта, а при высоком уровне - чтение. EO, DI, WR - внутренние сигналы вырабатываемые блоком управления чтением/записью/хранением. Доступ к произвольной ЯПj производится с помощью прямоугольного дешифратора, состоящего из двух обычных дешифраторов, причем k-адресных линий заводится на дешифратор столбцов (DCc), а оставшиеся n-k линий подключены к дешифратору строк (DCr). Количество строк и столбцов будет соответственно равно 2(n-k) и 2k, т.е. общее количество, обслуживаемых ЯП, равно 2k * 2(n-k) = 2n.

Рис. 5.7. Структура памяти

Статическая память может быть синхронной и асинхронной. В асинхронной памяти выдача и прием информации определяется подачей комбинационных сигналов. В синхронной памяти выдача и прием информации тактируется.

ОЗУ динамического типа (DRAM). В качестве элемента памяти используется микроконденсатор в интегральном исполнении, размеры которого значительно меньше D-триггера статической памяти. По этой причине, при одинаковых размерах кристалла, информационная емкость DRAM выше, чем у SRAM. Количество адресных входов и габариты должны увеличиться.Чтобы не допустить этого, адресные линии внутри микросхемы разбиваются на две группы, например старшая и младшая половина. Две одноименные k-линии каждой группы подключаются к двум выходам внутреннего k-го демультиплексора "1 в 2", а его вход соединяется с k-ым адресным входом микросхемы. Количество адресных входов, при этом уменьшается в два раза, но зато передача адреса в микросхему должна производиться, во-первых в два приема, что несколько уменьшает быстродействие, и во-вторых потребуется дополнительный внешний мультиплексор адреса.В процессе хранения бита конденсатор разряжается. Чтобы этого не допустить заряд необходимо поддерживать.

Суммируя, можно перечислить чем отличается динамическое ОЗУ от статического: 1) мультиплексированием адресных входов, 2) необходимостью регенерации хранимой информации, 3) повышенной емкостью (до нескольких Мбит), 4) более сложной схемой управления. На рисунке 5.5 приведено условное обозначение микросхемы 565РУ7 емкостью 256K*1 (218K) и способ подключения 18-ти линий адреса к девяти адресным входам с помощью 9-ти мультиплексоров "2 в 1", например трех счетверенных селекторов-мультиплексоров типа 1533КП16.

Рис.5.8. Схема подключения микросхемы 565РУ7

Динамическая память может быть синхронной и асинхронной. В асинхронной памяти выдача и прием информации определяется подачей комбинационных сигналов. В синхронной памяти выдача и прием информации тактируется.

Все DRAM имеют несколько режимов работы – чтения/записи, страничный режим чтения и записи, а также режим регенерации.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Классификация запоминающих устройств?

2. Что такое ПЗУ?

3. Что такое ОЗУ?

4. Что такое статическое ЗУ?

5. Что такое динамическое ЗУ?

6. Какой запоминающий элемент используется в статических ЗУ?

7. Какой запоминающий элемент используется в динамическихЗУ?

Тема лекции 6. Общие принципы построения микропроцессорных систем (МПС). Основные понятия и определения. Структура МПС. Классификация микропроцессоров (МП). Архитектура МП.

Микропроцессор (МП) - программно-аппаратное устройство, изготовленные в одном кристалле, в виде большой (БИС) или сверхбольшой интегральной схемы (СБИС) и предназначенные для обработки информации представленной в двоичной форме (арифметические и логические операции над двоичными информацией).

Микропроцессорные системы (МПС) - программно-аппаратная система ядром которого является МП и память, обладающая в идеале возможностями приема, обработки и вывода любой информации (сигнал, текст, видео, речь и т.д.) в заданной разработчиком форме и алгоритму.

Классификация МП.

По разрядности данных: 8-, 16-,32-, 64- разрядные

По конструктивному исполнению делятся:

- однокристальные МП;

- многокристальные МП.

К однокристальным относятся МП вся схема которой расположено в теле одного кристалла и выполняет все заданные функции.

Многокристальные МП делятся на два класса:

- многокристальные МП с фиксированной разрядностью в 4 и 8 разрядов, из которых с помощью объединяющих интерфейсных микросхем можно собрать 8,16,32 и 64 разрядные МП;

- секционные многокристальные МП с разделением функции выполняемого одним кристаллом, например: 8 разрядная секция АЛУ; 8 разрядная секция РОН, 8 разрядная секция УУ и т.д.. из комплекта которых можно собрать 8 разрядный МП.

Архитектура процессоров делится на два вида:

- фон-Неймановская, когда в МП реализуется концепция хранимой программы: программы и данные хранятся в одной и той же памяти (рис. 6.1);

- Гарвардская архитектура. Особенностью этой архитектуры является то, что память данных и программ разделены и имеют отдельные шины (рис. 6.2).

Р

Рис 6.1. Фон-Неймановская архитектура Рис. 6.2. Гарвардская архитектура

Микроконтроллером называется МПС с встроенной памятью программ и данных, а также встроенным интерфейсом для подключения внешних устройств, предназначенные для использования в системах управления технологическим оборудованием и/или процессами. Микроконтроллеры используемые для цифровой обработки сигналов называются процессорами цифровой обработки или спецпроцессорами.

В общем смысле под архитектурой процессора понимается его программная модель, то есть программно-видимые свойства. Под микроархитектурой понимается внутренняя реализация этой программной модели. Для одной и той же архитектуры разными фирмами и в разных поколениях применяются существенно различные микроархитектурные реализации, при этом, естественно, стремятся к максимальному повышению производительности. Сейчас существует множество архитектур процессоров, которые делятся на три категории – RISC, CISC и VLIW.

RISC - Reduced (Restricted) Instruction Set Computer - процессоры (компьютеры) с сокращенной системой команд. Эти процессоры обычно имеют набор однородных регистров универсального назначения, причем их число может быть большим. Система команд отличается относительной простотой, коды инструкций имеют четкую структуру, как правило, с фиксированной длиной.

CISC - Complete Instruction Set Computer - процессоры (компьютеры) с полным набором инструкций, к которым относится и семейство х86. Состав и назначение их регистров существенно неоднородны, широкий набор команд усложняет декодирование инструкций, на что расходуются аппаратные ресурсы. Возрастает число тактов, необходимое для выполнения инструкций.Процессоры х86 имеют самую сложную в мире систему команд. Хорошо ли это, вопрос спорный, но груз совместимости с программным обеспечением для IBM PC, имеющим уже 20-летнюю историю, не позволяет расставаться с этим "наследием тяжелого прошлого". В процессорах семейства х86, начиная с 486, применяется комбинированная архитектура - CISC-процессор имеет RISC-ядро.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Какие функций выполняет МП?

2. Перечислите основные блоки МПС?

3. Из скольких шин состоит МПС стандартной конфигураций?

4. Основные методы ввода и вывода информации?

5. Основные методы передачи информации в МПС?

6. В чем отличие Гарвардской архитектуры от Фон-Неймановской?

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 1259; Нарушение авторских прав?; Мы поможем в написании вашей работы!