КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тема лекции 7. Однокристальные МП. Однокристальные 8-разрядные МП. Основные функции МП. Запись, считывание, прерывание и прямой доступ к памяти

|

|

|

|

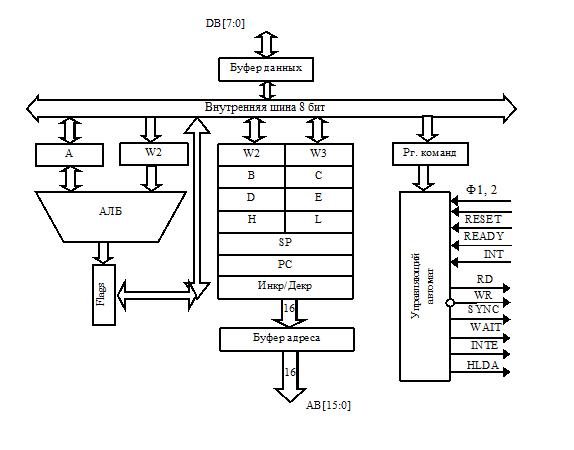

Микропроцессор i8080. На рис. 7.1. представлена внутренняя структура МП i 8080, включающего в себя 8-разрядное АЛУ с буферным регистром и схемой десятичной коррекции, блок РОН, регистры указателя стека SP и счетчика команд PC, первичный управляющий автомат УА, буферные схемы шин адреса и данных и схему управления системой.

Внешний интерфейс представлен 8-разрядной двунаправленной шиной данных D[7:0], 16-разрядной шиной адреса A[15:0] и группой линий управления.

Рис. 7.1. Внутренняя структура МП i8080

Назначение входных и выходных линий МП:

Ф1,Ф2 - сигналы тактового генератора частотой 1..2,5 МГц;

RESET - сброс (начальная установка и запуск программы с адреса 0000);

READY - входной сигнал готовности памяти или ВУ к обмену (обеспечивает асинхронный режим обмена);

INT - запрос внешнего прерывания;

HOLD - захват шины (требование прямого доступа в память со стороны ВУ);

WR - запись - выходной сигнал, определяющий направление передачи информации по шине данных от процессора к памяти или ВУ;

RD - чтение - выходной сигнал, определяющий направление передачи информации по шине данных от памяти или ВУ к процессору;

SYNC - выходной сигнал, идентифицирующий наличие на шине данных дополнительной управляющей информации (PSW);

WAIT - выходной сигнал, отмечающий состояние ожидания или останова МП;

INTE - выходной сигнал, подтверждающий режим внешних прерываний;

HLDA - выходной сигнал, подтверждающий режим прямого доступа в память (подтверждение захвата).

Командный цикл микропроцессора. В основе работы МП лежит командный цикл - действия по выбору из памяти и выполнению одной команды. В зависимости от типа и формата команды, способов адресации и числа операндов командный цикл может включать в себя различное число обращений к памяти и ВУ и следовательно - иметь различную длительность.

|

|

|

Любой командный цикл (КЦ) начинается с извлечения из памяти первого байта команды по адресу, хранящемуся в PC. Команды i8080 имеют длину 1, 2 или 3 байта, причем в первом байте содержится информация о длине команды. В случае 2- или 3-байтовой команды реализуются дополнительные обращения к памяти по соседним адресам.

После считывания команды начинается ее выполнение, причем в процессе выполнения может потребоваться еще одно или несколько обращений к памяти или ВУ (чтение операнда, запись результата).

Для реализации команды i8080 может потребоваться от 1 до 5 обращений к памяти (ВУ). Хотя обращения к ЗУ/ВУ располагаются в разных частях КЦ, выполняются они по единым правилам, соответствующим интерфейсу МПС и реализованы на общем оборудовании управляющего автомата. Действия МПС по передаче в/из МП одного байта данных/команды называются машинным циклом.

Машинные циклы и их идентификация. Командный цикл представляет собой последовательность машинных циклов (МЦ), причем КЦ i8080 может содержать от 1 до 5 МЦ, которые принято обозначать M1, M2,..M5.

МЦ обязательно включает в себя действия по передаче байта информации. Кроме того, в некоторых МЦ дополнительно реализуются действия по пересылке и/или преобразованию информации внутри МП. Поэтому длительность МЦ может быть различной - за счет различного числа содержащихся в них машинных тактов (T1, T2,...).

Машинный такт образует пара сигналов тактового генератора Ф1, Ф2, поэтому длительность такта постоянна - период тактового генератора (за исключением такта Tw - см. ниже).

С помощью входа READY можно не только согласовывать работу МП с устройствами различного быстродействия, но и реализовывать пошаговый и потактовый режимы работы МП:

- выдача адреса;

- выдача информации о начатом МЦ;

- анализ значения входных сигналов;

|

|

|

- при необходимости – ожидание сигнала готовности;

- прием/выдача данных;

- при необходимости – внутренняя обработка/пересылка данных.

При реализации одного МЦ процессор может:

1) принять из памяти байт команды;

2) принять из памяти байт данных;

3) принять из УВВ байт данных;

4) принять из стека байт данных;

5) принять вектор прерывания;

6) выдать в память байт данных;

7) выдать в стек байт данных;

8) выдать на УВВ байт данныхю

Дефицит внешних выводов МП не позволяет выводить во внешний интерфейс достататочный для эффективного функционирования объем управляющей информации. Для выдачи более полной информации о состоянии МП в текущем МЦ используется мультиплексированные шины данных. В начале каждого МЦ на линий шины данных D [7:0] выдается байт дополнительной управляющей информации записывающиеся во внешний регистр состояния (PSW), разряды которого имеют следующее значение:

D0 - подтверждение прерывания;

D1 - запись (в ЗУ) или вывод (на УВыв);

D2 - обращение в стек;

D3 - подтверждение останова;

D4 - вывод (на УВыв);

D5 - M1 (считывание из памяти первого байта команды);

D6 - ввод (из УВв);

D7 - чтение (из ЗУ).

Наличие на D[7:0] управляющей информации отмечается специальным выходным сигналом SYNC.

Байт управляющей информации присутствует на шине данных (ШД) один такт, а использоваться может в течение всего МЦ. Поэтому в МПС, использующих информацию PSW, предусматривается специальный, внешний по отношению к МП, регистр-защелка для фиксации PSW.

Организация прямого доступа к памяти. В современных ЭВМ широко используется прямой доступ к памяти (ПДП), что дает возможность использовать в МПС быстродействующих внешних запоминающих устройств таких как накопители на магнитных лентах (НМЛ) и магнитных дисках (НМД). ПДП обеспечивает высокую скорость обмена данными за счет, того, что управление обменом производится не программным путем, а электронными схемами. Такие электронные схемы, внешние по отношению к процессору, размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти.

При подключении контроллера ПДП возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Одним из путей решения этой проблемы является использование тех машинных циклов процессора, в которых он не обменивается данными с памятью и принудительным отключением процессора от шин системного интерфейса.

|

|

|

Для реализации такого режима работы ПДП системный интерфейс МПС дополняется двумя линиями для передачи управляющих сигналов "Требование прямого доступа к памяти" (HOLD) и "Предоставление прямого доступа к памяти" (HLDA).

Сигнал HOLD при необходимости вырабатывается контроллером ПДП. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, "захватывая" цикл процессора выдает в системный интерфейс сигнал HLDA и отключается от шин системного интерфейса. После чего шины интерфейса управляются контроллером ПДП, и осуществляется обмен одним байтом или словами данных с памятью микроЭВМ, и затем, сняв сигнал HOLD, возвращает управление системным интерфейсом МП. Как только контроллер ПДП будет готов к обмену со следующим байтом, он вновь "захватывает" цикл процессора и т.д. В промежутке между сигналами HOLD процессор продолжает выполнять команды программы.

Одним из представителей 8-разрядных МП является упрощенный вариант 16-разрядного МП Intel 8086 под названием Intel 8085 или i 8085.

Структура и функционирование микропроцессора Intel 8085. Во всём мире широко применяются микропроцессоры фирмы Intel и их аналоги. Для изучения, в данном случае выбран МП К1821ВМ85А - аналог микропроцессора Intel 8085A. Это простой для изучения объект, на котором легко проследить основные принципы работы МП.

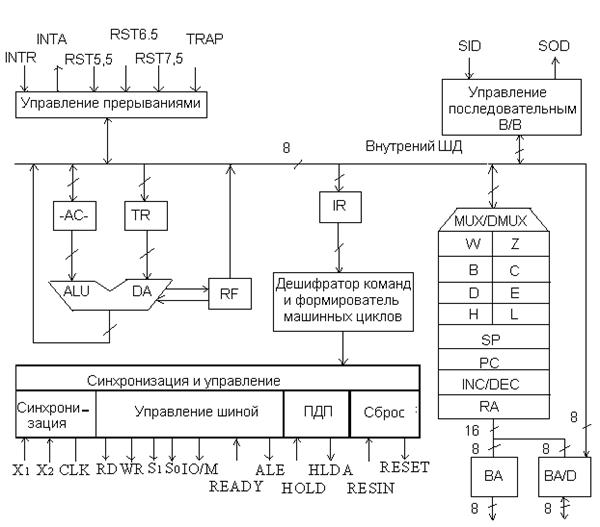

Рис. 7.2. Структура микропроцессора К1821ВМ85А

Структура микропроцессора К1821ВМ85А показана на рис. 7.2.

Микропроцессор имеет восьмиразрядную шину данных (внутреннюю), через которую его блоки обмениваются информацией. На схеме приняты следующие обозначения.

AC (Accumulator) – регистр-аккумулятор, выполненный на двухступенчатых триггерах и способен хранить одновременно два слова (один из операндов и результат операции);

TR (Temporary Register) – регистр временного хранения одного из операндов;

|

|

|

ALU (Arithmetic-Logic Unit) – арифметико-логическое устройство (АЛУ), выполняющее действие над двумя словами- операндами, подаваемыми на его входы. Аккумулятор служит источником и приёмником данных, TR – источником слова данных, хранимым на время выполнения операции. АЛУ функционирует согласно отношению A:=A*B, где B хранится в TR, второй операнд поступает от аккумулятора, в него же поступает результат операции. АЛУ непосредственно выполняет лишь операции сложения, вычитания, сдвига, сравнения слов, поразрядные логические операции (конъюнкцию, дизъюнкцию, сложение по модулю 2). Более сложные операции (умножение и деление и др.) выполняется по подпрограммам. В АЛУ имеется схема перевода двоичных чисел в двоично-десятичные (DA, Decimal Adjust).

RF (Register Flags) – регистр флажок, т. е. битов, указывающих признаки результатов арифметических или логических операций, выполненных в АЛУ.

Указываются пять признаков: Z (Zero) – нулевой результат, C (Carry) – перенос, AC (Auxiliary Carry) – вспомогательный перенос, S (Sing) – знак, P (Parity) – чётность веса слова. Признак вспомогательного переноса (переноса между младшей и старшей тетрадами восьмиразрядного слова) нужен при выполнении операции в двоично-десятичном коде. Смысл остальных признаков ясен из их наименований. Признаки служат для управления ходом процесса обработки информации.

Назначение блоков управления прерыванием и последовательным вводом/выводом ясно из их названий. Режимы прерывания и последовательного ввода/вывода подробнее рассмотрены далее.

При естественном следовании команд МП, начав работу, выбирает из памяти и выполняет одну команду за другой, пока не дойдёт до команды ”Останов”(HАLT). Каждое обращение к памяти или ВУ требует машинного цикла, который связан с передачей байта в МП или из него. В свою очередь машинный цикл делится на то или иное число тактов Т, число которых зависит от типа машинного цикла.

Микропроцессор К1821ВМ85А имеет следующие типы машинных циклов:

- выборки команды (OF, Opcode Fetch).

- чтения из памяти (MR, Memory Read).

- записи в память (MW, Memory Write).

- чтение из ВУ (IOR, Input-Output Read).

- записи в ВУ (IOW, Input-Output Write).

- подтверждение прерывания (INA, Interrupt Acknowledge).

- освобождения шин (BI, Bus Idle).

- останов (HALT).

В начале каждого машинного цикла генерируются сигналы состояния, идентифицирующие тип цикла и действующие в течение всего цикла

S1, S0 - сигналы состояния МП, сообщаемые внешней среде. Формируются в начале и сохраняются во время всего машинного цикла.

IO/M – сигнал выбора памяти или внешнего устройства. При высоком уровне происходит обращение к ВУ, при низком – к памяти.

Совместно с сигналами S1, S0 сигнал IO/M идентифицирует тип машинного цикла. Сигналы состояния и управляющие сигналы RD, WR и INTA для различных машинных циклов имеют значения, представленные в таблице 7.1.

Совместно с сигналами S1, S0 сигнал IO/M идентифицирует тип машинного цикла. Сигналы состояния и управляющие сигналы RD, WR и INTA для различных машинных циклов имеют значения, представленные в таблице 7.1.

Таблица 7.1.

| Тип МЦ | Сигналы состояния | Сигналы управления | ||||

| IO/M | S1 | S0 | RD | WR | INTA | |

| OF MR MW IOR IOW INA BI HALT | TC* TC | X | X | TC | TC |

В приведённой таблице TC обозначается третье состояние.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Принцип организации и архитектура микропроцессора i8080?

2. Отличие микропроцессора i8085 от микропроцессор i8080?

3. Состав микропроцессора микропроцессор i8080?

4. Состав микропроцессора микропроцессор i8085?

5. Из скольких Машиных циклов состоит процесс записи и считывания?

6. Основные функции выполняемые микропроцессором i8080?

7. Основные функции выполняемые микропроцессором i8085?

Тема лекции 8. Однокристальные 16-разрядные МП. Структурная схема i 8086. Циклы шины процессора. Типы прерываний. Система команд МП.

К 16- разрядным МП первого поколения принадлежат МП i8086. МП выполняет операции над 8- и 16-разрядными данными и имеет встроенные аппаратные средства умножения и деления. МП i8086 имеет внутреннее СОЗУ 14 х 16 байт. Шина адреса является 20-разрядной, что позволяет непосредственно адресовать 1 Мбайт памяти.

МП i8086 работает в двух режимах. Вминимальном режиме, используемом для построения однопроцессорных МПС. В максимальном режиме, используемом для построения мультипроцессорных систем.

Структурная схема МП i8086. В МП i8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд.

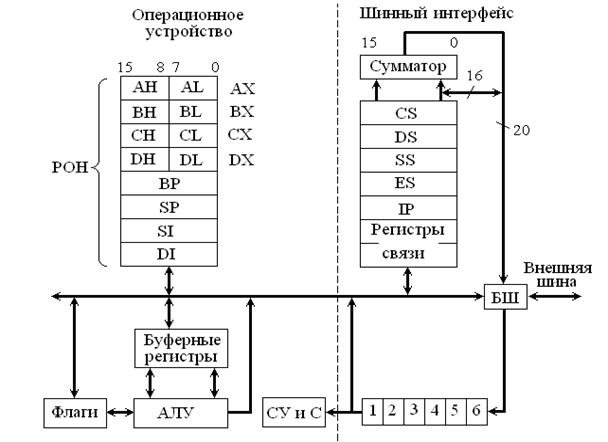

Структурная схема МП i8086 показана на рис. 8.1. Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с внешней шиной – выставляет адреса, считывает коды команд и операнды, записывает результаты вычислений в память или устройства ввода и вывода.

Рис. 8.1. Структурная схема микропроцессора i8086

Операционное устройство состоит из РОН, предназначенных для хранения промежуточных результатов вычислений – данных и адресов; АЛУ с буферными регистрами; Регистра флагов; схемы управления и синхронизации (СУ и С), которая дешифрирует коды команд и генерирует управляющие сигналыдля всех блоков схемы МП.

Шинный интерфейс состоит из шестибайтнойрегистровой памяти, которая называется очередью команд, четырех сегментных регистров: CS, DS, ES, SS; указатели команд IP, сумматора, а также вспомогательных регистров связи и буферных схем шин адреса и данных.

В данном МП применена впервые конвейерная архитектура, котораяпозволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд. Это достигается паралельной работой двух сравнительно

независимых устройств – операционного устройства и шинного интерфейса.

Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействиес внешней шиной – выставляет адреса, считывает коды команд и операнды, записывает результаты вычислений в память или устройства ввода/вывода.

Операционное устройство состоит из РОН, предназначенных для хранения промежуточных результатов вычислений – данных адресов; АЛУ с буферными регистрами; регистр флагов; схемы управления и синхронизации, которая дешифрирует коды клманд и генерирует управляющие сигналы для всех блоков МП.

Шинный интерфейс состоит из шестибайтной регистровой памяти, которая называется очередью команд, четырех сегментных регистров: CS, DS, ES, SS, указателя команд IP, сумматора. А также вспомогательных регистров связи и буферных схем шин адреса/данных.

Линий ST2-ST0 – выходы сигналов состояния- идентифицирует тип цикла шины, который выполняется в соответствии с табл. 8.1.

Таблица 8.1.

| Линий | состояния | Типы цикла шины | |

| ST2 | ST1 | ST0 | |

| ПОДТВЕРЖДЕНИЕ ПРЕРЫВАНИЯ (INTA) | |||

| ВВОД (чтение внешнего устройства) | |||

| ВЫВОД (запись во внешнее устройство) | |||

| ОСТАНОВ | |||

| ВЫБОРКА КОМАНДЫ | |||

| ЧТЕНИЕ ИЗ ПАМЯТИ | |||

| ЗАПИСЬ В ПАМЯТЬ | |||

| Цикла шины нет |

Циклом шины называют обращение к ячейке памяти или внешнему устройству. Это определение совпадает с определением машинного цикла для 8-разрядных МП. Однако в 16-разрядных процессорах цикл шины может инициировать не толькоМП, но и арифметический соопроцессор i8087 или специализированный процессор вводв/вывода. Начало цикла определяется переходом линий состояния ST2-ST0 из пассивного состояния (111) в активное, а конец обратным переходом в пассивное состояние. Сигналы ST2-ST0 подаются на входы контроллера шины i8288, который дешифрирует их и формирует сигналы управление системной шиной.

Сигналы ST3, ST4 определяют, какой сегментный регистр используется в данном машинном цикле(см. табл. 8.2).

Таблица 8.2.

| ST4 | ST3 | Сегментный регистр |

| ES | ||

| SS | ||

| CS | ||

| DS |

Сигналы QS1, QS2 определяет операцию над очередью команд в соответствии с табл. 8.3.

Таблица 8.3.

| QS1 | QS2 | Операции над очередью |

| Операции нет, в последнем такте не было выборки из очереди | ||

| Из очереди выбран первый байт команды | ||

| Очередь пуста | ||

| Из очереди выбран следующий байт команды |

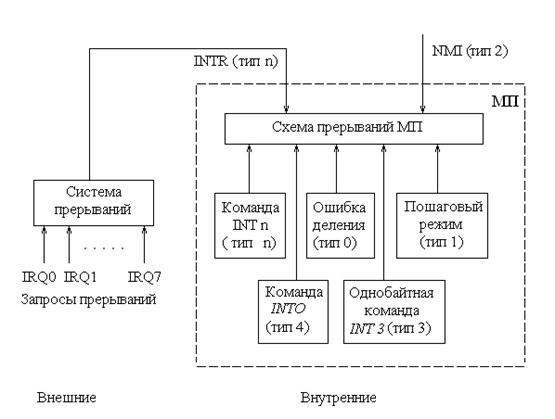

Прерывания делятся на внешние аппаратные и внутренние. Запросы прерываний IRQ внешних аппаратных прерываний оступают в ситему прерываний или на линию немаскированного прерывания NMI МП. Система прерывания формирует сигнал INTR маскированного прерывания МП.

Рис. 8.2. Типы прерываний

Типы прерываний показаны на рис. 8.2. Внутренние прерывания процессора разделяют на программные и аппаратные. Источниками внутренних программных прерываний (см. рис. 8.2.) являются: ошибка деления (тип 0); пошаговый режим (тип 1); команда INTO (тип 4).

Внутренние программные прерывания INT n и INT 3 выполняются по команде прерывания и разрешают вызывать подпрограммы обработки прерываний.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Принцип организации и архитектура микропроцессора i8086?

2. Отличие микропроцессора i8086 от микропроцессор i8080?

3. Состав микропроцессора микропроцессор i8086?

4. Какие типы машиных циклов существует?

5. Какие типы прерывания существует?

6. Какие сегментные регистры используются микропроцессором i8086?

Тема лекции 9. Построение модуля центрального процессора Построение модуля центрального процессора на базе i 8086 и схема подключения ОЗУ и ПЗУ. Буферный регистр. Шинные формирователи.

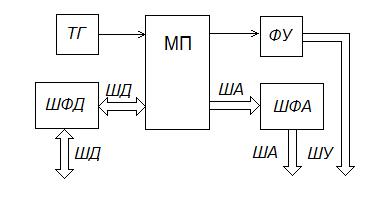

Микропроцессорная система состоит из трех основных блоков: микропроцессора МП, устройства сопряжения с объектом УСО и объекта управления (см. рис. 9.1.).

Рис. 9.1. Микропроцессорная система

Основным и центральным блоком МПС является ядро МПС в составе самого МП и шинных формирователей, которые обеспечивает согласование нагрузок в МПС (см. рис. 9.2).

Рис. 9.2. Схема модуля центрального процессора

Напомним, что по техническим условиям эксплуатации нагрузочная способность выводов МП не должна превышать нагрузки одного входа элемента ТТЛ. Такая низкая нагрузочная способность выводов микропроцессора объясняется стремлением уменьшить величину тока, протекающего через транзисторы кристалла микропроцессора, и связанную с ним выделяемую тепловую энергию. Увеличение нагрузочной способности выводов микропроцессора неизбежно потребовало бы использования транзисторов большей мощности. Это привело бы, во-первых, к увеличению их количества и, во-вторых, к повышению температуры кристалла.

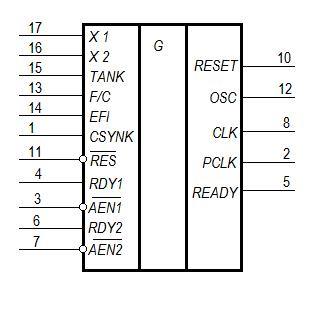

Для построения модуля ЦП необходимо обеспечить синхронизацию работы системы и согласование работы с ЦП с системной шиной. Для синхронизации используется внешний генератор схема которого приведена на рис. 9.3.

Рис. 9.3. Условное обозначение внешнего генератора

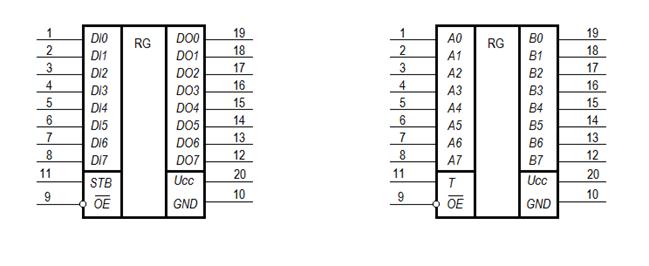

Для согласования нагрузки различных устройств ипользуется буферные регисты структура которых показана на рис. 9.4., которые служит основой шинных формирователей.

Рис. 9.4. Структурная схема буферного регистра

Однако практические задачи, решаемые МС, требуют подключения памяти, дешифраторов, связных адаптеров и т.д., что значительно превышает допустимую нагрузку выводов микропроцессора. Поэтому для увеличения нагрузочной способности микропроцессора в шины адреса и данных встраивают специальные буферы, выполненные на ИС, которые называются шинными формирователями (ШФ). Наиболее распространенными являются четырехразрядные ШФ К589АП16, К589АП26 и восьмиразрядные ШФ К580ВА86 и К580ВА87 (см. рис. 9.5)

Рис. 9.5. Условные обозначение шинных формирователей

С точки зрения разрядности предпочтение следует отдать ШФ серии К580.. Корпус 8-разрядного ШФ К580ВА86 имеет информационные выводы А0-А7 и В0-В7, вывод Т, логическое содержание которого определяет направление передачи информации, и вывод OE (выборки кристалла).

Формирование шины адреса системы. Шина адреса МС на базе микропроцессора i 8086 является однонаправленной 20-разрядной. Поэтому для ее буферирования необходимо использовать три корпуса ИС К580ВА86. На рис. 9.6 показана схема включения трех ШФ для образования ША системы.

Рис. 9.6. Функциональная схема модуля центрального процессора

Поскольку направление передачи в ША системы происходит в одном направлении, а выводы канала А шинного формирователя предпочтительно подключить к микропроцессору, то ШФ должен быть включен в режим для передачи данных из канала А в канал В, для чего на вывод Т необходимо подать сигнал высокого уровня. Это достигается подключением к выводу Т источника питания +5В через резистор 1 кОм. Вывод ВК формирователей можно объединить и подключить к общему выводу платы.

В том случае, если в системе предусматривается использовать режим ПДП, в котором необходимо отключать шину адреса от микропроцессора при наличии сигнала высокого уровня ПЗХ, то этот сигнал можно использовать для перевода ШФ в выключенное состояние. Для этого сигнал ПЗХ микропроцессора нужно подключить к выводу ВК формирователя через любой логический элемент, обеспечивающий большую нагрузочную способность.

Формирование шины данных системы

Шина данных системы служит для передачи 16-разрядных данных в двух направлениях: от МП к ВУ и в обратном направлении. Поэтому буфер шины данных, реализованный на двух микросхемах К580ВА86, должен иметь возможность переключения направления передачи данных. Для этой цели удобно использовать сигналы микропроцессора ПМ - прием и ВД - запись. В режиме приема высоким уровнем сигнала ПМ формирователь обеспечивает передачу данных из канала В и шины данных в микропроцессор. В режиме записи низким уровнем сигнала ПМ на входе Т формирователь изменит направление передачи данных, и данные будут передаваться от микропроцессора в шину данных системы. В режиме захвата высоким уровнем сигнала ПЗХ на входе ВК формирователя любые передачи будут блокированы.

Формирование системной шины управления. Микропроцессорная система может содержать значительное количество внешних устройств. Для обмена данными между ними все ВУ подключаются к общей системной шине данных и системной адресной шине. Для четкого взаимодействия микропроцессора и ВУ необходимы специальные управляющие сигналы, составляющие системную шину управления. Для управления процессом обмена данными с ВУ микропроцессор имеет только два сигнала управления: ПМ - прием и ВД - запись. Этих сигналов явно недостаточно, поэтому сигналы системной шины управления формируются специальной схемой с использованием управляющих сигналов ПМ и ВД и байта «слова состояния» микропроцессора.

Напомним, что в такте Т1 каждого цикла микропроцессор выдает на свою ШД одновременно с синхронизирующим сигналом С байт «слова состояния» МП, которое в такте Т2 записывается во внешний регистр, чтобы его можно было использовать в течение всего машинного цикла. Разряды байта состояния микропроцессора, записанные в регистр, используются далее для формирования управляющих сигналов системной шины управления.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Определение и состав МПС управления объектом?

2. Перечислите состав центрального МП блока на базе МП i8086?

3. Основная функция шинных формирователей?

4. Основная функция фнешнего генератора?

5. Отличие ШФ для шины адреса и шины данных?

6. Основные функции выполняемые буферным регистром?

Тема лекции 10. Интерфейсы ввода и вывода. Шинная организация IBM PC. Передача информации в МПС. Методы ввода/вывода и их классификация. Последовательная передача данных.

Интерфейсы ввода/вывода. Все внешние устройства требуют для своего функционирования определенного набора управляющих сигналов, протокола обмена и способа обмена с ЭВМ, вида используемого кода, и поэтому шины обмена информацией подключаются не непосредственно к периферийному устройству, а через интерфейс, структура и принцип работы которого в сильной степени определяется совместимостью компонентов.

Сложность интерфейса в значительной мере определяются степенью совместимости ЭВМ и периферийных устройств, которая, в свою очередь, определяется четырьмя основными признаками: быстродействием, кодами, используемыми при обмене, архитектурой процессора, электрическими характеристиками.

Таким образом, под интерфейсом будем понимать совокупность программных и аппаратных средств, с помощью которых компоненты системы объединяются с целью решения требуемых задач.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 2059; Нарушение авторских прав?; Мы поможем в написании вашей работы!