КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тема лекции 15. Коммуникационные и сетевые процессоры. Коммуникационный МП MPC8260. Сетевые микропроцессоры компаний Intel. Микропроцессор IXP1200

|

|

|

|

Коммуникационные процессоры – это микрочипы, представляющие собой нечто среднее между жесткими специализированными интегральными микросхемами и гибкими процессорами общего назначения. Коммуникационные процессоры программируются, как и привычные для нас ПК-процессоры, но построены с учетом сетевых задач, оптимизированы для сетевой работы и на их основе производители – как процессоров, так и оборудования – пишут программное обеспечение для специфических приложений. Коммуникационный процессор имеет собственную память и оснащен высокоскоростными внешними каналами для соединения с другими процессорными узлами. Скоростной коммуникационный процессор с RISC-ядром позволяет управлять обменом данными по нескольким независимым каналам, поддерживать практически все распространенные протоколы обмена, гибко и эффективно распределять и обрабатывать последовательные потоки данных с временным разделением каналов.

Коммуникационный контроллер MC68360 (QUICC)

Наиболее широкими возможностями обладает контроллер MC68360, использующий 32-разрядный процессор CPU32+ и модуль коммуникационного процессора CPM, который является расширенным вариантом СP. Этот контроллер, который получил название QUICC (Quad Integrated Communications Controller), рассматривается подробно.

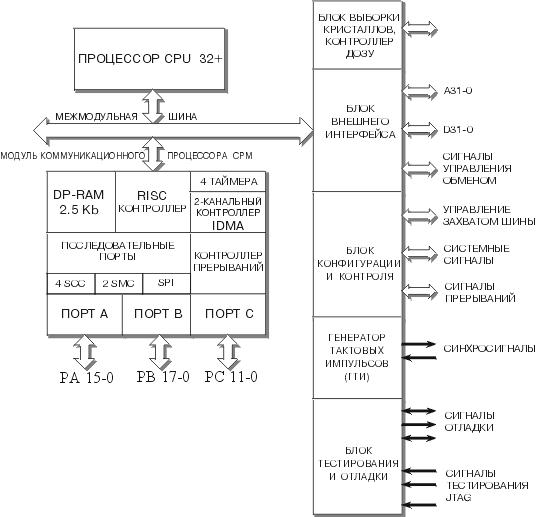

Контроллер MC68360 и его модификации MC68EN360, MC68MH360 имеют модульную структуру (рис. 15.1), в которую входят центральный процессор CPU32+, модуль коммуникационного процессора CPM и модуль системной интеграции SIM60, соединенные общей внутренней шиной.

Рис. 15.1. Общая структура коммуникационного процессора MC68360.

Центральный процессор CPU32+

Процессор CPU32+ имеет архитектуру, принятую в микропроцессорах семейства 68000, что позволяет использовать большой объем программного обеспечения, созданный для этого семейства. Процессор обеспечивает работу с 32-разрядными шинами адресов и данных, аналогично MС68020 и более поздним моделям семейства 68000.

|

|

|

Архитектура процессора ориентирована на раздельное выполнение двух классов задач: управление работой системы с помощью супервизора(операционной системы) или решение прикладных задач пользователя.. В режиме супервизора разрешается выполнение любых команд, реализуемых процессором, и доступ ко всем его регистрам. В режиме пользователя запрещается выполнение ряда команд и доступ к некоторым регистрам, чтобы не допустить такие изменения состояния системы, которые могут помешать выполнению других пользовательских программ или нарушить режим работы процессора, установленный супервизором.

Процессор CPU32+ выполняет набор из 158 команд, которые реализуют пересылку данных, арифметические и логические операции, сдвиги, операции сравнения и тестирования, битовые операции, операции управления и условной установки байтов. Часть команд выполняется только в режиме супервизора. Это привилегированные команды, попытка выполнения которых в режиме пользователя вызывает прерывание программы.

В набор команд включены команды интерполяции, которые вычисляют значения линейной функции в 255 промежуточных точках отрезка, для которого задаются конечные значения. Таким образом исключается необходимость хранения в памяти промежуточных значений линейных функций. Процесор CPU32+ не имеет специальных команд ввода-вывода данных. Для обращения к внешним устройствам их адрес формируется и выдается на адресную шину, как при выборке ячеек памяти.

Процессор CPU32+ реализует обслуживание программных исключений, возникающих при выполнении некоторых команд, и аппаратных исключений, которые вызываются внешними запросами или внутренними сигналами, формируемыми при возникновении ряда ситуаций.

|

|

|

Во всех этих ситуациях процессор заносит в стек кадр определенного формата, содержимое которого обеспечивает возвращение к прерванной программе. Стековый кадр имеет размер от 4 до 12 байт, и содержит текущие значения регистров PC и SR, код формата Fe и адрес вектора прерывания Av, а также дополнительную информацию, которая помогает подпрограмме обслуживания определить причину исключения.

После загрузки стека в PC заносится из памяти вектор исключения Ve - начальный адрес подпрограммы обслуживания. Эти вектора хранятся в таблице, базовый адрес которой содержится в регистре VBR. Каждое исключение имеет свой номер Ne, который принимает значения от 0 до 255. Значение Ne, сдвинутое на два разряда влево, дает относительный адрес вектора в таблице исключений. Таблица может иметь объем до 1024 байт и содержать адреса входов для 254 подпрограмм обслуживания.

Специфические особенности функционирования и применения MC68360 и его модификаций MC68EN360, MC68MH360 связаны с наличием в их составе коммуникационного процессора CPM, который содержит большой набор интерфейсных блоков, обеспечивающих возможности подключения контроллера к линиям связи с различными протоколами обмена.

Модуль CPM подключается к внутренней шине и работает под управлением собственного RISC-контроллера с минимальным вмешательством процессора CPU32+. Основное назначение CPM - обеспечить разнообразные каналы параллельной и последовательной передачи данных между микропроцессорной системой, управление которой осуществляет CPU32+ через интерфейсный модуль SIM60, и внешними устройствами, подключенными с помощью линий связи с различными протоколами обмена. Коммуникационный контроллер может работать в режиме ведомого (slave). В этом режиме его CPU отключается, и модуль CPM функционирует под управлением внешнего процессора. Таким образом можно реализовать систему из нескольких CPM (контроллеров в режиме ведомого), работающих под управлением одного ведущего процессора.

КМК МС68302 содержит встроенный коммуникационный процессор, самостоятельно выполняющий программы по обработке практически любого протокола связи (см. рис. 15.2).

|

|

|

Рис.15.2. Структура коммуникационного контроллера MC68302

В ПЗУ микрокода изначально содержатся программы, поддерживающие наиболее распространенные протоколы: HDLC, BISYNC, UART, Transparent и другие. Кроме того, программы могут выполняться из двухпортового ОЗУ, что позволяет реализовать практически любой нестандартный протокол и делает данный КМК чрезвычайно универсальным. Три независимых коммуникационных контроллера (SCC) имеют индивидуальные каналы прямого доступа к памяти как на прием, так и на передачу. Взаимодействие со встроенным управляющим процессором 68000 осуществляется через двухпортовое ОЗУ емкостью 1152 байт, половина которого используется для указателей входных/выходных буферов, а вторая половина может использоваться для хранения данных или загрузки микрокода. Коммуникационный процессор обеспечивает одновременную работу всех трех каналов, причем каждый из них может обрабатывать любой из протоколов. Помимо поддержки логических протоколов, МС68302 имеет блок сопряжения с физическими интерфейсами: немультиплексируемый интерфейс с поддержкой модемных сигналов (NMSI) и интерфейсы с временным мультиплексированием, например, ИКМ или ISDN BRI (IDL и GCI). Производительность МС68302 позволяет обрабатывать потоки информации до 2 Мбит/с. Помимо основных последовательных каналов (SCC), МС68302 содержит два контроллера управления обменом SМС, поддерживающие работу с IDL или GCI, а также синхронный последовательный интерфейс SCP.

Управляющий процессор 68000 является базовой моделью широко распространенного семейства 680х0, что предоставляет в распоряжение пользователя огромный выбор апробированного программного обеспечения: от кросс-ассемблеров до операционных систем реального времени, а также готовых аппаратных и программных решений.

Блок системной интеграции позволяет подключать внешние устройства и память с минимальными аппаратными затратами и содержит независимый канал ПДП общего назначения, контроллер прерываний, таймеры, тактовый генератор, программируемые выборки внешних устройств, контроллер регенерации динамической памяти.

|

|

|

МС68360 выпускается в нескольких модификациях, среди которых в первую очередь можно выделить МС68МН360. Этот контроллер поддерживает до 32 каналов HDLC на одном SCC, что позволяет легко обрабатывать потоки данных с временным разделением каналов, например, ИКМ-30 или ISDN PRI. Типичными применениями МС68MH360 являются: оборудование ИКМ, цифровые АТС различного уровня, сетевое оборудование, станции сотовой связи. МС68EN360 поддерживает Ethernet на любом из каналов SCC, обеспечивая функции контроля доступа к среде (MAC), полную обработку коллизий, обнаружение длинных фреймов и другие функции при скорости обмена до 10 Мбит/с.

Сетевые процессоры

Процессоры серии IXP12хх являются представителями семейства сетевых процессоров, производимых компанией Intel в рамках IXA.

Архитектура Internet Exchange включает в себя следующие компоненты:

- сетевые процессоры серии IXP;

- коммутационные контроллеры приложений серии IXE для сетей ATM, Gigabit и 10/100Mb Ethernet. Эти высокопроизводительные устройства предоставляют системным разработчикам возможность сократить сроки поставки своей продукции на рынок и обеспечить ее полную совместимость с новейшими общепринятыми стандартами;

- форматирующие устройства серии IXF для форматирования ячеек ATM, фреймов T1/E1 и Sonet/SDH, пакетов данных Gigabit и 10/100Mb Ethernet;

- компоненты физического уровня серии LXT для сопряжения сетевых устройств, работающих в стандартах T1/E1, HDSL, HDSL2, Sonet/SDH PHYs, 10/100Mb Ethernet, Gigabit (в том числе основанные на медной технологии). Процессоры IXP

По мере смешения голосовых сетей и сетей передачи данных, пересечение открытых и частных сетей все острее требует от производителей оборудования создания основанных на открытых стандартах устройств, способных поддерживать несколько услуг одновременно. По мере того, как повышаются требования поставщиков услуг к интеллектуальности и гибкости сетей, все отчетливее ощущается важность наличия в центре сервисной инфраструктуры перепрограммируемых сетевых процессоров.

Каждый тип процессоров представлен определенным семейством, включающим несколько его модификаций. Семейство процессоров IXP представлено более чем пятью моделями, основное отличие которых заключается в производительности, а следовательно, и пригодности для создания различного телекоммуникационного оборудования. Процессоры 12хх относятся к простейшей линейке сетевых процессоров IXP.

Сетевой процессор IXP1200

Ключевым элементом архитектуры IX является сетевой процессор IXP1200, совместимый со всем спектром коммутирующих и форматирующих устройств, а также компонентов физического уровня. Шина IX сетевого процессора IXP1200 позволяет поручить ему выполнение сложных сетевых функций (например, контроль за шифрованием и обеспечением качества обслуживания), освободив от них коммутирующие устройства IXE в целях соблюдения приоритетности и обеспечения управления.

Сетевому процессору IXP1200 отводятся функции обработки, преобразования и маршрутизации пакетов данных, передаваемых по сетям всех типов. Сетевой процессор IXP1200 обладает мощностью, достаточной для выполнения вычислений в процессе передачи данных, а также определенных задач управления сетевой системой.

Сетевой процессор IXP1200 объединил в себе два вычислительных компонента, играющих важную роль в большинстве сетевых систем: встроенный микропроцессор и контроллеры передачи данных со скоростью, сравнимой с кабельной трансляцией.

Встроенный микропроцессор StrongARM, совместимый с 32-разрядной архитектурой ARM®, служит для выполнения задач управления сетью, 6 программируемых микроконтроллеров ведут многопоточную обработку данных, перемещаемых по сети со скоростью трансляции по кабелю. Одновременно могут выполняться 7 различных сетевых задач, а 18 других ставятся в очередь для выполнения в течение одного цикла. Такая контекстно-зависимая подкачка в режиме нулевого ожидания обеспечивается специализированными инструкциями микроконтроллеров.

Каждый процессор IXP1200 способен направлять 3 млн пак/с, а с учетом объединения нескольких процессоров, производительность системы составит 1,5 Тбит/с.

IXP1200 можно применять в разработке маршрутизаторов, переключателей и концентраторов, поддерживающих такие протоколы передачи данных, как Gigabit Ethernet, Sonet и ATM.

Архитектура IXP1200

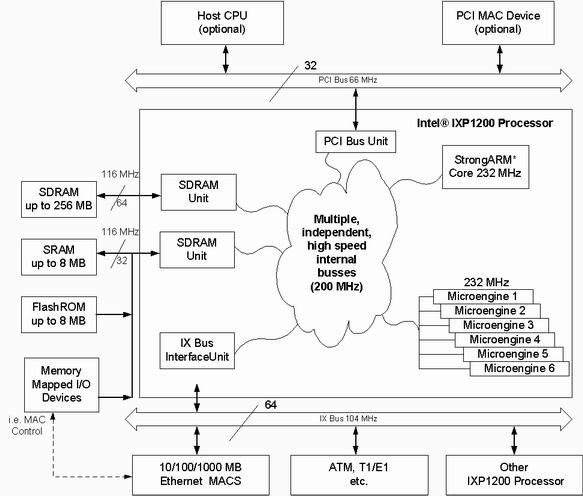

Кристалл процессора IXP1200 содержит процессорное ядро StrongARM и 6 независимых 32-битных RISC микропроцессоров, устройства SRAM, SDRAM, PCI и IX контроллеры шины (рис. 15.3).

Рис.15. 3. Структурная схема процессора IXP1200

Операционные частоты 166–232 МГц. Производительность процессора составляет 3 млн пак/с, что дает 1,5 Гбит/с. Производительность может быть увеличена, если организовать подключение нескольких процессоров параллельно. Таким образом, объединив 8 процессоров можно достичь производительности 24 Mpps.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература: 9 [236-283], 10 [35-61]

Контрольные вопросы:

1. Назначение коммуникационных процессоров?

2. Назначение сетевых процессоров?

3. Структура и состав коммуникационного процессора MC68360?

4. Структура и состав сетевого процессора IXP1200?

5. дискретизация?

6. Особенности коммуникационных процессоров?

7. Особенности сетевых процессоров?

Экзаменационные вопросов по курсу:

1. Способы представления Булевых функций.

2. Булевые функций одной переменной.

3. Булевые функций от двух переменных.

4. Минимизация булевых функций

5. Основные формы представления чисел.

6. Представление чисел с фиксированной запятой.

7. Представление чисел с плавающей запятой.

8. Кодирование десятичных чисел.

9. Перевод чисел из одной системы счисление в другую.

10. Операция сложения двоичных чисел.

11. Операция сложения двоичных чисел в системе 2421.

12. Операция сложения двоичных чисел в системе 8421+3.

13. Операция сложения двоичных чисел в системе 8421+6.

14. Операция вычитания двоичных чисел.

15. Операция вычитания двоичных чисел в системе 2421.

16. Операция вычитания двоичных чисел в системе 8421+3.

17. Операция вычитания двоичных чисел в системе 8421+6.

18. Операция умножения двоичных чисел.

19. Операция деления двоичных чисел.

20. Особенности выполнения операции умножения десятичных чисел.

21. Особенности выполнения операции деления десятичных чисел.

22. Комбинационные схемы.

23. Анализ и синтез комбинационных схем.

24. Последовательные схемы – элементарные автоматы.

25. Автомат Миля.

26. Автомат Мура.

27. Схемы И,ИЛИ и НЕ, таблицы истинности.

28. Дешифраторы.

29. Шифраторы.

30. Мультиплексоры.

31. Демультиплексоры.

32. Компаратор.

33. Запоминающие элементы.

34. RS- триггер.

35. JK- триггер.

36. D- триггер.

37. DV- триггер.

38. T- триггер.

39. TV- триггер.

40. Однотактные триггеры.

41. Двухтактные триггеры.

42. Регистры. Классификация.

43. Последовательный регистр

44. Параллельный регистр.

45. Регистр сдвига.

46. Универсальный регистр.

47. Счетчики. Классификация.

48. Последовательные счетчики.

49. Прямые и обратные счетчики.

50. Полусумматор.

51. Полный одноразрядный сумматор.

52. Многоразрядный последовательный сумматор,

53. Многразрядный накпливающий сумматор.

54. Арифметическое-логическое устройство.

55. Запоминающие укстройства (ЗУ). Классификация.

56. Оперативные ЗУ.

57. Постоянные ЗУ.

58. Сверхоперативное ЗУ.

59. Статическое ОЗУ.

60. Динамическое ОЗУ.

61. Микропроцессор (МП). Определение и классификация.

62. Командный цикл МП.

63. Машинный цикл МП.

64. Машинный такт.

65. Основной состав и принцип работы МП.

66. Запись информации.

67. Считывание информации.

68. Процесс прерывания.

69. Прямой доступ к памяти (ПДП).

70. МП Intel 8080.

71. МП Intel 8086.

72. МП Intel 8085.

73. МП Intel 80286.

74. МП Intel 80386.

75. МП Intel 80486.

76. МП Pentium.

77. Микропроцессорная система (МПС). Определение и классификация.

78. Основной состав и принцип работы МПС.

79. Основное ядро МПС.

80. Шинные формирователи.

81. Контроллер ввода с клавиатуры и вывода на индикаторы.

82. Контроллер последовательного ввода/вывода.

83. Контроллер прямого доступа к памяти.

84. Контроллер параллельного ввода/вывода информации.

85. Сопроцессоры.

86. Микроконтроллер. Определение и классификация.

87. Микроконтроллеры с CISC архитектурой.

88. Микроконтроллеры с RISC архитектурой.

89. Сигнальный процессор. Определение и классификация.

90. Интерфейсы микро-ЭВМ.

91. Интерфейс PCI.

92. Однокристальный микро-ЭВМ МК48.

93. Однокристальный микро-ЭВМ МК51.

94. Пример использование МК 51.

95. Сигнальные процессоры фирмы Motorolla

96. Сигнальные процессоры фирмы Texas Instruments

97. Основные функций МП.

98. Арбитраж в интерфейсах МПС.

99. Коммуникационные процессоры.

100. Сетевые процессоры.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 1983; Нарушение авторских прав?; Мы поможем в написании вашей работы!