КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Типы команд

|

|

|

|

Классификация по месту хранения операндов

Количество команд и их сложность, безусловно, являются важнейшими факторами, однако не меньшую роль при выборе АСК играет ответ на вопрос о том, где могут храниться операнды и каким образом к ним осуществляется доступ. С этих позиций различают следующие виды архитектур системы команд:

- стековую;

- аккумуляторную;

- регистровую;

- с выделенным доступом к памяти.

Выбор той или иной архитектуры влияет на принципиальные моменты: сколько адресов будет содержать адресная часть команд, какова будет длина этих адресов, насколько просто будет происходить доступ к операндам и какой, в конечном итоге, будет общая длина команд.

Стековая архитектура

Стеком называется память, по своей структурной организации отличная от основной памяти ВМ. Стек образует множество логически взаимосвязанных ячеек (рис. 1.7), взаимодействующих по принципу «последним вошел, первым вышел» (LIFO, Last In First Out).

| |||

|

| Push a | Push b | Push c | Pop c | Pop b | |||||

| вершина стека | a | b | c | b | a | ||||

| a | b | a | |||||||

| a | |||||||||

Рис. 1.7. Принцип работы стека

Верхнюю ячейку называют вершиной стека. Для работы со стеком предусмотрены две операции: Push (проталкивание данных в стек) иРор(выталкивание данных из стека). Запись возможна только в верхнюю ячейку стека, при этом вся хранящаяся в стеке информация предварительно проталкивается на одну позицию вниз. Чтение допустимо также только из вершины стека. Извлеченная информация удаляется из стека, а оставшееся его содержимое продвигается вверх. В вычислительных машинах, где реализована АСК на базе стека (их обычно называют стековыми), операнды перед обработкой помещаются в две верхних ячейки стековой памяти. Результат операции заносится в стек.

|

|

|

Аккумуляторная архитектура

Архитектура на базе аккумулятора исторически возникла одной из первых. В ней для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр – аккумулятор. В этот же регистр заносится и результат операции. Поскольку адрес одного из операндов предопределен, в командах обработки достаточно явно указать местоположение только второго операнда. Изначально оба операнда хранятся в основной памяти, и до выполнения операции один из них нужно загрузить в аккумулятор. После выполнения команды обработки результат находится в аккумуляторе и, если он не является операндом для последующей команды, его требуется сохранить в ячейке памяти.

Регистровая архитектура

В машинах данного типа процессор включает в себя массив регистров (регистровый файл), известных как регистры общего назначения (РОН). Эти регистры, в каком-то смысле, можно рассматривать как явно управляемый кэш для хранения недавно использовавшихся данных.

Размер регистров обычно фиксирован и совпадает с размером машинного слова. К любому регистру можно обратиться, указав его номер. Количество РОН в архитектурах типа CISC обычно невелико (от 8 до 32), и для представления номера конкретного регистра необходимо не более пяти разрядов, благодаря чему в адресной части команд обработки допустимо одновременно указать номера двух, а зачастую и трех регистров (двух регистров операндов и регистра результата). RISC-архитектура предполагает использование существенно большего числа РОН (до нескольких сотен), однако типичная для таких ВМ длина команды (обычно 32 разряда) позволяет определить в команде до трех регистров.

|

|

|

Регистровая архитектура допускает расположение операндов в одной из двух запоминающих сред: основной памяти или регистрах. С учетом возможного размещения операндов в рамках регистровых АСК выделяют три подвида команд обработки:

- регистр-регистр;

- регистр-память;

- память-память.

В варианте «регистр-регистр» операнды могут находиться только в регистрах. В них же засылается и результат. Подтип «регистр-память» предполагает, что один из операндов размещается в регистре, а второй в основной памяти. Результат обычно замещает один из операндов. В командах типа «память-память» оба операнда хранятся в основной памяти. Результат заносится в память. Каждому из вариантов свойственны свои достоинства и недостатки.

Таблица 1.2.

Сравнительная оценка регистровой архитектуры

| Вариант | Достоинства | Недостатки |

| Регистр-регистр | Простота реализации, фиксированная длина команд, простая модель формирования объектного кода при компиляции программ, возможность выполнения всех команд за одинаковое количество тактов | Большая длина объектного кода, из-за фиксированной длины команд часть разрядов кода при компиляции в коротких командах не используется |

| Регистр-память | Данные могут быть доступны без загрузки в регистры процессора, простота кодирования команд, объектный код получается достаточно компактным | Потеря одного из операндов при записи результата, длинное поле адреса памяти в коде команды сокращает место под номер регистра, что ограничивает общее число РОН |

| Память-память | Компактность объектного кода, малая потребность в регистрах для хранения промежуточных данных | Разнообразие форматов команд и времени их исполнения, низкое быстродействие из-за обращения к памяти |

Архитектура с выделенным доступом к памяти

В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. В английской транскрипции данную архитектуру называют Load / Store Architecture. Команда lоad (загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра). Пересылка информации в противоположном направлении производится командой store (сохранение). Операнды во всех командах обработки информации могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения). Результат операции также заносится в регистр. В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. Допускается наличие в АСК ограниченного числа команд, где операнд является частью кода команды.

|

|

|

АСК с выделенным доступом к памяти характерна для всех вычислительных машин с RISC-архитектурой. Команды в таких ВМ, как правило, имеют длину 32 бита и трехадресный формат. В качестве примеров вычислительных машин с выделенным доступом к памяти можно отметить НР РА-RISC, IВМ RS 6000, Sun SPARC, МIРS R4000, DЕС Аlрhа и т. д. К достоинствам АСК следует отнести простоту декодирования и исполнения команды.

Несмотря на различие в системах команд разных ВМ, некоторые основные типы операций могут быть найдены в любой из них. Для описания этих типов примем следующую классификацию:

- команды пересылки данных;

- команды арифметической и логической обработки;

- операции с десятичными числами;

- команды преобразования;

- команды ввода/вывода;

- команды управления потоком команд.

Команды пересылки данных

Рассматриваемая группа команд обеспечивает передачу информации между процессором и ОП, внутри процессора и между ячейками памяти. Пересылочные операции внутри процессора имеют тип «регистр-регистр». Передачи между процессором и памятью относятся к типу «регистр-память», а пересылки в памяти – к типу «память-память».

Команды арифметической и логической обработки

В данную группу входят команды, обеспечивающие арифметическую и логическую обработку информации в различных формах ее представления. Для каждой формы представления чисел в АСК обычно предусматривается некий стандартный набор операций.

Помимо вычисления результата выполнение арифметических и логических операций сопровождается формированием в АЛУ признаков (флагов), характеризующих этот результат. Наиболее часто фиксируются такие признаки, как: нулевой результат; отрицательный результат; переполнение разрядной сетки; наличие переноса.

|

|

|

Операции с целыми числами

К стандартному набору операций над целыми числами, представленными в форме с фиксированной запятой, следует отнести:

- арифметические операции с двумя операндами: сложение, вычитание, умножение и деление;

- арифметические операции с одним операндом: вычисление абсолютного значения (модуля) операнда, изменение знака операнда;

- операции сравнения, обеспечивающие сравнение двух целых чисел и выработку признаков, характеризующих соотношение между сопоставляемыми величинами ( ).

).

Операции с числами в форме с плавающей запятой

Для работы с числами, представленными в форме с плавающей запятой, в АСК большинства машин предусмотрены:

- основные арифметические операции: сложение, вычитание, умножение и деление;

- операции сравнения, обеспечивающие сравнение двух вещественных чисел с выработкой признаков:  ;

;

- операции преобразования: формы представления (между фиксированной и плавающей запятой), формата представления (с одинарной и двойной точностью).

Логические операции

Стандартная система команд ВМ содержит команды для выполнения различных логических операций над отдельными битами слов или других адресуемых единиц. Такие команды предназначены для обработки символьных и логических данных. Минимальный набор поддерживаемых логических операций – это «НЕ», «И», «ИЛИ» и сложение по модулю 2.

Операции сдвигов

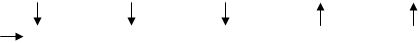

В дополнение к побитовым логическим операциям, практически во всех АСК предусмотрены команды для реализации операций логического, арифметического и циклического сдвигов.

Операции с десятичными числами

Десятичные числа представляются в ВМ в двоично-кодированной форме. В вычислительных машинах первых поколений для обработки таких чисел предусматривались специальные команды, обеспечивавшие выполнение основных арифметических операций (сложение, вычитание, умножение и деление). В АСК современных машин подобных команд обычно нет, а соответствующие вычисления имитируются с помощью команд целочисленной арифметики.

Команды преобразования

Команды преобразования осуществляют изменение формата представления данных. Примером может служить преобразование из десятичной системы счисления в двоичную или перевод 8-разрядного кода символа из кодировки АSCII в кодировку ЕВСDIС, и наоборот.

Команды ввода/вывода

Команды этой группы могут быть подразделены на команды управления периферийным устройством (ПУ), проверки его состояния, ввода и вывода.

Команды управления системой

Команды, входящие в эту группу, являются привилегированными и могут выполняться, только когда центральный процессор ВМ находится в привилегированном состоянии или выполняет программу, находящуюся в привилегированной области памяти (обычно привилегированный режим используется лишь операционной системой). Так, лишь эти команды способны считывать и изменять состояние ряда регистров устройства управления.

Команды управления потоком команд

Концепция фон-неймановской вычислительной машины предполагает, что команды программы, как правило, выполняются в порядке их расположения в памяти. Для получения адреса очередной команды достаточно увеличить содержимое счетчика команд на длину текущей команды. В то же время основные преимущества ВМ заключаются именно в возможности изменения хода вычислений в зависимости от возникающих в процессе счета результатов. С этой целью в АСК вычислительной машины включаются команды, позволяющие нарушить естественный порядок следования и передать управление в иную точку программы. В адресной части таких команд содержится адрес точки перехода (адрес той команды, которая должна быть выполнена следующей). Переход реализуется путем загрузки адреса точки перехода в счетчик команд (вместо увеличения содержимого этого счетчика на длину команды).

В системе команд ВМ можно выделить три типа команд, способных изменить последовательность вычислений:

- безусловные переходы;

- условные переходы (ветвления);

- вызовы процедур и возвраты из процедур.

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 1840; Нарушение авторских прав?; Мы поможем в написании вашей работы!