КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Архитектуры ЭВМ

|

|

|

|

Функциональные блоки (агрегаты, устройства)

Принципы фон Неймана

В основу архитектуры большинства компьютеров положены следующие общие принципы, сформулированные в 1945 г. американским ученым Дж. фон Нейманом в отчете по ЭВМ EDVAC — принцип программного управления; принцип однородности памяти; принцип адресности. По истечении более 60 лет большинство компьютеров так и имеют «фон-неймановскую архитектуру», причем обычно принципы фон Неймана реализованы в следующей форме:

• оперативная память (ОП или ОЗУ — оперативное запоминающее устройство) организована как совокупность машинных слов (МС) фиксированной длины или разрядности (имеется в виду количество двоичных единиц или бит, содержащихся в каждом МС). Например, ранние ПЭВМ имели разрядность 8, затем появились 16-разрядные, а затем — 32- и 64-разрядные машины. В свое время существовали даже 45-разрядные (М-20, М-220), 35-разрядные (Минск-22, Минск-32) и др. машины;

• ОП образует единое адресное пространство, адреса МС возрастают от младших к старшим;

• в ОП размещаются как данные, так и программы, причем в области данных одно слово, как правило, соответствует одному числу, а в области программы — одной команде (машинной инструкции — минимальному и неделимому элементу программы);

• команды выполняются в естественной последовательности (по возрастанию адресов в ОП), пока не встретится команда управления (условного/безусловного перехода, или ветвления — branch), в результате которой естественная последовательность нарушится;

• ЦП может произвольно обращаться к любым адресам в ОП для выборки и/или записи в МС чисел или команд.

|

|

|

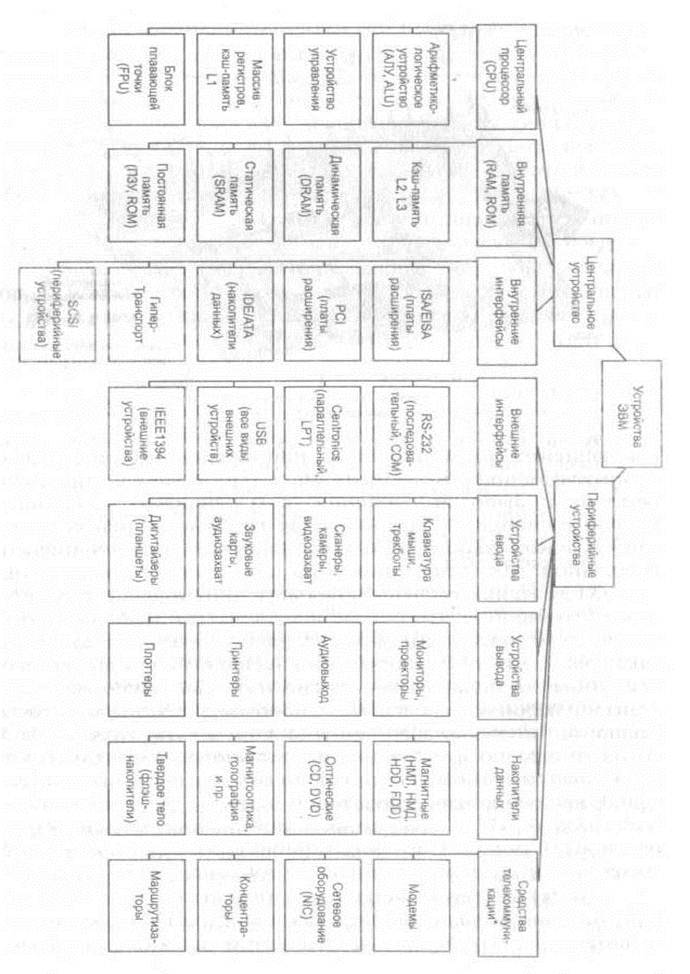

Краткий список основных устройств, входящих в состав вычислительных машин, приведен на рис. 1.

Рис. 1 Перечень устройств ЭВМ

Рис. 1 Перечень устройств ЭВМ

Центральное устройство (ЦУ) представляет основную компоненту ЭВМ и в свою очередь включает ЦП — центральный процессор (central processing unit — CPU) и ОП (Main Storage, Core Storage, Random Access Memory — RAM).

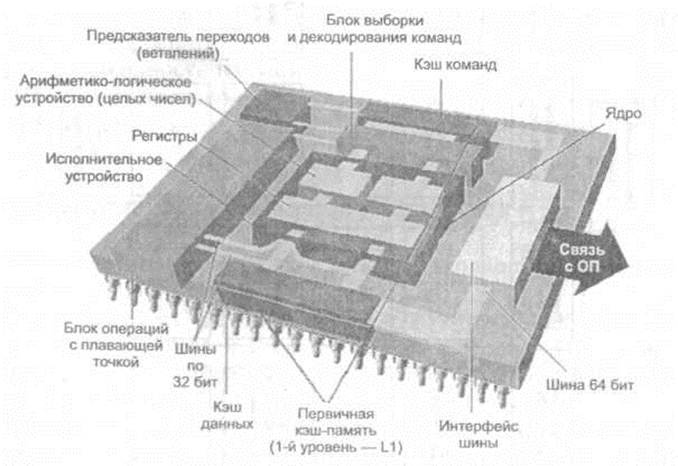

Процессор непосредственно реализует операции обработки информации и управления вычислительным процессом, осуществляя выборку машинных команд и данных из оперативной па мяти, их выполнение и запись результатов в ОП, включение и отключение ВУ. Рассмотрим в качестве примера процессор Intel Pentium (рис. 2).

Рис.2 Основные компоненты процессора Pentium

Он состоит из следующих блоков:

• ядро (Core). Основное исполнительное устройство, которое включает в себя арифметико-логическое устройство (АЛУ, или Arithmetic and Logical Unit — ALU) регистры, конвейеры. АЛУ — часть процессора, выполняющая арифметические и логические операции над данными, работает в соответствии с сообщаемыми ему кодами операций, которые должны быть выполнены над переменными, помещаемыми в регистры. Повышение производительности достигалось благодаря двум конвейерам, позволяющим выполнить одновременно несколько инструкций. Это два параллельных 5-ступенчатых конвейера обработки целых чисел, которые позволяют читать, интерпретировать, исполнять две команды одновременно. Целочисленные команды могут выполняться за один такт синхронизации. Эти конвейеры неодинаковы: U-конвейер выполняет любую команду системы команд семейства 86; V-конвейер выполняет только «простые» команды, т. е. команды, которые полностью встроены в схемы МП и не требуют микропрограммного управления (microcode) при выполнении (это команды, до- пускающие спаривание с другими командами: регистр—регистр, память—регистр, регистр—память, переходы, вызовы, арифметико-логические операции);

• предсказатель переходов (Branch Predictor) — блок, который «пытается угадать» направление ветвления программы и заранее загрузить информацию в блоки предвыборки и декодирования команд;

|

|

|

• буфер адреса переходов (Branch Target Buffer — В ТВ). Обеспечивает динамическое предсказание переходов. Он улучшает выполнение команд путем запоминания состоявшихся переходов (256 последних переходов) и с опережением выполняет наиболее вероятный переход при выборке команды ветвления. При статических методах предсказания предписывается всегда выполнять или нет определенные виды переходов. При динамических методах исследуется поведение команд перехода за предшествующий период;

• блок плавающей точки (Floating Point Unit). Выполняет обработку чисел с плавающей точкой;

• кэш-память 1-го уровня (Level I cache). Процессор имеет два банка памяти по 8 Кбайт, один — для команд, второй — для данных, которые обладают большим быстродействием, чем более емкая внешняя кэш-память (L2 cache).

• интерфейс шины (Bus Inte rface). Передает в ЦП поток команд и данных, а также передает данные из ЦП.

Внешние (периферийные) устройства (ВУ). ВУ обеспечивают взаимодействие с окружающей средой — пользователями, объектами управления, другими машинами.

Интерфейсы служат для сопряжения центральных узлов машины с ее внешними устройствами.

Однотипные ЦУ и устройства хранения данных могут использоваться в различных типах машин. Известны примеры того, как фирмы, начавшие свою деятельность с производства управляющих машин, совершенствуя свою продукцию, перешли к выпуску систем, которые в зависимости от конфигурации ВУ могут исполнять как роль универсальных, так и управляющих машин (машины Hewlett-Packard — HP и Digital Equipment Corporation — DEC).

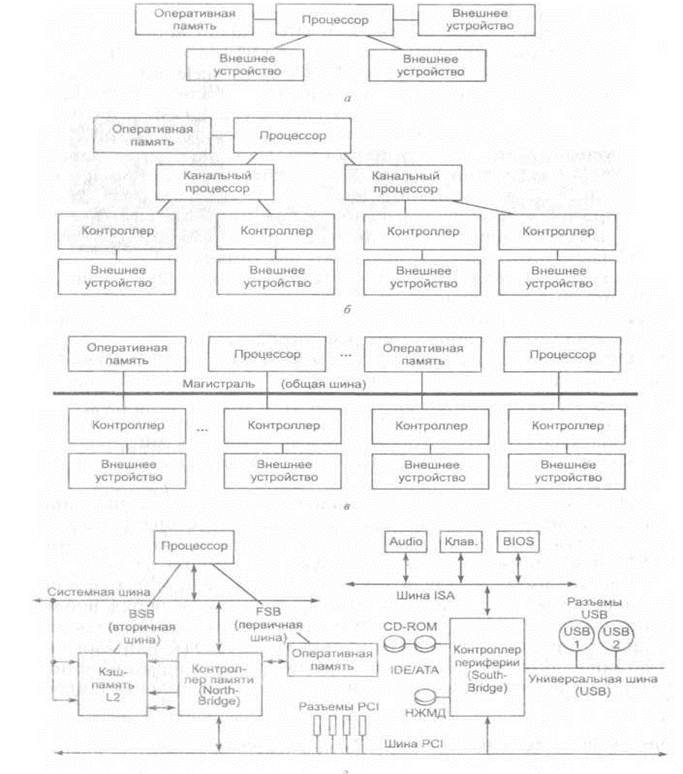

Архитектура «звезда». Здесь процессор (ЦУ) — рис. 3, а — соединен непосредственно с ВУ и управляет их работой (ранние модели машин). Этот тип также именуется классическая архитектура (фон Неймана) — одно арифметико-логическое устройство (АЛУ), через которое проходит поток данных, и одно устройство управления (УУ), через которое проходит поток команд — программа. Это однопроцессорный компьютер.

Принстонская и гарвардская архитектуры. Архитектуру фон Неймана часто отождествляют спринстонской архитектурой, которая характеризуется использованием общей оперативной памяти для хранения программ и данных. Гарвардская же архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. Элементы гарвардской архитектуры часто используются в современных процессорах, когда в кэш-памяти ЦП выделяется память команд (I-cache) и память данных (D-cache).

|

|

|

Иерархическая архитектура (рис. 3, б) — ЦУ соединено с периферийными процессорами (вспомогательными процессорами, каналами, канальными процессорами), управляющими в свою очередь контроллерами, к которым подключены группы ВУ (системы IBM 360-375, ЕС ЭВМ);

Maгucmpaлlьнaя структура (общая шина — unibas, рис. 3, в) — процессор (процессоры) и блоки памяти (ОН) взаимодействуют между собой и с ВУ (контроллерами ВУ) через внутренний канал, общий для всех устройств (машины DEC, IBM PC-совместимые ПЭВМ).

Технически шина представляет собой набор проводников (линий), соединяющий различные компоненты компьютера для подвода к ним питания и обмена данными. В минимальной комплектации шина имеет три типа линий: управления; адреса; данных.

К этому типу архитектуры относится также архитектура персонального компьютера (ПК). Конечно, реальная структура ПК (рис. 3, г) отличается от теоретических схем — здесь используется несколько разновидностей шинных интерфейсов, которые соединяются между собой мостами — контроллерами памяти (Northbridge, «Северный мост») и периферийных устройств (Southbndge, «Южный мост»).

Рис. 3 Основные классы архитектур ЭВМ

Рис. 3 Основные классы архитектур ЭВМ

а – централизованная, б – иерархическая, в – магистральная, г – общая структура ПК

Здесь приведен пример набора микросхем (chipset) Triton 430 ТХ:

• Northbridge — микросхема 82439ТХ System Controller, MTXC. Интегрирует контроль кэш-памяти, ОП и шины PCI;

• Southbridge - 82371АВ PCI ISA IDE Xcelerator, PIIX4 - многофункциональное устройство, реализующее связь PCI— ISA, функции концентратора (hub) USB и функции управления потреблением электроэнергии (Enhanced Power Management). Здесь реализована Dynamic Power Management Architecture (DPMA) — архитектура динамического управления энергопотреблением. Поддерживается также протокол прямого обращения к памяти (Ultra DMA), который обеспечивает скорость передачи в 33 Мбайт/с с НЖМД.

|

|

|

Современные системы включают два типа шин:

• системная шина, соединяющая процессор с ОП и кэш-памятью 2-го уровня;

• множество шин ввода-вывода, соединяющие процессор с различными периферийными устройствами.

Системная шина при архитектуре DIB (Dual independent bus, двойная независимая шина) физически разделена на две (рис. 3, г):

• первичная шина (FSB, frontside bus), связывающая процессор с ОП и ОП с периферийными устройствами;

• вторичная шина (BSB, backside bus) для связи с кэш-памятью.

Использование двойной независимой шины повышает производительность за счет возможности для процессора параллельно обращаться к различным уровням памяти. Обычно термины «FSB» и «системная шина» используют как синонимы.

Следует иметь в виду, что терминология, используемая в настоящее время для описания интерфейсов, не является вполне однозначной и ясной. Системная шина часто упоминается как «главная шина», «хост-шина», «шина процессора», или «локальная шина». Для шин ввода-вывода используются термины «шина расширения», «внешняя шина» и опять же — «локальная шина».

|

|

|

|

|

Дата добавления: 2013-12-13; Просмотров: 938; Нарушение авторских прав?; Мы поможем в написании вашей работы!