КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Архитектура микроЭВМ

|

|

|

|

Как было указано ранее, особенностью архитектуры микроконтроллера является логическое и физическое разделение памяти на программную и данных. Программная память представлена только ПЗУ, так как в К1816 отсутствуют программные средства оперативной записи команд и программ.

Память может расширяться путем подключения внешних БИС: программная — на 2 Кбайта, данных — на 256 байт. Возможно также расширение средств ввода-вывода за счет использования интерфейсных БИС серии К580.

Таблица 1

| Пр.память | Объём пр.памяти | Расширение пр. памяти | Максимальная тактовая частота, МГц | ОЗУ | Расширение озу | |

| 1816ВЕ35 | ----- | ------- | ||||

| 1816ВЕ39 | ----- | -------- | ||||

| 1816ВЕ48 | ППЗУ | 1К | ||||

| 1816ВЕ49 | ПЗУ | 2К | ||||

| 1816ВЕ51(1) | ППЗУ | 4К | 64К | |||

| 1816ВЕ51(1) | ПЗУ | 4К | 64К | |||

| 1816ВЕ51(1) | ---------- | -------- | 64К |

Структурная схема контроллера представлена на рис.1. Основу микроконтроллера составляет системная шина, которая связывает между собой все основные функциональные узлы микросхемы: блок управления, арифметико-логического устройство, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. По такой схеме построены все представители семейства MCS-48. Различные микросхемы этого семейства различаются только объёмом внутренней памяти. Система команд всех контроллеров семейства MCS-48 содержит 96 базовых команд с форматом 1 или 2 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одного типа микросхем на другой. Рассмотрим подробнее назначение каждого блока.

|

|

|

Рисунок 1. Структурная схема контроллера К1816ВЕ48

Блок управления и синхронизации

Блок управления и синхронизации

Блок управления и синхронизации предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков микроконтроллера во всех режимах работы. В состав блока управления входят:

· устройство формирования временных интервалов,

· логика ввода-вывода,

· регистр команд,

· дешифратор команд, логика управления ЭВМ.

· Устройство синхронизации и управления связано с периферийными устройствами 13-разрядной шиной С {12: 0}, отдельные провода которой несут на себе следующие сигналы (в скобках указаны аналоги сигналов МП580):

· BQ1, BQ2 - подключение кварца или LC — цепи синхронизации встроенного тактового генератора или входа внешнего тактового генератора;

· WR (WR) — запись во внешнюю память данных, запись из порта BUS во внешнее устройство;

· RD (DBIN) — чтение из внешней памяти или из внешних устройств, подключенных к порту BUS

· ALE (C) (address latch enable) — стробирование внешней памяти;

· SR (RESET) (set-reset) - инициализация микроЭВМ;

· INT (INT) — сигнал запроса на прерывание;

· SS — организация пошагового выполнения программы (используется совместно с ALE);

· PME (periphery memory enable) - стробирование внешней памяти при чтении;

· EMA (external memory access} — доступ к внешней памяти. Используется также при программировании и проверке ППЗУ; PR (periphery register) — расширение каналов ввода/вывода. Используется также при программировании ППЗУ; ТО — ввод условия для JTO/JNTO или выход тактовых сигналов после выполнения команды ENTO CLK; TI — ввод условия для JT1/JNT1 или ввод счетчика внешних событий после выполнения команды STRT CNT.

·

· Блок программного управления преобразует коды команд программы в сигналы управления. Он включает в себя счетчик команд (PC), дешифратор адреса команды, ППЗУ, регистр команды (IR) и дешифратор команды (IDC). В отличие от МП580, этот блок может работать как с внутренней, так и с внешней памятью. В последнем случае код адреса РС {11: 0} подается на внешнюю программную память, а байтный код команды записывается непосредственно в регистр команды.

|

|

|

Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Генератор построен на внутреннем инверторе и внешнем кварцевом или LC резонаторе. Допустимая частота кварцевого резонатора от 1 до 6 МГц. Схемы задающих генераторов тактовой частоты с использованием внутренней и внешней синхронизации приведены на рисунке 2.

Рисунок 2. Схемы генераторов тактовой частоты.

Нужно отметить, что запуск задающего генератора этого микроконтроллера был затруднённым (жёсткий режим самовозбуждения), поэтому для надёжного запуска задающего генератора следовало использовать либо внешний генератор, либо шунтировать ножки XTAL1 и XTAL2 внешним резистором.

Практически все команды микроконтроллера выполняются за один или два машинных цикла. Обозначим частоту задающего генератора через Fг. Тогда длительность машинного цикла равна 15/Fг или составляет 15 периодов сигнала задающего генератора. Именно с такой частотой выдаётся сигнал стробирования адреса ALE. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода и системную шину микроконтроллера.

Сброс микроконтроллера можно осуществить при помощи конденсатора, подключенного к ножке сброса RESET, как показано на рисунке 3. Минимальное время сброса контроллера 50 мс. В настоящее время для этой цели лучше бы подошла микросхема супервизора питания ADM809. После сброса микроконтроллера обнуляется содержимое счётчика команд PC, указателя стека в составе регистра PSW, выбираются 0 банк регистров и нулевой банк памяти программ. Запрещаются прерывания.

Рисунок 3. Схемы сброса микропроцессора.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды, считанной из ПЗУ.

|

|

|

Арифметико-логический блок представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛБ состоит из:

· регистров временного хранения TMP1 и TMP2,

· аккумулятора (ACC),

· ПЗУ констант,

· арифметико-логического устройства,

· регистра состояния программ (PSW).

Регистры временного хранения - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Регистры временного хранения информации программно не доступны.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Арифметико-логическое устройство представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций И, ИЛИ, исключающего ИЛИ инкремент, декремент, инверсию, циклический сдвиг вправо и влево, десятичную коррекцию содержимого аккумулятора.

При выполнении операций обработки данных в АЛУ вырабатываются флаги, которые сохраняются в регистре состояния программы PSW.

Кроме того, вырабатываются флаги, по которым осуществляется переход в командах условного перехода, такие как флаг нулевого содержимого аккумулятора и флаг наличия единицы в выбранном бите аккумулятора.

Блок обработки прерываний предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ. Опрос входа запроса прерывания INT производится во время выдачи сигнала ALE. Передача управления на вектор прерывания 3 произойдёт только по завершению цикла команды. При обработке прерывания содержимое счётчика команд и старшей тетрады слова состояния программы сохраняется в стеке. При обработке прерывания запросы прерываний игнорируются до выхода из подпрограммы обработки прерывания по команде RETR. Прерывания могут быть запрещены командой DIS и разрешены командой EN. Приоритет от внешнего прерывания выше приритета прерывания от внутреннего таймера, то есть если эти прерывания возникнут одновременно, то будет осуществлён переход на вектор прерывания 3

|

|

|

Счетчик команд (Program Counter) предназначен для формирования текущего 11-разрядного адреса памяти программ. В состав счетчика команд входят 11-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1). Кроме того, под управлением команд SEL MB0 и SEL MB1 могут переключаться страницы памяти программ.

ОЗУ - память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы. Формат регистра PSW приведён ниже:

| Номер бита | ||||||||

| Имя флага | C | AC | F0 | BS | - | S2 | S1 | S0 |

Память программ предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах семейства применяются ПЗУ различного объёма. В микросхеме 1816ВЕ35 внутренняя память программ отсутствует вовсе.

Устройство параллельных портов микроконтроллеров MCS-48

Порты P1, P2 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией микроконтроллера с внешними устройствами, образуя 16 линий ввода- вывода. Каждый из портов содержит восьмиразрядный регистр, позволяющий устанавливать (запись '1') или сбрасывать (запись '0') любой разряд этого регистра с помощью программного обеспечения. Выходы регистров квазидвунаправленного порта соединены с внешними ножками микросхемы. Упрощенная схема одного разряда порта показана на рисунке 4.

При записи в разряд порта (в триггере Т) логического '0' выходной транзистор открывается и на выводе микросхемы появляется низкий потенциал, изменить который извне невозможно. Поэтому при опросе ножки микросхемы входная информация в этом случае всегда будет восприниматься как логический '0' независимо от состояния выходов внешних устройств. Если в указанный разряд записать логическую '1', то выходной транзистор закрывается и на выводе микросхемы появляется высокий потенциал за счет генератора тока. Он может извне изменен на нулевой потенциал (замыканием этой ножки микросхемы на корпус). В этом случае, считываемая микроконтроллером информация, будет соответствовать информации на выходе внешнего устройства. Поэтому, перед тем как осуществить ввод информации по какому-либо выводу порта, соответствующий разряд необходимо настроить на ввод - записать в него логическую '1'.

Рисунок 4. Упрощенная схема одного бита порта.

Рисунок 4. Упрощенная схема одного бита порта.

|

Порт Р2 используется также для подключения расширителя ввода/вывода и выдачи четырех старших разрядов программного счетчика РС{11: 8 }.

Порт BUS реализует двунаправленный канал передачи данных. Он передает восемь младших разрядов кода адреса команд РС{1: 0} или кода адреса данных ADRD {7: 0} при работе с внешней программной памятью или памятью данных и байт данных D{1: 0} при работе с внешней памятью или схемами расширения (интерфейсные БИС серии К580). По завершению передачи данных порт переходит в третье состояние.

IN A, P1;Скопировать состояние ножек порта P1 в аккумулятор

IN A, P2;Скопировать состояние ножек порта P2 в аккумулятор

Вывод информации через параллельные порты осуществляется командами:

OUTL P1, A;Скопировать содержимое аккумулятора в порт P1

OUTL P2, A;Скопировать содержимое аккумулятора в порт P2

При выводе информации обычно требуется работать с каждым битом порта отдельно. Так как при считывании значения порта на самом деле будет считываться напряжение на внешней ножке микросхемы, то для модификации кода, записываемого в порт нужно хранить его копию во внутренней памяти микроконтроллера. Модификация обычно производится при помощи операции маскирования с использованием команд ORL и ANL.

Порты микросхемы служат для управления внешними устройствами, подключенными к микроконтроллеру. Схема подключения простейших внешних устройств приведена на рисунке 5. Этот рисунок иллюстрирует особенности подключения индикаторов к параллельным портам микроконтроллера MCS-48.

Присутствие в схеме мощного транзистора позволяет подключать к выводам порта светодиодные индикаторы непосредственно без усилителя мощности. Однако при этом необходимо следить за максимальной допустимой мощностью, рассеиваемой на микросхеме и напряжением, подаваемом на светодиод. Эквивалентная схема, на которой показан путь протекания выходного тока порта приведена на рисунке 5. Как видно из этой схемы именно этот ток используется для зажигания светодиода.

|

Для умощнения выводов порта можно применить транзисторный ключ, показанный на рисунке 6. Обратите внимание, что база транзистора подключена непосредственно к выводу порта. Это стало возможным только благодаря использованию в схеме порта генератора тока в верхнем плече выходного каскада (Схему подключения устройств к портам с TTL выходами можно посмотреть здесь). Если выходного тока достаточно для открывания транзисторного ключа, то резистор R2 не используется. Этот резистор подключается для увеличения базового тока транзисторного ключа. На максимальное значение тока через этот резистор накладываются те же ограничения, что и для непосредственного подключения светодиодного индикатора к выводам порта.

Это были рассмотрены схемотехнические особенности применения параллельных портов. Однако управлять напряжением на выходе параллельного порта микроконтроллера можно только при помощи программы. В приведённой на рисунке 6 схеме, для зажигания светодиода VD1, в шестой вывод порта P0 необходимо записать логический 0. Для зажигания светодиода VD2 необходимо в седьмой разряд порта P2 записать логическую единицу.  Рисунок 6. Схема подключения светодиодных индикаторов к параллельному порту.

Рисунок 6. Схема подключения светодиодных индикаторов к параллельному порту.

Для записи числа в порт (изменения потенциалов на ножках микросхемы) можно воспользоваться следующими способами:

1. OUTL (выдача в порт константы), например

2. MOV A, #56h;Установить единичный сигнал на ножках 1,2,4 и 6 порта P2 3. OUTL P2, A;и нулевой потенциал на ножках 0,3,5 и 74. 5. MOV A, #01110011b;Выдать на все восемь выводов порта P1 OUTL P1, A;двоичное число 011100116. ANL (использование логического 'И' для обнуления выбранных маской бит), например:

7. MOV A, 56;Занести в аккумулятор копию порта P18. ANL P1, #11110011b;сформировать низкий потенциал на ножках P1.2 и P1.3 OUTL P1, A;записать новое значение в порт P19. XRL (использование операции исключающее 'ИЛИ' для инвертирования выбранных бит), например

10. MOV A, 56;Занести в аккумулятор копию порта P111. XRL A, #01000010b;инвертировать состояние ножек P1.1 и P1.6 OUTL P1, A;записать новое значение в порт P112. ORL (использование операции логическое 'ИЛИ' для записи единиц в выбранные биты), например

13. MOV A, 56;Занести в аккумулятор копию порта P114. ORL A, #00100001b;выдать высокий потенциал на ножках P1.0 и P1.5 OUTL P1, A;записать новое значение в порт P1По той же причине при настройке выводов порта на выполнение альтернативных функций в соответствующие разряды должны быть записаны логические '1'.

Порт P1. Этот квазидвунаправленный порт никаких особенностей не имеет. При сбросе микросхемы во все разряды порта P2 записываются '1'.

· Порт P2. Младшая тетрада порта может быть использована для передачи старших четырёх бит адреса при работе с внешней памятью программ и внешней памятью данных (с 12- разрядным адресом). Схема использования порта P2 в качестве шины адреса приведена на рисунке 4. При сбросе микросхемы во все разряды порта P2 записываются '1'. Кроме того через младшие четыре разряда порта 2 могут быть использованы для подключения микросхемы расширителя портов.

· Порт D/A. Может быть использован для стробируемого вывода данных. Стробирование данных производится сигналом WR. Над этим портом возможно выполнение логических операций, что может сократить длину программ, приведённых выше, до одной команды.

Построение памяти микроконтроллеров семейства MCS-48

Микроконтроллеры семейства MCS-48 построены по Гарвардской архитектуре. Это означает, что память данных и память программ в этих микросхемах разделены и имеют отдельное адресное пространство. В этих микроконтроллерах имеется три адресных пространства: память программ, внешняя память данных и внутренняя память данных. Такое построение памяти позволяет реализовывать максимально надёжные системы.

Схема подключения внешних микросхем памяти к микроконтроллерам семейства MCS-48 показана на рисунке 7. Регистр адреса D3 на этой схеме предназначен для запоминания младших 8-ми бит адреса, передаваемых через шину данных/памяти. Старшие четыре бита адреса передаются через шину адреса, совмещенную с портом P2. Во время передачи адреса, микроконтроллер вырабатывает синхроимпульс на ножке ALE. Именно этот импульс позволяет запомнить младший байт адреса в регистре D3.

Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде.

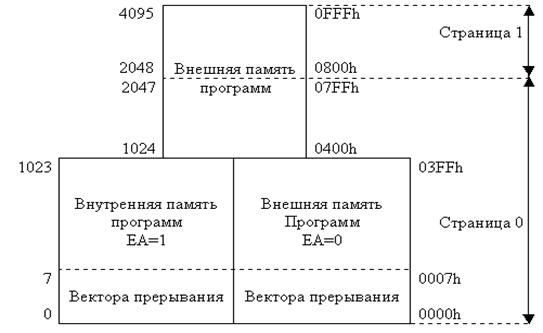

Память программ микроконтроллеров MCS-48

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом 4 Кбайта, причем для некоторых микросхем (например КР1816ВЕ48, КМ1816ВЕ49) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область младших адресов памяти программ. Учитывая, что выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, то при включении питания начнет выполняться программа, записанная во внутреннем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (например КР1816ВЕ35 или 8035) могут работать только с внешней микросхемой ПЗУ емкостью до 4 Кбайт. Микроконтроллеры семейства MCS-48 имеют внешний вывод EA, с помощью которого можно запретить работу внутренней памяти, для чего необходимо подать на вывод EA логический "0" (соединить этот вывод с корпусом). При этом внутренняя память программ отключается и, начиная с нулевого адреса, все обращения происходят к внешней памяти программ.

Рисунок 7. Схема подключения схем внешней памяти к микроконтроллерам семейства MCS-48

Доступ к внешней памяти программ осуществляется в двух случаях:

1. при действии сигнала EA=0 независимо от адреса обращения,

2. в любом случае, если программный счетчик (РС) содержит число большее, чем максимальная ячейка внутренней памяти программ.

Распределение памяти программ микроконтроллера КР1816ВЕ48 представлено ниже:

|

Рисунок 8. Адресное пространство памяти программ.

Для чтения таблиц элементарных функций, перекодировок или строк, выводимых на дисплей, из памяти программ используются команды

MOVP A, @A и MOVP3 A, @A

Переключение страниц памяти программ осуществляется командами

SEL MB1;Выбрать первую страницу

SEL MB0;Выбрать нулевую страницу

Для других микроконтроллеров этого семейства изменяется только объем внутренней памяти программ. При использовании портов P1 и P2 в качестве дополнительных адресных расширителей объём доступной внешней памяти программ может быть увеличен до 16 Мбайт.

Ниже приведены адреса векторов прерываний и соответствующие им аппаратурные источники прерываний программы:

| Вектор прерывания | Флаги, вызывающие прерывание | Источник прерывания |

| 0000Н | - | Рестарт (сброс) контроллера RESET |

| 0003Н | IE | внешнее прерывание INT |

| 0007Н | TF | Таймер |

Внешняя память данных микроконтроллеров MCS-48

Внешняя память данных предназначена для временного хранения информации, используемой в процессе выполнения программы. Эта память физически должна быть подключена к микросхеме микроконтроллера при помощи схемы, изображенной на рисунке 1. Максимальный объем этой памяти определяется регистрами R0 и R1 и составляет 256 байт. Точно также как и в случае внешней памяти программ, объем внешней памяти данных может быть увеличен за счет использования портов P1 и P2 до 16 Мбайт.

| Для обращения к внешней памяти данных используются команды: MOVX A, @R0 или MOVX A, @R1 (команды чтения) MOVX @R0, или MOVX @R1, A (команды записи) |

Рисунок 9. Адресное пространство внешней памяти данных.

Отметим, что в качестве внешней памяти данных могут быть использованы как микросхемы ОЗУ так и микросхемы ПЗУ.

Внутренняя память данных микроконтроллеров MCS-48

Внутренняя память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы. Адресное пространство внутренней памяти данных представляет собой 256 восьмиразрядных ячеек, с адресами от 000h до 0FFh. Для микроконтроллеров 8048, 8035, КР1816ВЕ35, КР1816ВЕ48 из них доступно только 64 ячейки памяти. Для микроконтроллеров 8049, КР1816ВЕ49 из них доступно 128 ячеек памяти. И только для микроконтроллеров 1850ВЕ49 доступны все 256 ячеек внутренней памяти данных. Распределение адресного пространства памяти данных микроконтроллеров серии MCS-48 приведено на рисунке 10.

Младшие 32 байта внутреннего ОЗУ данных объединены с 2 мя банками регистров (RB0 - RB1) и восьмиуровневым стеком микроконтроллера. Банк регистров состоит из восьми восьмиразрядных регистров с именами R0, R1, …, R7. Два банка регистров служат для организации независимой работы основной программы и подпрограмм обслуживания прерываний. Переключение банков регистров производится при помощи особого бита BS регистра слова состояния программы PSW командами SEL RB0 и SEL RB1.

Команды программы могут обращаться к регистрам, используя их имена R0-R7 (MOV A, R0 или MOV R7, A), или используя их адрес во внутренней памяти данных (доступна только косвенно-регистровая адресация). Например:

MOV R0, #5MOV A, @R0или

MOV R0, #7MOV @R0, A).

Рисунок 10. Адресное пространство внутренней памяти данных.

Следующие после второго банка регистров ячейки памяти образуют обычное ОЗУ.

Ячейки внутренней памяти данных с адресами 8 - 23 представляют из себя аппаратный 8 - ми уровневый стек, где сохраняются адреса возвратов из подпрограмм. В составе системы команд отсутствуют команды сохранения регистров в стеке. То есть разработчик программы вынужден следить за использованием регистров во вложенных подпрограммах. Это, наряду с малой глубиной аппаратного стека, сильно ограничивает возможности по написанию программ для микроконтроллеров семейства MCS-48.

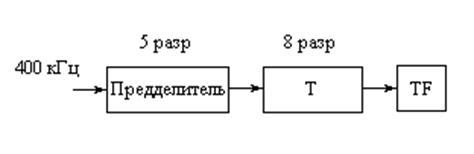

Устройство таймера микроконтроллера MCS-48

В микроконтроллерах семейства MCS-48 внутренний таймер может быть использован как в режиме таймера так и в режиме счетчика внешних событий.

Режим таймера

Таймер состоит из пятиразрядного предварительного делителя на 32 и восьмиразрядного суммирующего счётчика. На вход предделителя поступают сигналы основной синхронизации ALE с периодом 2,5 мкс (15 периодов задающего генератора тактовой частоты). Таким образом минимальный промежуток времени, задаваемый при помощи таймера равен 80 мкс. Путём предварительной записи информации в таймер можно регулировать время, задаваемое таймером от 80 мкс до 20,48 мс. Эти значения определяются тем, что в таймер T можно записать 256 различных чисел. Если требуется больший временной интервал, то его можно получить программным путём с использованием любой ячейки внутренней памяти. Схема таймера приведена на рисунке 11.

Рисунок 11. Схема таймера микроконтроллеров семейства MCS-48.

Когда содержимое счетчика изменяется из состояния все "1" в состояние все "0", то устанавливается (принимает значение "1") флаг прерывания таймера TF0 или TF1.

Обычно пользователя интересует не максимальный интервал времени, а свой конкретный интервал времени, меньший максимально возможного. Для уменьшения интервала времени в регистр таймера можно предварительно занести число и тем самым сформировать произвольный интервал времени. Рассмотрим пример подготовки таймера T для формирования временного интервала 5мс.

;Настроить таймер на генерацию 5-ти миллисекундного интервала времени-------------------------------------- mov A, #-62;Загрузить таймер числом 9Eh, равным числу -62 - количество периодов mov T, A;входной частоты таймера (62 периода таймера = 62*80 мкс = 4,96 мс) STRT T;Запустить таймер OjidanTimer: JTF SledKomanda;Подождать пока не переполнится таймер JMP OjidanTimerSledKomanda: STOP TCNT;Остановить таймерРежим счётчика

В режиме счетчика содержимое счетчика инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на вывод микроконтроллера T1. Так как на распознавание периода требуются три машинных цикла то, минимальное время между импульсами равно 7,5 мкс. Минимальная длительность единичного сигнала на входе T1 при частоте кварцевого резонатора 6 МГц равна 0,5 мкс. На длительность периода входных сигналов ограничений сверху нет.

Запуск счётчика осуществляется командой STRT CNT, а остановка STOP TCNT. Количество подсчитанных импульсов можно считать командой MOV A, T.

Система команд микроконтроллеров MCS-48

Система команд микроконтроллера предоставляет большие возможности обработки данных, обеспечивает реализацию логических, арифметических операций, а также управление в режиме реального времени.

Реализована побайтовая (8 бит) и потетрадная (4 бита) обработка данных. Микросхемы семейства MCS-48 - это 8-разрядные микропроцессоры, а это означает, что ПЗУ, ОЗУ, регистры специального назначения, АЛУ и внешние шины имеют байтовую организацию.

В машинном коде команда занимает один, или два байта в зависимости от типа команды. Команды выполняются за один или два машинных цикла. При этом большинство команд выполняются за один машинный цикл длительностью 2,5 мкс (при 6 МГц кварцевом резонаторе).

Запись команд в машинных кодах для человека неудобна, кроме того, разные машинные команды выполняют одинаковые действия только над разными ячейками памяти. Поэтому для записи команд микропроцессоров была придумана система мнемонических обозначений. Для записи команды микропроцессора сначала ставится мнемоническое обозначение, затем указывается ячейка памяти – приёмник результата выполнения операции и наконец источник данных для выполнения операции. Например, в команде

MOV A, R2символы MOV обозначают операцию копирования, второй операнд R2 определяет, что данные необходимо взять из регистра R2 текущего банка регистров, а первый операнд A определяет, что результат необходимо поместить в регистр – аккумулятор. При этом старое значение регистра – аккумулятора будет стёрто.

Мнемоническое обозначение команды отделяется от операндов одним или несколькими символами пробела или табуляции, а операнды отделяются друг от друга запятыми.

Если операция требует для выполнения двух источников и одного приёмника результата операции (например, команда сложения ADD или логического умножения ANL), то первый операнд является одновременно и источником и приёмником результата операции. Например, в команде

ADD A, R1символы ADD обозначают операцию сложения двух чисел, данные будут взяты из регистра R1 текущего банка регистров и аккумулятора а результат будет помещён в аккумулятор вместо старого значения этого регистра.

В таблице 2 приведены инструкции, влияющие на установку флагов.

Систему команд микроконтроллера условно можно разбить на пять групп:

· арифметические команды

· логические команды

· команды передачи данных

· команды ветвления программ и передачи управления

· команды управления режимами работы микроконтроллера

|

|

|

|

Дата добавления: 2013-12-13; Просмотров: 4586; Нарушение авторских прав?; Мы поможем в написании вашей работы!