КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Синхронные SR-защелки

|

|

|

|

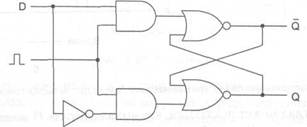

Часто бывает удобно сделать так, чтобы защелка меняла состояние только в определенные моменты. Чтобы достичь этой цели, мы немного изменили основную схему и получили синхронную SR-защелку (рис. 3.22).

|

| Q |

Тактовый п генератор

Рис. 3.22. Синхронная SR-защелка

Эта схема имеет дополнительный синхронизирующий вход, который обычно равен 0. Если этот вход равен 0, то оба выхода вентилей И равны 0 независимо от S и R, и защелка не меняет состояние. Когда значение синхронизирующего входа равно 1, действие вентилей И исчезает и состояние защелки становится зависимым от S и R. Для обозначения того факта, что синхронизирующий вход равен 1

Память

(то есть состояние схемы зависит от значений S и R), часто используется термин стробировать.

(то есть состояние схемы зависит от значений S и R), часто используется термин стробировать.

' До сих пор мы скрывали, что происходит, если S=R=1. И по понятным причинам: когда и R, и S в конце концов возвращаются к 0, схема становится недетерминированной. Единственное состоятельное положение при S=R=1 — это Q=Q=0, но как только оба входа возвращаются к 0, защелка должна перейти в одно из двух стабильных состояний. Если один из входов принимает значение 0 раньше, чем другой, оставшийся в состоянии 1 «побеждает», потому что когда один из входов равен 1, он управляет состоянием защелки. Если оба входа переходят к 0 одновременно (что маловероятно), защелка переходит в одно из своих состояний наугад.

Синхронные D-защелки

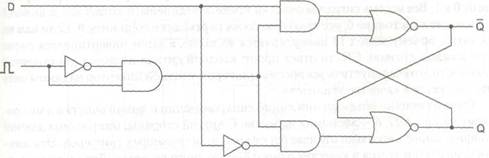

Чтобы разрешить неопределенность SR-защелки (неопределенность возникает в случае, если S=R=1), нужно предотвратить появление подобной неопределенности. На рис. 3.23 изображена схема защелки только с одним входом D. Так как входной сигнал в нижний вентиль И всегда является обратным кодом входного сигнала в верхний вентиль И, ситуация, когда оба входа равны 1, никогда не возникает. Когда D=l и синхронизирующий вход равен 1, защелка переходит в состояние Q=l. Когда D=0 и синхронизирующий вход равен 1, защелка переходит в состояние Q=0. Другими словами, когда синхронизирующий вход равен 1, текущее значение D отбирается и сохраняется в защелке. Такая схема, которая называется синхронной D-защелкой, представляет собой память объемом 1 бит. Значение, которое было сохранено, всегда доступно на выходе Q. Чтобы загрузить в память текущее значение D, нужно пустить положительный импульс по линии синхронизирующего сигнала.

|

|

|

Рис. 3.23. Синхронная D-защелка

Такая схема требует наличия 11 транзисторов. Более сложные схемы могут хранить 1 бит, имея всего 6 транзисторов. На практике обычно используются последние.

Триггеры (flip-flops)

Многие схемы выбирают значение на определенной линии в определенный момент времени и запоминают его. В такой схеме, которая называется триггером,

Глава 3. Цифровой логический уровень

переход состояния происходит не тогда, когда синхронизирующий сигнал равен 1, а во время перехода синхронизирующего сигнала с 0 на 1 (нарастающий фронт) или с 1 на 0 (задний фронт). Следовательно, длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро.

переход состояния происходит не тогда, когда синхронизирующий сигнал равен 1, а во время перехода синхронизирующего сигнала с 0 на 1 (нарастающий фронт) или с 1 на 0 (задний фронт). Следовательно, длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро.

Подчеркнем еще раз различие между триггером и защелкой. Триггер запускается фронтом сигнала, а защелка запускается уровнем сигнала. Обратите внимание, что в литературе эти термины часто путаются. Многие авторы используют термин «триггер», когда речь идет о защелке, и наоборот1.

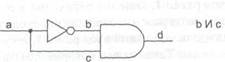

Существует несколько подходов к разработке триггеров. Например, если бы существовал способ генерирования очень короткого импульса на нарастающем фронте синхронизирующего сигнала, этот импульс можно было бы подавать в D-за-щелку. В действительности такой способ существует. Соответствующая схема показана на рис. 3.24, а.

|

|

|

|

| D | ||||

Время

Рис. 3.24. Генератор импульса (а); временная диаграмма для четырех точек на схеме (б)

На первый взгляд может показаться, что выход вентиля И всегда будет нулевым, поскольку функция И от любого сигнала с его инверсией дает 0, но на самом деле ситуация несколько более тонкая. При прохождении сигнала через инвертор происходит небольшая, но все-таки не нулевая задержка. Данная схема работает именно благодаря этой задержке. Предположим, что мы измеряем напряжение в четырех точках а, Ь, с и d. Входовый сигнал в точке а представляет собой длинный синхронизирующий импульс (см. нижний график на рис. 3.24, б). Сигнал в точке b показан над ним. Отметим, что этот сигнал инвертирован и подается с некоторой

В отечественной литературе термин «защелка» (latch) не используется, говорят о триггерах. Однако при этом вводится понятие Т-триггера, который здесь называется настоящим триггером. — Примеч. научн. ред.

В отечественной литературе термин «защелка» (latch) не используется, говорят о триггерах. Однако при этом вводится понятие Т-триггера, который здесь называется настоящим триггером. — Примеч. научн. ред.

Память

задержкой. Время задержки зависит от типа инвертора и обычно составляет несколько наносекунд.

задержкой. Время задержки зависит от типа инвертора и обычно составляет несколько наносекунд.

Сигнал в точке с тоже подается с задержкой, но эта задержка обусловлена только временем прохождения сигнала (со скоростью света). Если физическое расстояние между а и с, например, 20 микрон, тогда задержка на распространение сигнала составляет 0,0001 не, что, конечно, незначительно по сравнению со временем, которое требуется на прохождение сигнала через инвертор. Таким образом, сигнал в точке с практически идентичен сигналу в точке а.

Когда входные сигналы b и с подвергаются операции И, в результате получается короткий импульс, длина которого (Д) равна вентильной задержке инвертора (обычно 5 не и меньше). Выходной сигнал вентиля И — данный импульс, сдвинутый из-за задержки вентиля И (см. верхний график на рис. 3.24, б). Этот временной сдвиг означает только то, что D-защелка активизируется с определенной задержкой после нарастающего фронта синхронизирующего импульса. Он никак не влияет на длину импульса. В памяти со временем цикла в 50 не импульс в 5 не (который сообщает, когда нужно выбирать линию D) достаточно короткий, и в этом случае полная схема может быть такой, какая изображена на рис. 3.25. Следует упомянуть, что такая схема триггера проста для понимания, но на практике обычно используются более сложные триггеры.

|

|

|

Рис. 3.25. D-триггер

Стандартные изображения защелок и триггеров показаны на рис. 3.26. На рис. 3.26, а изображена защелка, состояние которой загружается тогда, когда синхронизирующий сигнал СК (от слова clock) равен 1, в противоположность защелке, изображенной на рис. 3.26, б, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0, чтобы загрузить состояние из D. На рис. 3.26, виг изображены триггеры. То, что это триггеры, а не защелки, показано с помощью уголка при синхронизирующем входе. Триггер на рис. 3.26, в изменяет состояние на возрастающем фронте синхронизирующего импульса (переход от 0 к 1), тогда как триггер на рис. 3.26, г изменяет состояние на заднем фронте (переход от 0 к 1). Многие (хотя не все) защелки и триггеры также имеют выход Q, а у некоторых есть два дополнительных входа: Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q=l, а второй (Reset ила Clear) - Q=0.

Глава 3. Цифровой логический уровень

|

|

|

|

б в

Рис. 3.26. D-защелки и D-триггеры

|

|

|

|

Дата добавления: 2013-12-13; Просмотров: 2967; Нарушение авторских прав?; Мы поможем в написании вашей работы!