КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Отметим, что операция сдвига выполняется процессорами компьютеров гораздо быстрее, чем общая операция умножения или деления

|

|

|

|

Внимательный анализ результатов обычного сдвига двоичного кода показывает, что сдвиг влево эквивалентен умножению на два, а сдвиг вправо эквивалентен целочисленному делению на два.

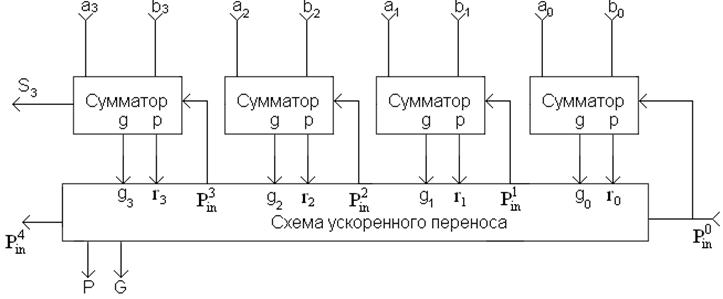

Такой способ наращивания разрядности сумматоров путем последовательного объединения нескольких полных сумматоров меньшей разрядности достаточно прост в схемной реализации, но при этом имеет существенный недостаток – низкое быстродействие. Распространение переноса в таких структурах осуществляется последовательно от микросхемы к микросхеме. Этого недостатка лишены сумматоры с параллельным переносом.

Чтобы уменьшить время операции сложения многоразрядных чисел, можно использовать схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных. Для сигнала переноса i-го разряда справедливо соотношение:

;

;

;

;

Величины gi, ri вычисляются в качестве промежуточных результатов и в полном сумматоре. Следовательно, их получение не требует дополнительных затрат. Сигнал gi вырабатывается тогда, когда в данном разряде перенос происходит из-за комбинации входных переменных ai, bi. Поэтому его называют функцией генерации переноса. Сигнал ri показывает, передается ли полученный в младшем разряде сигнал переноса  дальше. Поэтому он называется функцией распространения переноса.

дальше. Поэтому он называется функцией распространения переноса.

Таким образом, можно вывести следующие формулы для вычисления сигналов переноса:

Хотя полученные выражения достаточно сложные, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций определяется только временем задержки распространения сигнала на двух элементах. Эти функции реализуются специальным комбинационным устройством — схемой ускоренного переноса.

|

|

|

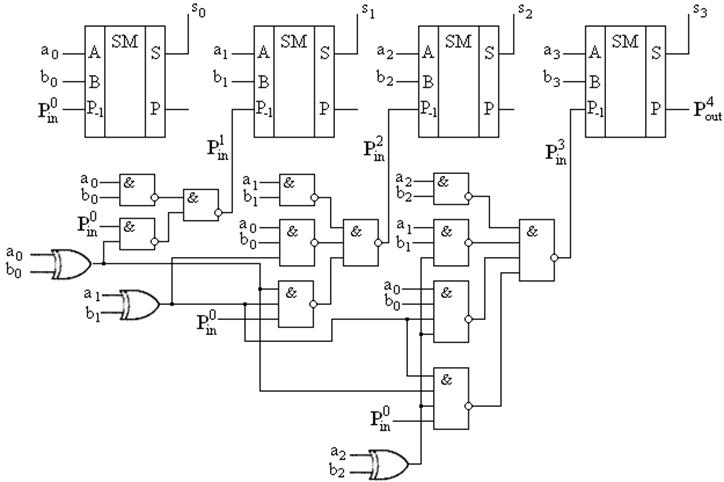

Схема сумматора с параллельным переносом приведена на рисунке. На другом рисунке изображена схема устройства параллельного переноса в группе из четырех разрядов. Эта схема реализует полученную ранее систему уравнений.

Рис. Схема сумматора с параллельным переносом.

Рис. 4.9. Схема четырехразрядного сумматора с параллельным переносом.

Комбинационная схема сдвига

Как известно, умножения в двоичной системе счисления сводится к сложению и сдвигу кода, деление также реализовано через сложение и сдвиг кода. Различают несколько разновидностей сдвига: влево, вправо, циклический сдвиг влево и циклический сдвиг вправо. Сдвиг кода влево означает, что каждый его бит перемещается на соседнюю слева позицию, при этом освободившийся младший (самый правый) разряд поля заполняется нулем, а самый левый бит кода теряется. Про такой бит говорят, что он выталкивается за разрядную сетку. Сдвиг вправо осуществляется в противоположном направлении: каждый бит кода занимает соседний справа разряд, при этом освободившийся старший (самый левый) разряд поля заполняется нулем, а младший бит кода выталкивается за разрядную сетку, теряется. Существуют еще и циклические сдвиги кода, в которых выталкиваемый бит кода не теряется, а записывается в освободившийся слева или справа разряд поля.

00101101 00101101

01011010 00010110

а) б)

Рис. Сдвиг кода влево (а), сдвиг кода вправо (б).

В более общих схемах оба варианта сдвига объединяются в одну схему с единым управляющим битом, поступающим в две управляющие линии, причем в одну из них через вентиль «НЕ». Таким образом, значение С=1 запускает сдвиг в одну сторону, а значение С=0 обеспечивает сдвиг в другую сторону. В такой схеме сдвига используется 2n вентилей «И», где n — количество сдвигаемых разрядов, и один вентиль «НЕ». Следовательно, для ее реализации требуется 6n+1 транзисторов.

|

|

|

Рассмотрим схему сдвига, которая имеет восемь входов и восемь выходов (рис. 3.15). Восемь входных битов подаются на линии D0,…,D7. Выходные данные, которые представляют собой входные данные, сдвинутые на 1 бит, поступают на линии S0,…,S7. Линия управления С определяет направление сдвига: 0 – влево, 1 – вправо.

Рис. 3.15. Схема сдвига.

Если С=1, правый член каждой пары включается, пропуская через себя соответствующий бит. Так как правый вентиль И соединён с входом вентиля ИЛИ, который расположен справа от этого вентиля И, происходит сдвиг вправо. Если С=0, включается левый вентиль И из пары, и тогда происходит сдвиг влево.

|

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 1413; Нарушение авторских прав?; Мы поможем в написании вашей работы!