КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

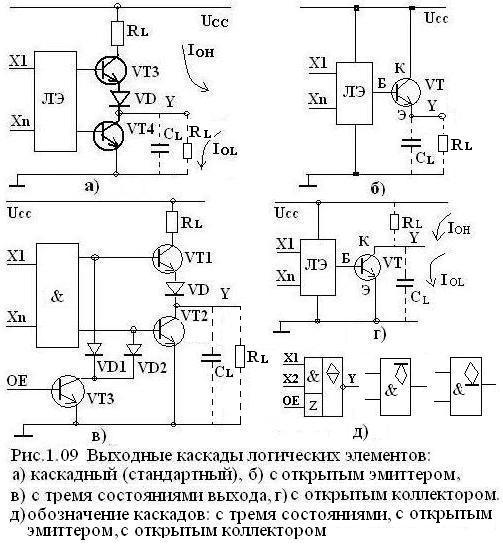

Выходные каскады логических элементов

Разные шины выходных каскадов обладают различными характеристиками, достоинствами и недостатками.

Рассмотрим 4 основных типа выходных каскадов, приведенных на Рис. 1.09.

а). Стандартный или как его еще называют каскадный выход, используемый в логических элементах, например, в элементе И-НЕ.

Работа каскада рассмотрена в §1.1. рис.1.1.а). Его основной недостаток – невозможно параллельное объединение выходов нескольких элемнтов.

б). Выход элемента с открытым эмиттером.

В этом случае в выходном транзисторе элемента эмиттер выведен на вывод микросхемы, с которому пользователь может подключать нагрузку самостоятельно.

Нагрузка определяется из соотношения:

где Imax – допустимый ток через транзистор VT.

в). Выход элемента с тремя состояниями.

Выход логического элемента на транзисторах VT1, VT2, VT3 и диодах VD1 и VD2 имеет управляющий вход ОЕ.

При ОЕ=0 элемент имеет стандартный выход, поскольку при этом VT3 закрыт, следовательно и диоды VD1 и VD2 закрыты и не влияют на входы VT1 и VT2, которые в этом случае управляются самим логическим элементом.

При ОЕ=1, VT3, VD1 и VD2 открываются и на базы VT1 и VT2 подается низкий уровень, что приводит к их закрытому состоянию.

На выходе У появляется высокий импенданс, третье состояние, называемое Z-состоянием. Широко применяются в цифровой технике, имеющей общую шину, к которой подключаются многие узлы, имеющие выход с тремя состояниями, позволяющий отключать узел от шины, тем самым освобождая ее для использования другими узлами.

г). Выход элемента с открытым коллектором.

В таком элементе на выходе ставится аналогично элементу с открытым эмиттером дополнительный транзистор VT, у которого база подключена к выходу логического элемента, эмиттер – к земле, а коллектор выведен на вывод микросхемы, к которому пользователь может подключать нагрузку из расчета:

где Imax – максимально допустимый ток через транзистор VT;

CL – рассматриваемая в ранее приведенных схемах, состоит из входной емкости нагрузки плюс монтажная емкость.

Достоинство элементов с открытыми эмиттером или коллектором в том, что они позволяют выходы нескольких элементов объединять на общую нагрузку, что позволяет получать дополнительные логические функции.

д). На Рис. 1.9.д) приведены условные обозначения каскадов, изображенных на рисунках б), в) и г).

Пример использования логического элемента для реализации функций МОНТАЖНОГО ИЛИ и МОНТАЖНОГО И в схеме, приведенной на Рис. 1.10. Уровень напряжения на выходе У (сх. на рисунке а) будет «0», когда открыт один или все выходные транзисторы VT, объединенные по выходу. Реализуется функция И-ИЛИ-НЕ. Такую функцию принято называть МОНТАЖНОЕ ИЛИ.

С другой стороны: на выходе У будет «1» тогда и только тогда, когда каждый элемент установит на выходе транзистора VT «1». Если же хотя бы один элемент установит на выходе VT «0», то на выходе У также будет «0». Это обстоятельство позволяет рассматривать схему, реализующую И: «1» - при всех единицах, «0» - при «0» на любом из них. Поэтому такую схему еще называют МОНТАЖНОЕ И.

В схеме максимальное число объединяемых элементов и максимальное значение RL ограничивается соотношением между значениям RL и суммой утечки закрытых транзисторов VT.

Когда все VT закрыты, падение напряжения на RL при протекании суммы токов утечки не должно снижать высокий уровень на выходе У ниже допустимого (для ТТЛ – 2.4л.).

Минимальное значение RL ограничивается максимально допустимым током через открытый транзистор VT.

Условное обозначение МОНТАЖНОГО ИЛИ на схемах показано на Рис. 1.10.б). УГО монтажных И и ИЛИ на Рис. 1.10 в) и г).

|

|

Дата добавления: 2014-01-05; Просмотров: 1792; Нарушение авторских прав?; Мы поможем в написании вашей работы!