КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Режима работы DMA

|

|

|

|

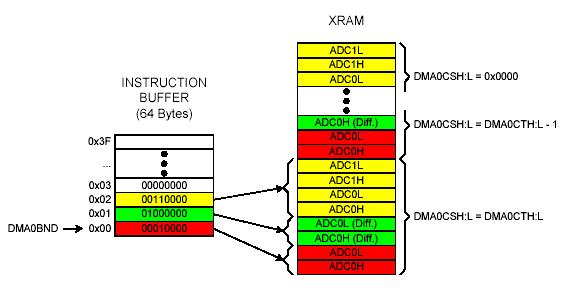

1. Режим 0

Регистр статуса DMA0ISW, ожидает адрес, содержащийся в регистре границы инструкции DMA0BND. Когда текущая инструкция DMA станет End of Operation instruction, Instruction Status Register сбросится в Instruction Boundary Register.

Схема 28. Режим 0 работы DMA

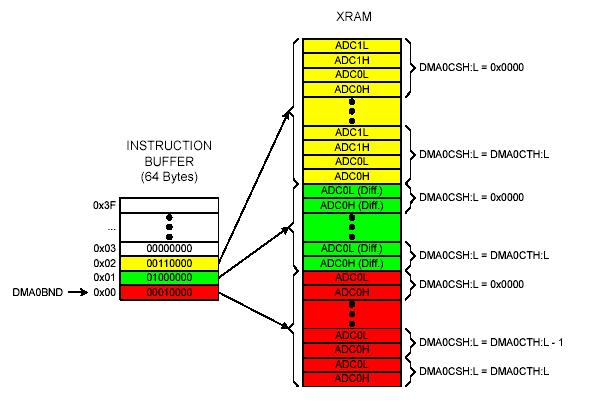

2. Режим 1

Регистр статуса DMA0ISW, ожидает адрес, содержащийся вне регистра границы инструкции DMA0BND. В конце выполнения инструкции Repeat Counter декрементируется, инструкция будет повторяться до тех пор, пока Repeat Counter не станет 0x0000. Затем значение Repeat Counter сбрасывается до Repeat Counter Limit. DMA инкрементирует DMA0ISW для следующего адреса инструкции.

Схема 29. Режим 1 работы DMA

2 регистра управления DMA

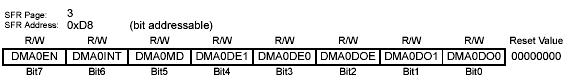

DMA0CN:

Бит DMA0EN: разрешает DMA

Бит DMA0INT: 0 – операции выполняются, 1 – выполнение операций завершилось

Бит DMA0MD: режим работы DMA

Бит DMA0DE1: флаг ошибки переполнения

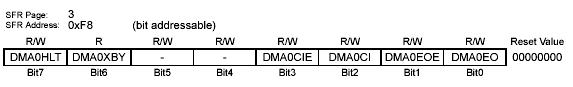

DMA0CF:

Бит DMA0HLT: 0 – DMA завершил доступ к XRAM, 1 – DMA работает с XRAM

[1] CISC (Complex Instruction Set Computing) – традиционная архитектура процессоров с широким набором различных машинных команд переменной длины и разным временем их исполнения

RISC (Reduced Instruction Set Computing) – архитектура процессоров, построенная на основе сокращённого набора команд. Характеризуется наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр (все, кроме команд чтения и записи в память), а также отсутствием косвенной адресации

[2]Гарвардская архитектура – архитектура компьютера, разработанная с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. В Гарвардской архитектуре память данных отдельна от памяти программ

[3] MAC (Mandatory access control) – разграничение доступа субъектов к объектам, основанное на назначении метки конфиденциальности для информации, содержащейся в объектах, и выдаче официальных разрешений (допуска) субъектам на обращение к информации такого уровня конфиденциальности

[4] Конец операции, конец операции с продолжением преобразования, восстановление

|

|

|

|

|

Дата добавления: 2014-01-05; Просмотров: 368; Нарушение авторских прав?; Мы поможем в написании вашей работы!