КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Счетчик с параллельным переносом

|

|

|

|

Для повышения быстродействия счетчиков применяют различные способы ускорения переноса, как это делают и в сумматорах для сокращения времени сложения чисел.

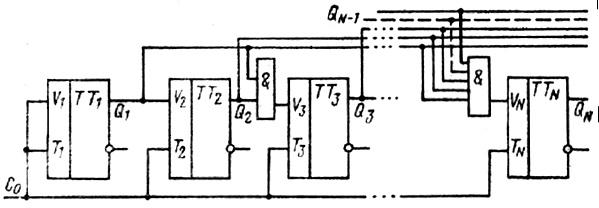

Один из широко применяемых способов ускорения переноса в счетчиках основан на введении логических элементов, с помощью которых достигается возможность одновременного (параллельного) формирования сигналов переноса для всех разрядов. Для реализации этого способа применяют ТV-триггеры. На Т-входы всех триггеров одновременно подаются счетные импульсы, а на V-вход каждого триггера поступает сигнал переноса, формируемый логической схемой в виде уровня 1. Триггеры, на V-входе которых имеется сигнал переноса, одновременно опрокидываются с приходом очередного счетного импульса, и таким образом устанавливается новое состояние счетчика. Для определения вида цепи переноса в счетчике обратимся к уже рассмотренной табл. 2.4. Из нее следует, что первый разряд, как и в счетчике с последовательным переносом, должен быть построен на Т-триггере. Если применяется ТV-триггер, то на его V-вход следует подать 1 или соединить его с Т-входом.

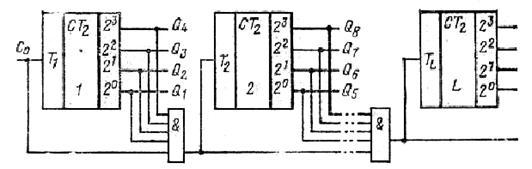

Второй триггер опрокидывается счетным импульсом при наличии 1 на выходе первого триггера, а третий триггер опрокидывается при наличии 1 на выходах двух предыдущих триггеров. Обобщая эту закономерность на случай N-разрядного счетчика, получим, что каждый последующий триггер должен опрокинуться под воздействием счетного импульса при наличии 1 на выходах всех предыдущих триггеров. Следовательно, для формирования сигнала переносов каждый разряд счетчика необходимо включить элемент И и соединить его входы с прямыми выходами всех предыдущих разрядов, а выход с V-входом триггера данного разряда. Пример суммирующего счетчика с параллельным переносом на ТV-триггерах приведен на рис. 2.12. Быстродействие этого счетчика выше, чем счетчика с последовательным переносом, поскольку оно равно быстродействию одного разряда.

Рис. 2.12. Счетчик с параллельным переносом

Это является важным достоинством счетчиков с параллельным переносом, обеспечившим им широкое применение. Недостаток необходимости включения в схему логических элементов с разным, причем нарастающим от разряда к разряду, числом входов. Это нарушает регулярность структуры счетчика и ограничивает возможность наращивания его схемы. Частично этот недостаток можно устранить при использовании триггеров с входной логикой.

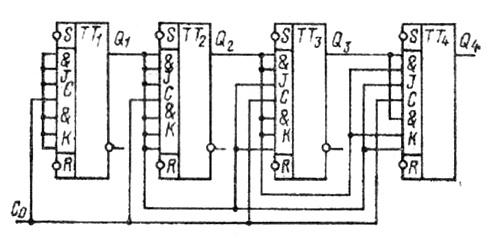

Многие серии микросхем содержат JК-триггеры с входной логикой. Для преобразования JК-триггера в ТV-триггер необходимо объединить входы J и К в один, это и будет V-вход. У триггера с тремя конъюнктивно связанными J-входами и тремя конъюнктивно связанными К-входами могут быть образованы, следовательно, три конъюнктивно связанных V-входа. При реализации счетчика на таких триггерах исключаются дополнительные логические элементы в цепях переноса. Однако ограничение в разрядности счетчика остается. Поскольку имеющиеся интегральные JК-триггеры позволяют получить до трех V-входов, на них может быть построен лишь четырехразрядный счетчик с параллельным переносом (рис. 2.13).

Рис. 2.13. Счетчик на JK-триггерах с входной логикой

Вычитающий счетчик с параллельным переносом строится так же, как и суммирующий, но сигналы переноса снимаются с инверсных, относительно используемых в суммирующем счетчике, выходов триггеров.

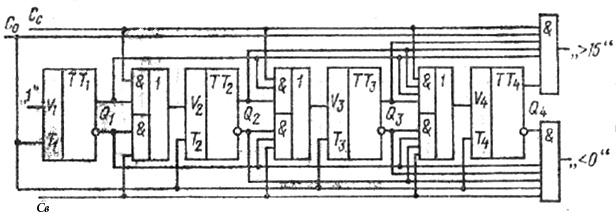

Реверсивный счетчик, объединяющий возможности суммирующего и вычитающего, строится таким образом, чтобы обеспечивалось управление направлением счета с помощью сигналов на сложение Сс и вычитание Св. Поэтому его схема содержит дополнительную комбинационную часть, выполняющую указанную функцию.

Многие счетчики с параллельным переносом, выпускаемые в виде микросхем, имеют помимо основных выходов – дополнительные (рис. 2.14). На одном из выходов, обозначенном «> 15», сигнал 1 появляется при заполнении счетчика единицами, т. е. когда он перешел в состояние с номером 15. Следовательно, на этом выходе формируется сигнал переноса в следующий счетчик. На другом выходе, обозначенном «<0», сигнал появляется при заполнении счетчика нулями и является сигналом займа в следующий счетчик в режиме вычитания.

Рис. 2.14. Реверсивный счетчик на TV-триггерах

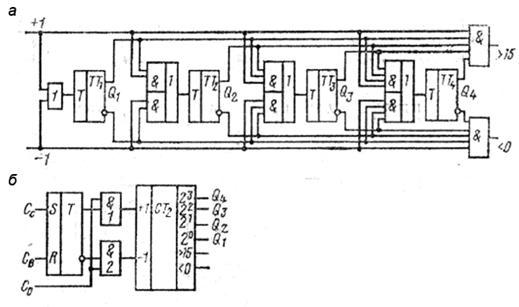

Реверсивный счетчик можно построить и на Т-триггерах (рис. 2.15, а). Как и в рассмотренном ранее суммирующем счетчике, счетные импульсы поступают на Т вход триггера через логические элементы только в том случае, если они открыты единичными сигналами с выходов предыдущих разрядов.

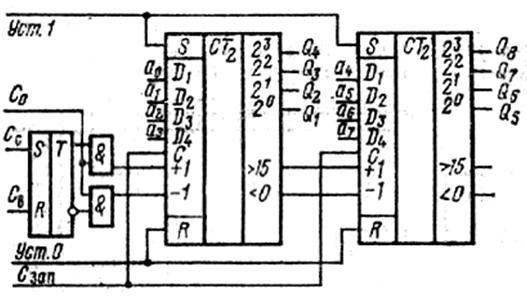

В счетчике на рис. 2.15, а для счетных импульсов предусмотрены два входа. Если счетчик должен работать в режиме прямого счета, импульсы следует подавать на вход «+1», в режиме обратного счета – на вход «-1». При использовании такого счетчика в качестве реверсивного с одним источником импульсов необходимо предусмотреть внешнее устройство коммутации счетных импульсов на суммирующий «+1» либо на вычитающий «-1» входы. Вариант такой коммутирующей приставки к счетчику приведен на рис. 2.15, б. При подаче положительного импульса на S-вход RS-триггера на его прямом выходе установится единичный уровень, который откроет элемент 1 для счетных импульсов С0. Счетчик будет работать в режиме сложения. Если подать положительный импульс на R-вход триггера, откроется для счетных импульсов элемент 2 и счетчик будет работать в режиме вычитания.

Комбинированный, т. е. параллельно-последовательный перенос применяется при построении многоразрядных счетчиков, которые должны иметь высокое быстродействие. Функциональная схема таких счетчиков состоит из группы триггеров, внутри каждой из которых организуется параллельный перенос, а между группами – последовательный. В примере на рис. 2.15 счетчик состоит из четырехразрядных счетчиков с параллельным переносом. На выходе каждой группы триггеров включен элемент И, который формирует сигнал переноса в следующую группу при заполнении триггеров единицами.

Рис. 2.15. Реверсивный счетчик на Т-триггерах: а – функциональная схема; б – схема управляющая напряжением счета

Рис. 2.16. Многоразрядный счетчик с комбинированным переносом

Интегральные четырехразрядные счетчики с выходами переноса и займа объединяются с использованием этих выходов. Например, при объединении суммирующих счетчиков необходимо соединить выход «>15» одного со счетным входом другого. При объединении реверсивных счетчиков, имеющих выходы сигналов переноса «> 15» и займа «<О», необходимо эти выходы соединить соответственно с суммирующим и вычитающим входами следующего счетчика. Пример восьмиразрядного реверсивного счетчика приведен на рис. 2.17. Возможности указанной микросхемы допускают установку заданного исходного состояния счетчика путем записи в него по D-входам (D1÷D4) нужной кодовой комбинации (а0... а7) при наличии разрешающего сигнала на входе Сз а п. Кроме того, по шинам «Уст. О» и «Уст. 1» счетчик можно заполнить нулями или единицами.

Рис. 2.17. Восьмиразрядный реверсивный счетчик

Результат счета снимается с выходов Q1 ÷ Q8. Счетчик можно использовать для деления числа (частоты повторения) импульсов на 16, если использовать выход «> 15» первой микросхемы, и на 256, если использовать аналогичный выход второй микросхемы.

|

|

|

|

|

Дата добавления: 2014-01-06; Просмотров: 15135; Нарушение авторских прав?; Мы поможем в написании вашей работы!