КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

КЕШ- пам'ять

|

|

|

|

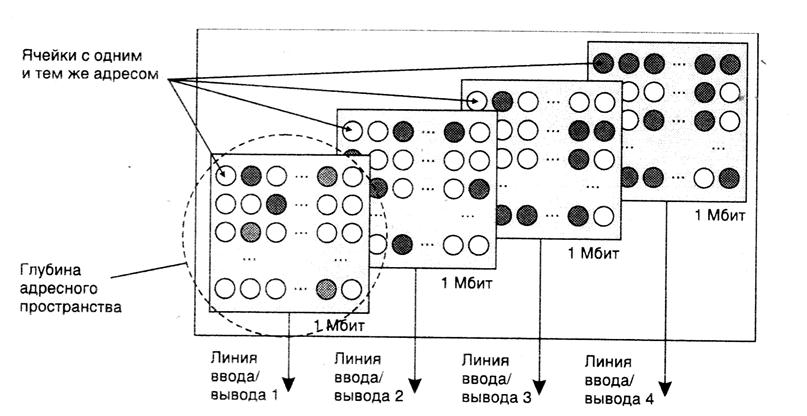

Рис8.6

Рис8.5

РА – регістр адреси

Р х, Р у – регістри адресів (координати х та у відповідно)

Д x, Д y – дешифратори адресів (стовпців і строк відповідно)

РД – регістр даних (запис і читання)

РУ – регістр управління, який виробляє сигнали для взаємодії всіх пристроїв

На Рис8.5 показана структура однорозрядної комірки пам’яті, що має одну лінію введення-виведення. Для того, щоб одержати багаторозрядну систему, треба застосувати n таких структур, як це показано на Рис8.6 для n =4.

Таким чином, загальна ємність мікросхеми пам’яті дорівнює добутку глибини адресного простору на кількість матриць, або ліній введення-виведення. В нашому прикладі:

1 Мбайт * 4 = 4 Мбайта

Оперативна пам’ять енергозалежна, вона може працювати тільки при наявності напруги живлення. При вимиканні напруги інформація зникає. Але зате вона швидкодіюча. Швидкість звертання до неї (время доступа) в сотні тисяч раз менша ніж до пам'яті на магнітних дисках (6-7 нсек і 7-20 мсек відповідно)

Оперативна пам'ять буває двох типів в залежності від її фізичної реалізації: статична (SRAM) і динамічна (DRAM). Статична будується на тригерах, а динамічна використовує принцип зберігання електричного заряду на конденсаторах.

В динамических ЗУ (DRAM) данные хранятся в виде зарядов емкостей

МОП-структур и основой ЗЭ является просто конденсатор небольшой емкости.

Такой ЗЭ значительно проще триггерного, содержащего 6 транзисторов,

что позволяет разместить на кристалле намного больше ЗЭ (в 4...5 раз)

и обеспечивает динамическим ЗУ максимальную емкость. В то же время

конденсатор неизбежно теряет со временем свой заряд, и хранение данных

|

|

|

требует их периодической регенерации (через несколько миллисекунд).

На Рис.8.7 дана спрощена схема однієї комірки DRAM.

Рис. 8.7 ЛЗС – линия записи- считывания, ЛВ – линия выборки

Коли транзистор ввімкнутий, на конденсатор С подається сигнал U запису або стирання одного біту інформації. Це певний рівень напруги (наприклад, 1 вольт – „1”, 0 вольт – „0”). При вимиканні транзистора ідеальний конденсатор міг би зберігати цей сигнал необмежений час. Але реальний конденсатор завжди має опір витіку (сопротивление утечки) R і поступово втрачає свій заряд. Тому інформацію в пам’яті типу DRAM необхідно періодично регенерувати (приблизно кожні 2 мсек). Це знижує швидкодію такої пам'яті.

Незважаючи на це саме пам'ять DRAM є найбільш розповсюдженою оперативною пам’яттю, бо вона набагато дешевше ніж SRAM.

Основні характеристики пам'яті:

- ємність

- швидкодія

- розрядність

- пропускна спроможність, або швидкість передачі даних

-та інші: частота шини, структурна організація, конструктивні відмінності, ціна, умови експлуатації.

Ємність оперативної пам'яті вимірюється в мегабайтах. Для комп’ютерів широкого призначення він сягає 256 Мбайт– 4 Гбайт і більше.

Швидкодія ОП вимірюється в наносекундах (1нс = 10-9 сек). Вона складається з часу позиціонування адреси за координатами х та у (час доступу) і часу вибору даних. Ці терміни приблизно однакові і для сучасних ОП складають 4-10 нсек.

Треба зауважити, що швидкодія оперативної пам'яті зазвичай набагато нижче ніж швидкодія процесора, внутрішня пам'ять якого побудована на тригерних регістрах. Тому розробники пам'яті застосовують різні структурні рішення (паралелізм вибірки, сторінкова організація тощо) для підвищення швидкодії.

Велике значення для продуктивності тандему процесор-пам'ять має пропускна спроможність шин обміну даними між процесором і пам’яттю. Вона залежить від фізичної частоти передачі даних по шинах, а також розрядності шин – 8, 16, 32, 64...

|

|

|

В поточний час (2008 – 2010 р.) найбільш розповсюдженою пам’яттю динамічного типу є SDRAM (синхронна DRAM) та RDRAM (RAMBUS DRAM). SDRAM має час доступу 6-9 нсек, частоту шини даних 66, 133, 150 Мгц, пропускну спроможність 256-1000 Мбайт/с. RDRAM має час доступу 4 нсек, частоту шини до 800 мгц, пропускну спроможність до 6 Гбайт/с. Але велику вартість – біля 1000 доларів за 128 Мбайт.

Всі параметри оперативної пам'яті з часом дуже швидко змінюються в кращу сторону, в тому числі і вартість. Сьогодні прийнятна ринкова ціна становить десь 15-20 доларів за 64 Мбайта, 30 за 128 Мбайт.

В пам’яті комп’ютерів з різних причин, наприклад, через сплески напруги джерел живлення, можуть бути збої інформації. Вважається, що в надійних система в інформаційних кодах можуть бути зіпсовані тільки поодинокі розряди. В такому випадку є можливість боротьби з помилками (виявляти чи, навіть, виправляти) за рахунок використання в кожній комірці пам’яті спеціалізованих додаткових розрядів – кодів Хеммінга. Найбільш часто використовується один додатковий розряд – розряд парності, який фіксує парність одиниць в інформаційному слові і таким чином виявляє поодинокі помилки. Збільшуючи число контрольних розрядів можна не тільки виявити, але і виправляти поодинокі помилки. Для цього розроблена спеціальна теорія і алгоритми.

Конструктивно оперативна пам’ять виконана у вигляді невеликих друкованих плат з декількома мікросхемами пам’яті на платі. В старих моделях (5 років тому) такі модулі були двох типів. SIMM (Single Inline Memory Module) – з одностороннім розташуванням виводів, та DIMM (Dual Inline Memory Module) – з двохстороннім розташуванням виводів. Модулі SIMM мають об’єм пам’яті до 128 Мбайт, 72 контакти і швидкість передачі даних за один цикл 32 біта. Модулі DIMM мають об’єм пам’яті до 256 Мбайт, 168 контактів і швидкість передачі даних – 64 біт за цикл. В багатьох комп’ютерах передбачено встановлення до чотирьох модулів пам’яті, тобто загальних об’єм може сягати 0,5 – 1 Гбайт.

Сучасні персональні комп’ютери комплектуються різноманітними видами оперативної пам’яті, але на даний час дуже широко використовується тільки три види оперативної пам’яті: DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM, а наступні вже застарілі: SIMM, SDRAM (DIMM), RD RAM,

Сучасні персональні комп’ютери комплектуються різноманітними видами оперативної пам’яті, але на даний час дуже широко використовується тільки три види оперативної пам’яті: DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM, а наступні вже застарілі: SIMM, SDRAM (DIMM), RD RAM,

|

|

|

Процесори завжди працювали швидше ніж пам'ять. Удосконалення процесорів іде в основному шляхом підвищення їх швидкодії, в той час, коли удосконалення пам’яті зазвичай направлено перш за все на збільшення її об’єму. На практиці така невідповідність в швидкості приводить до того, що при безпосередній взаємодії швидкого процесора з повільною пам’яттю, процесор при кожному звертанні до пам’яті простоює, в результаті чого знижується загальна ефективність комп’ютера.

Кэш-память запоминает копии информации, передаваемой между устройствами

(прежде всего между процессором и основной памятью). Она имеет

небольшую емкость в сравнении с основной памятью и более высокое быстродействие (реализуется на триггерных элементах памяти).

При чтении данных сначала выполняется обращение к кэш-памяти (рис. 4.8). Если в кэше имеется копия данных адресованной ячейки основной

памяти, то кэш вырабатывает сигнал Hit (попадание) и выдает данные

на общую шину данных. В противном случае сигнал Hit не вырабатывается

и выполняется чтение из основной памяти и одновременное помещение

считанных данных в кэш.

Эффективность кэширования обуславливается тем, что большинство прикладных программ имеют циклический характер и многократно используют

одни и те же данные. Поэтому после первого использования данных из относительно медленной основной памяти повторные обращения требуют

меньше времени. К тому же при использовании процессором кэш-памяти

основная память освобождается, и могут выполняться регенерация данных в

динамическом ЗУ или использование памяти другими устройствами.

Объем кэш-памяти много меньше емкости основной памяти и любая единица информации, помещаемая в кэш, должна сопровождаться дополнительными данными (тегом), определяющими, копией содержания какой

ячейки основной памяти является эта единица информации.

В ассоциативной кэш-памяти, структура которой показана на рис. 4.9, каждая ячейка хранит данные, а в поле "тег" — полный физический адрес информации, копия которой записана. При любых обменах физический адрес запрашиваемой информации сравнивается с полями "тег" всех ячеек и при совпадении их в

|

|

|

любой ячейке устанавливается сигнал Hit.

При чтении и значении сигнала Hit = 1 данные выдаются на шину данных,

если же совпадений нет (Hit = 0), то при чтении из основной памяти данные

вместе с адресом помещаются в свободную или наиболее давно не спользуемую

ячейку кэш-памяти.

Для уникнення цього недоліку використовується проміжна високошвидкісна пам'ять, як буфер між процесором і оперативною пам’яттю. Ця пам'ять відносно невеликого об’єму називається кеш-пам’яттю (cache). Вона побудована на тригерах (SRAM) і має час доступу не більш 2 нсек. Об’єм кеш-пам'яті порівняно невеликий – в межах 512 КВ, але в останніх моделях – 1ГВ і більше.

Ідея кеш-пам’яті проста: в цю пам’ять заздалегідь записуються дані, які будуть використані в поточному циклі роботи процесора. Якщо цих даних достатньо, то можна досягти синхронної роботи процесора і пам’яті. Ефективність кеш-пам’яті відображається коефіцієнтом збігу, чи успішності, який дорівнює відношенню вдалих звернень до кеш-пам’яті до загального числа звернень до пам’яті.

В перших спробах використання кеш-пам’яті в ній збереглися як дані, так і програми. Але в поточному часі існує тенденція використання розподіленої кеш-пам’яті, коли для даних і команд існують різні кеш-пам’яті. Розподілена кеш-пам’ять дозволяє здійснювати паралельний доступ до команд і операндів, що необхідно при організації конвеєрних архітектур в процесорах.

Щоб мінімізувати час доступу до інформації, в сучасних персональних комп’ютерах передбачено декілька рівнів кеш-пам’яті: перший(L1), другий (L2) та іноді третій (L3). Кеш L1 розташована прямо в корпусі процесора, кеш L2 і L3 розташована на системній платі поблизу від процесора.

Треба зауважити, що кеш-пам’ять використовується не обов’язково тільки при обслуговування процесора. Вона часто використовується також при обміні даними з другими швидкодіючими пристроями, наприклад, з вінчестерами.

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 1212; Нарушение авторских прав?; Мы поможем в написании вашей работы!