КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

RAM-память

|

|

|

|

Аббревиатурой RAM обозначаются оперативные запоминающие устройства на базе полупроводниковых технологий. Они имеют определенное количество ячеек памяти. Каждая ячейка памяти имеет установленный объем памяти. Она может принимать информацию определенной длины. Каждая ячейка памяти имеет индивидуальный адрес. По этим адресам осуществляется доступ к ячейкам памяти. То есть RAM является памятью с произвольной выборкой.

Обозначение RAM является сокращением от Random Access Memory, англ. — память с произвольной выборкой.

Ячейки памяти выбираются по своим адресам. В ячейках хранится записанная информация. Для вывода данных ячейки также выбираются по своему адресу. Считывание данных не стирает содержание ячейки. Если информация больше не нужна, она может быть удалена, а в ячейку памяти записана новая информация.

ОЗУ выпускаются исключительно в виде интегральных микросхем. Различают статические RAM и динамические ОЗУ. В статическом ОЗУ ячейки состоят из триггеров. Каждый бит записывается в один из триггеров. В динамическом ОЗУ для хранения информации используются внутренние емкости. Каждый бит записывается в маленький конденсатор. Так как имеют место токи утечки, то возникает потеря заряда, поэтому емкости периодически надо подвергать процессу регенерации (восстановление исходных уровней сигнала).

Статические и динамические ОЗУ являются энергозависимыми. При отключении питания информация теряется.

В целях сохранения информации ставят автономные батареи. Энергонезависимые RAM находятся в стадии разработки. Их ждет большое будущее.

Статические ОЗУ или RAM производятся на базе различных технологий. Схемы принадлежат к различным семействам. Существует ОЗУ в ТТЛ-исполнении, в ЭСЛ-, в TV-МОП- и в А-МОП-исполнении. Динамические ОЗУ строятся на различных МОП-элементах.

12.3.1. Статические ОЗУ (SRAM)

12.3.1.1. Элемент памяти RAM в ТТЛ-исполнении

Статические ОЗУ могут быть построены на биполярных транзисторах. Используется известная ТТЛ-технология (см. гл. 6 «Семейства схем»). Основой ячейки является триггер на двух мультиэмиттерных транзисторах согласно рис. 12.17. Триггер управляется Х-адресной шиной, 7-адресной шиной и двумя разрядными линиями записи—считывания. Такой элемент памяти может запомнить 1 бит. Элемент содержит значение 1, если Тх открыт, а Т2 заперт. И значение 0, если Т2 открыт, а Тх заперт.

Активация ячейки памяти

Если на обоих адресных шинах X и Г действует 0-сигнал (О В, заземление), то ячейка памяти не активирована. Ток эмиттера открытого транзистора течет на землю. По разрядным линиям SLV SL2 ток не протекает.

|

Если только на одной адресной шине действует 1-сигнал, то элемент памяти остается неактивным, так как эмиттерный ток открытого транзис-

тора может протекать через другую адресную шину. Только когда по обеим адресным шинам проходит 1-сигнал, то есть +5 В, элемент памяти активируется, и эмиттерный ток открытых транзисторов течет по соответствующим линиям записи—чтения.

Чтение

После активации элемента памяти по iSX-линиям течет ток открытого транзистора. На рис. 12.17 транзистор Т2 открыт. Ток эмиттера протекает через

SL2 и на выходе Q через усилитель выдает 1-сигнал. Элемент памяти сохранил значение 0. Если после активации ток протекает по линии SLV то элемент памяти сохранил значение 1.

Запись

Для записи 1 в элемент, содержащий 0, необходимо подать 1-сигнал или +5 В на SL2 и 0-сигнал, или 0 В на SLV При хранении 0 проводит транзистор Т2. Он запирается после подачи на его третий эмиттер, подключенный к SLV +5 В. Транзистор Тх открывается, и его эмиттерный ток может течь через SLV После завершения активации элемент памяти сохраняет это состояние.

Для записи 0 в элемент, содержащий 1, необходимо подать 1-сигнал или +5 В на SLl и 0-сигнал, или 0 В на SL2. Триггер переключится по алгоритму, описанному выше, и сохранит значение 0.

Элементы памяти на ТТЛ-элементах работают очень быстро. Но зато они отличаются высоким энергопотреблением.

72.3.1.2. Элементы памяти RAM в Ы-МОП-исполнении

Элементы памяти RAM в TV-МОП-исполнении имеют по сравнению с ТТЛ-элементами существенные преимущества. Они потребляют меньше энергии и могут производиться с более высокой степенью интеграции. На квадратном миллиметре чипа может размещаться больше МОП-элементов памяти. Однако МОП-схемы имеют большее время переключения, т. е. они медленнее ТТЛ-схем (см. гл. 6 «Семейства схем»).

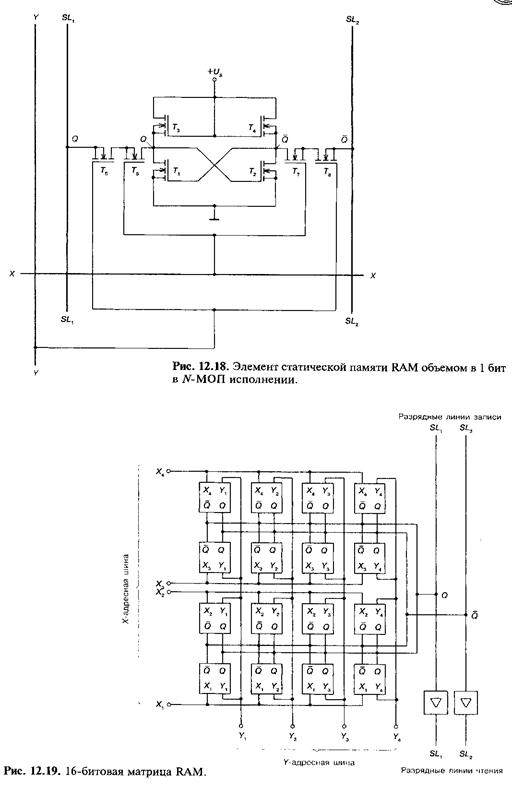

Структура типичного RAM-элемента представлена на рис. 12.18. Транзисторы Т{ и Т2 собраны по схеме триггера. Транзисторы Т3 и Т4 работают вместо нагрузочных сопротивлений. Если Тг заперт, а Т2 открыт, то элемент памяти сохранил значение 1. При 0 Ту открыт, а Т2 заперт.

Активация элемента памяти

Элемент активизируется, если на адресные шины Хи Глодается 1-сигнал. Транзисторы Г5, Г6, Т7 и Г8 открываются и соединяют выходы триггера Q и

Q с линиями чтения—записи SLX и SL2.

Чтение

После активации ячейки памяти из нее можно считывать данные. Если SLX проводит 1-сигнал, то элемент сохраняет единицу. Если SL2 проводит 1-сигнал, то элемент сохраняет 0.

Запись

В элемент памяти, содержащий 0, требуется записать 1. При О Тх открыт, а Т2 заперт. Если на SL2 действует 0-сигнал, то Тх запирается, а Т2 открывается. Триггер переключается в 1-состояние. Это состояние сохраняется после завершения активации.

72.3.7.3. Структура RAM с двухкоординатной адресацией

RAM-элементы памяти собираются в RAM-матрицы памяти. Матрица на рис. 12.19 имеет объем памяти 16 бит. Каждый элемент доступен индивидуально. Говорят, что каждый бит может быть адресован. Если бы мы хотели узнать, например, содержимое памяти запоминающего элемента 8, то на адресных шинах Х3 и Y4 должен быть 1-сигнал. На разрядных линиях SLX и

SL2 появляются выходные сигналы Q и Q.

12.3.2. Динамические ОЗУ (DRAM)

12.3.2.1. Элемент памяти динамического ОЗУ

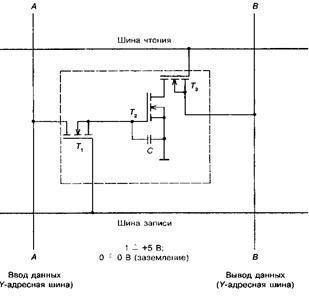

Типичный элемент памяти динамического ОЗУ состоит из трех самозапирающихся MOS-FET-транзисторов согласно рис. 12.20. Информация сохраняется в емкости С. Если С заряжен, то элемент памяти содержит 1. Если С не заряжен, то элемент памяти содержит 0.

Запись

| l |

| l |

|

| X |

| Рис. 12.20. Типичный элемент памяти динамической RAM. |

Запоминающий элемент активизируется 1-сигналом на шине чтения X (1-сигнал = +5 В).

Вследствие этого транзистор Тх открывается (низкоомен между истоком и стоком). При подаче на информационный вход 1-сигнала емкость С заряжается. Значение 1 сохранено. При заряженном конденсаторе С транзистор Т2 всегда низкоомен (открыт). Если на адресной шине X действует 0-сигнал, то элемент памяти больше не активизирован. Транзистор Тх запирается и предотвращает утечку заряда С. Для записи 0 следует активизировать элемент памяти (1-сигнал на адресной шине X). При этом Тх отпирается. Если 0-сигнал (0 = О В, земля) прикладывается на линию входных данных А, то емкость С может разрядиться через транзистор Tv Значение 0 сохранено. При разряженном конденсаторе С транзистор Т2 всегда заперт.

Чтение

Для считывания данных на шину вывода В прикладывается 1-сигнал (+ 5 В). Элемент памяти активизируется через шину чтения L. На L также прикладывается 1. При этом транзистор Т3 открывается.

Если записана 1, то транзистор Тъ открыт и ток через шину В через Г3 и Т2 течет на землю. Это признак записанной 1.

Если записан 0, то С разряжен, а Т2 заперт. Через шину В ток течь не может. Это признак записанного 0.

Во время чтения содержание элемента памяти не меняется.

Регенерация

Емкость С очень мала. Она составляет в зависимости от степени интеграции от 0,1 пФ до 1 пФ. Соответственно мал и сохраненный заряд. Очень маленький ток утечки быстро понижает заряд. Поэтому заряд должен быть через короткие промежутки времени снова восстановлен. Обычно подзарядка происходит каждые 2 мс.

Цикл регенерации начинается с чтения содержимого элемента памяти. Если оно равно 1, то Тх открывается и С заряжается. Если содержание памяти 0, то зарядка не происходит.

Для регенерации необходим особенный задающий генератор синхронизирующих импульсов и схема управления. Оба этих элемента включены в состав микросхем.

12.3.2.2. Особенности динамических ОЗУ

Динамические ОЗУ работают очень надежно. Это удивительно, если учесть, что хранимая информация должна быть примерно каждые 2 мс обновлена. Можно было бы предположить, что какой-нибудь бит пропадает. Однако этого не происходит.

Преимуществом динамических ОЗУ является большой объем памяти чипа или микросхемы. МОП-техника позволяет достичь высокой степени интеграции. Запоминающие элементы могут быть очень малы. Предложенное в настоящее время самое большое динамическое ОЗУ имеет объем памяти 4 Мбит (1 Мбит = 1048576 бит, приблизительно 1 млн бит). 4 Мбит могут сохраняться в одной-единственной микросхеме. В разработке находится схема с 16 Мбит.

Недостатком является относительно большое время переключения. Так называемое время доступа лежит в интервале между 100 не и 300 не. Под временем доступа понимают максимальное время, которое проходит от адресации элемента памяти до возможности работать с его данными.

Во время регенерации динамическое ОЗУ должно быть блокировано от записи и чтения, иначе будут возникать ошибки.

С ростом температуры кристалла токи утечки будут расти. Емкости будут разряжаться быстрее. Рекомендованная производителем частота регенерации рассчитана на рабочую температуру 70 °С. Если эта температура будет превышена, то данные могут быть потеряны.

12.3.3. Организация элементов памяти и ее параметры

12.3.3.1. Организация элементов памяти

Статические и динамические ОЗУ предлагаются с различными объемами памяти и различными структурами.

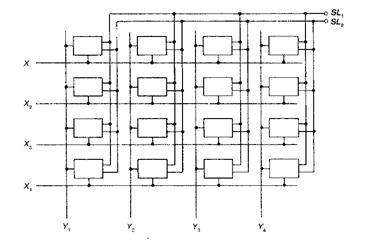

Адресуемая ячейка памяти может состоять из одного элемента или из нескольких элементов. Если она состоит только из одного элемента, то такая память называется памятью с побитовой организацией. Каждый запоминающий элемент, то есть каждый бит, имеет собственный адрес и является, таким образом, адресуемым. Конструктивная схема такой памяти показана на рис. 12.21. Обозначение 16 х 1 значит: совокупная емкость 16 бит, емкость ячейки памяти 1 бит.

Рис. 12.21. Структура памяти 16 х 1.

Если ячейка памяти состоит из нескольких запоминающих элементов, то память является пословно организованной. На рис. 12.22 показана конструктивная схема 32 х 8-битово элемент является адресуемым. Все 8 бит ячейки памяти всегда записываются и считываются одновременно.

Для 256 х 1-памяти необходимы 16 Х-адресных шин и 16 7-адресных шин (рис. 12.23). Выводить эти шины наружу в порты микросхемы неудобно. Эта схема имела бы очень много выводов. Поэтому применяются дешифраторы (см. разд. 11.2). Для выбора 16 элементов памяти нужны 4 адресных линии. Адресные линии выводятся на ножки микросхемы.

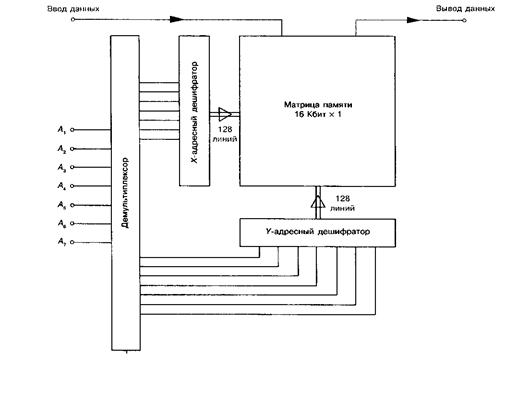

Рис. 12.24. Структура памяти 16 Кбит х 1 с дешифратором и демультиплексором.

демультиплексор (см. разд. 11.1). На входы от Ах до А7 сначала подается Х-адрес, затем F-адрес. Переключение происходит сигналом управления S. Мультиплексирование адресов позволяет применять небольшие корпуса ИС.

12.3.3.2. Параметры памяти

Для выбора памяти большое значение имеют ее параметры. В основном это емкость и структура, производительность и энергопотребление. Далее также важны электрические условия эксплуатации и допустимый рабочий диапазон. Рассмотрим по очереди самые важные параметры памяти.

Емкость

Емкость показывает количество элементов памяти, содержащихся в матрице, т. е. число бит, которые могут быть сохранены.

Структура памяти

Характеризует объем памяти одной ячейки и способ адресации.

Время доступа

Время доступа является временем, которое проходит от момента адресации элемента памяти (ЭП) до возможности располагать информацией на выходе данных.

Рис. 12.23Структура памяти 256 х 1 с дешифратором.

Рис. 12.23 Структура памяти 256х1 с дешифратором

Как организованы адресные шины в 16 Кбит х 1-битовой памяти? Должны быть адресованы 16 384 бит. Кроме этого, требуются 128 Х-адресных линии и 128 Y-адресных линии. Для выбора 128 адресных линий необходимо иметь 7 управляющих выводов (рис. 12.24). Всего на выводы микросхемы нужно выводить 14 адресных линий. Так как требуются еще информационные выводы для ввода—вывода данных и для команд управления, то получается очень большое число выводов. Чтобы этого избежать, ставят

Длительность цикла обработки

Под длительностью цикла обработки понимают минимальное время между двумя следующими друг за другом процессами чтения—записи.

Энергопотребление

Указывается общее энергопотребление всей микросхемы. Оно может варьироваться в зависимости от режима работы.

Электрические условия эксплуатации

Здесь указываются необходимые напряжения питания, необходимые уровни сигнала и диапазоны допустимых значений (см. гл. 6 «Семейства схем»), а также предельные значения других электрических величин.

Диапазон рабочих температур

Диапазон рабочих температур — диапазон температур, в котором память стабильно работает в рамках предписанных электрических условий эксплуатации.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 2106; Нарушение авторских прав?; Мы поможем в написании вашей работы!