КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Современная оперативная память

|

|

|

|

SDRAM: Определение

Аббревиатура SDRAM расшифровывается как S ynchronous D ynamic R andom A ccess M emory — синхронная динамическая память с произвольным доступом. Остановимся подробнее на каждом из этих определений. Под «синхронностью» обычно понимается строгая привязка управляющих сигналов и временных диаграмм функционирования памяти к частоте системной шины. Вообще говоря, в настоящее время изначальный смысл понятия синхронности становится несколько условным. Во-первых, частота шины памяти может отличаться от частоты системной шины (в качестве примера можно привести уже сравнительно давно существующий «асинхронный» режим работы памяти DDR SDRAM на платформах AMD K7 с чипсетами VIA KT333/400, в которых частоты системной шины процессора и шины памяти могут соотноситься как 133/166 или 166/200 МГц). Во-вторых, ныне существуют системы, в которых само понятие «системной шины» становится условным — речь идет о платформах класса AMD Athlon 64 с интегрированным в процессор контроллером памяти. Частота «системной шины» (под которой в данном случае понимается не шина HyperTransport для обмена данными с периферией, а непосредственно «шина» тактового генератора) в этих платформах является лишь опорной частотой, которую процессор умножает на заданный коэффициент для получения собственной частоты. При этом контроллер памяти всегда функционирует на той же частоте, что и сам процессор, а частота шины памяти задается целым делителем, который может не совпадать с первоначальным коэффициентом умножения частоты «системной шины». Так, например, режиму DDR-333 на процессоре AMD Athlon 64 3200+ будут соответствовать множитель частоты «системной шины» 10 (частота процессора и контроллера памяти 2000 МГц) и делитель частоты памяти 12 (частота шины памяти 166.7 МГц). Таким образом, под «синхронной» операцией SDRAM в настоящее время следует понимать строгую привязку временн ы х интервалов отправки команд и данных по соответствующим интерфейсам устройства памяти к частоте шины памяти (проще говоря, все операции в ОЗУ совершаются строго по фронту/срезу синхросигнала интерфейса памяти). Так, отправка команд и чтение/запись данных может осуществляться на каждом такте шины памяти (по положительному перепаду — «фронту» синхросигнала; в случае памяти DDR/DDR2 передача данных происходит как по «фронту», так и по отрицательному перепаду — «срезу» синхросигнала), но не по произвольным временным интервалам (как это осуществлялось в асинхронной DRAM).

|

|

|

Понятие «динамической» памяти, DRAM, относится ко всем типам оперативной памяти, начиная с самой древней, «обычной» асинхронной динамической памяти и заканчивая современной DDR2. Этот термин вводится в противоположность понятия «статической» памяти (SRAM) и означает, что содержимое каждой ячейки памяти периодически необходимо обновлять (ввиду особенности ее конструкции, продиктованной экономическими соображениями). В то же время, статическая память, характеризующаяся более сложной и более дорогой конструкцией ячейки и применяемая в качестве кэш-памяти в процессорах (а ранее — и на материнских платах), свободна от циклов регенерации, т.к. в ее основе лежит не емкость (динамическая составляющая), а триггер (статическая составляющая).

Наконец, стоит также упомянуть о «памяти с произвольным доступом» — Random Access Memory, RAM. Традиционно, это понятие противопоставляется устройствам «памяти только на чтение» — Read-Only Memory, ROM. Тем не менее, противопоставление это не совсем верно, т.к. из него можно сделать вывод, что память типа ROM не является памятью с произвольным доступом. Это неверно, потому как доступ к устройствам ROM может осуществляться в произвольном, а не строго последовательном порядке. И на самом деле, наименование «RAM» изначально противопоставлялось ранним типам памяти, в которых операции чтения/записи могли осуществляться только в последовательном порядке. В связи с этим, более правильно назначение и принцип работы оперативной памяти отражает аббревиатура «RWM» (Read-Write Memory), которая, тем не менее, встречается намного реже. Заметим, что русскоязычным сокращениям RAM и ROM — ОЗУ (оперативное запоминающее устройство) и ПЗУ (постоянное запоминающее устройство), соответственно, подобная путаница не присуща.

|

|

|

Микросхемы SDRAM: Физическая организация и принцип работы

Общий принцип организации и функционирования микросхем динамической памяти (DRAM) практически един для всех ее типов — как первоначальной асинхронной, так и современной синхронной. Исключение составляют разве что экзотические варианты, тем не менее, существовавшие еще до появления SDRAM, вроде Direct Rambus DRAM (DRDRAM). Массив памяти DRAM можно рассматривать как матрицу (двумерный массив) элементов (строго говоря, это понятие относится к логическому уровню организации микросхемы памяти), каждый из которых содержит одну или несколько физических ячеек (в зависимости от конфигурации микросхемы), способных вмещать элементарную единицу информации — один бит данных. Ячейки представляют собой сочетание транзистора (ключа) и конденсатора (запоминающего элемента). Доступ к элементам матрицы осуществляется с помощью декодеров адреса строки и адреса столбца, которые управляются сигналами RAS# (сигнал выбора строки — Row Access Strobe) и CAS# (сигнал выбора столбца — Column Access Strobe).

Из соображений минимизации размера упаковки микросхемы, адреса строк и столбцов передаются по одним и тем же адресным линиям микросхемы — иными словами, говорят о мультиплексировании адресов строк и столбцов (упомянутые выше отличия в общих принципах функционирования микросхем DRDRAM от «обычных» синхронных/асинхронных DRAM проявляются, в частности, здесь — в этом типе микросхем памяти адреса строк и столбцов передаются по разным физическим интерфейсам). Так, например, 22-разрядный полный адрес ячейки может разделяться на два 11-разрядных адреса (строки и столбца), которые последовательно (через определенный интервал времени, см. раздел «Тайминги памяти») подаются на адресные линии микросхемы памяти. Одновременно со второй частью адреса (адреса столбца) по единому командно-адресному интерфейсу микросхемы SDRAM подается соответствующая команда (чтения или записи данных). Внутри микросхемы памяти адреса строки и столбца временно сохраняются в буферах (защелках) адреса строки и адреса столбца, соответственно.

|

|

|

Важно заметить, что с динамической матрицей памяти связан особый буфер статической природы, именуемый «усилителем уровня» (SenseAmp), размер которого равен размеру одной строки, необходимый для осуществления операций чтения и регенерации данных, содержащихся в ячейках памяти. Поскольку последние физически представляют собой конденсаторы, разряжающиеся при совершении каждой операции чтения, усилитель уровня обязан восстановить данные, хранящиеся в ячейке, после завершения цикла доступа (более подробно участие усилителя уровня в цикле чтения данных из микросхемы памяти рассмотрено ниже).

Кроме того, поскольку конденсаторы со временем теряют свой заряд (независимо от операций чтения), для предотвращения потери данных необходимо периодически обновлять содержимое ячеек. В современных типах памяти, которые поддерживают режимы автоматической регенерации (в «пробужденном» состоянии) и саморегенерации (в «спящем» состоянии), обычно это является задачей внутреннего контроллера регенерации, расположенного непосредственно в микросхеме памяти.

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

1. На адресные линии микросхемы памяти подается адрес строки. Наряду с этим подается сигнал RAS#, который помещает адрес в буфер (защелку) адреса строки.

2. После стабилизации сигнала RAS#, декодер адреса строки выбирает нужную строку, и ее содержимое перемещается в усилитель уровня (при этом логическое состояние строки массива инвертируется).

3. На адресные линии микросхемы памяти подается адрес столбца вместе с подачей сигнала CAS#, помещающего адрес в буфер (защелку) адреса столбца.

|

|

|

4. Поскольку сигнал CAS# также служит сигналом вывода данных, по мере его стабилизации усилитель уровня отправляет выбранные (соответствующие адресу столбца) данные в буфер вывода.

5. Сигналы CAS# и RAS# последовательно дезактивируются, что позволяет возобновить цикл доступа (по прошествии промежутка времени, в течение которого данные из усилителя уровня возвращаются обратно в массив ячеек строки, восстанавливая его прежнее логическое состояние).

Так выглядела реальная схема доступа к ячейке DRAM в самом первоначальном ее варианте, реализованном еще до появления первых реально используемых микросхем/модулей асинхронной памяти типа FPM (Fast Page Mode) DRAM. Тем не менее, нетрудно заметить, что эта схема является достаточно неоптимальной. Действительно, если нам требуется считать содержимое не одной, а сразу нескольких подряд расположенных ячеек, отличающихся только адресом столбца, но не адресом строки, то нет необходимости каждый раз подавать сигнал RAS# с одним и тем же адресом строки (т.е. выполнять шаги 1-2). Вместо этого, достаточно удерживать сигнал RAS# активным на протяжении промежутка времени, соответствующего, например, четырем последовательным циклам чтения (шаги 3-4, с последующей дезактивацией CAS#), после чего дезактивировать сигнал RAS#. Именно такая схема применялась в асинхронной памяти типа FPM DRAM и более поздней EDO (Enhanced Data Output) DRAM. Последняя отличалась опережающей подачей адреса следующего столбца, что позволяло достичь меньших задержек при операциях чтения.

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

А пока перейдем к рассмотрению организации микросхем памяти SDRAM на логическом уровне. Как уже было сказано выше, микросхема DRAM, фактически, представляет собой двумерный массив (матрицу) элементов, состоящих из одного или нескольких элементарных физических ячеек. Очевидно, что главной характеристикой этого массива является его емкость, выражаемая в количестве бит информации, которую он способен вместить. Часто можно встретить понятия «256-Мбит», «512-Мбит» микросхем памяти — речь здесь идет именно об этом параметре. Однако составить эту емкость можно разными способами — мы говорим сейчас не о количестве строк и столбцов, но о размерности, или «вместимости» индивидуального элемента. Последняя прямо связана с количеством линий данных, т.е. шириной внешней шины данных микросхемы памяти (но не обязательно с коэффициентом пропорциональности в единицу, что мы увидим ниже, при рассмотрении отличий памяти типа DDR и DDR2 SDRAM от «обычной» SDRAM). Ширина шины данных самых первых микросхем памяти составляла всего 1 бит, в настоящее же время наиболее часто встречаются 4-, 8- и 16- (реже — 32-) битные микросхемы памяти. Таким образом, микросхему памяти емкостью 512 Мбит можно составить, например, из 128М (134 217 728) 4-битных элементов, 64М (67 108 864) 8-битных элементов или 32М (33 554 432) 16-битных элементов — соответствующие конфигурации записываются как «128Mx4», «64Mx8» и «32Mx16». Первая из этих цифр именуется глубиной микросхемы памяти (безразмерная величина), вторая — шириной (выраженная в битах).

Существенная отличительная особенность микросхем SDRAM от микросхем более ранних типов DRAM заключается в разбиении массива данных на несколько логических банков (как минимум — 2, обычно — 4). Не следует путать это понятие с понятием «физического банка» (называемого также «ранком» (rank) памяти), определенным для модуля, но не микросхемы памяти — его мы рассмотрим далее. Сейчас лишь отметим, что внешняя шина данных каждого логического банка (в отличие от физического, который составляется из нескольких микросхем памяти для «заполнения» шины данных контроллера памяти) характеризуется той же разрядностью (шириной), что и разрядность (ширина) внешней шины данных микросхемы памяти в целом (x4, x8 или x16). Иными словами, логическое разделение массива микросхемы на банки осуществляется на уровне количества элементов в массиве, но не разрядности элементов. Таким образом, рассмотренные выше реальные примеры логической организации 512-Мбит микросхемы при ее «разбиении» на 4 банка могут быть записаны как 32Mx4x4 банка, 16Mx8x4 банка и 8Mx16x4 банка, соответственно. Тем не менее, намного чаще на маркировке микросхем памяти (либо ее расшифровке в технической документации) встречаются именно конфигурации «полной» емкости, без учета ее разделения на отдельные логические банки, тогда как подробное описание организации микросхемы (количество банков, строк и столбцов, ширину внешней шины данных банка) можно встретить лишь в подробной технической документации на данный вид микросхем SDRAM.

Разбиение массива памяти SDRAM на банки было введено, главным образом, из соображений производительности (точнее, минимизации системных задержек — т.е. задержек поступления данных в систему). В самом простом и пока достаточном изложении, можно сказать, что после осуществления любой операции со строкой памяти, после дезактивации сигнала RAS#, требуется определенное время для осуществления ее «подзарядки». И преимущество «многобанковых» микросхем SDRAM заключается в том, что можно обращаться к строке одного банка, пока строка другого банка находится на «подзарядке». Можно расположить данные в памяти и организовать к ним доступ таким образом, что далее будут запрашиваться данные из второго банка, уже «подзаряженного» и готового к работе. В этот момент вполне естественно «подзаряжать» первый банк, и так далее. Такая схема доступа к памяти называется «доступом с чередованием банков» (Bank Interleave).

Модули SDRAM: Организация

Основные параметры логической организации микросхем памяти — емкость, глубину и ширину, можно распространить и на модули памяти типа SDRAM. Понятие емкости (или объема) модуля очевидно — это максимальный объем информации, который данный модуль способен в себя вместить. Теоретически он может выражаться и в битах, однако общепринятой «потребительской» характеристикой модуля памяти является его объем (емкость), выраженный в байтах — точнее, учитывая современный уровень используемых объемов памяти — в мега-, или даже гигабайтах.

Ширина модуля — это разрядность его интерфейса шины данных, которая соответствует разрядности шины данных контроллера памяти и для всех современных типов контроллеров памяти SDRAM (SDR, DDR и DDR2) составляет 64 бита. Таким образом, все современные модули характеризуются шириной интерфейса шины данных «x64». Каким же образом достигается соответствие между 64-битная шириной шины данных контроллера памяти (64-битным интерфейсом модуля памяти), когда типичная ширина внешней шины данных микросхем памяти обычно составляет всего 4, 8 или 16 бит? Ответ очень прост — интерфейс шины данных модуля составляется простым последовательным «слиянием» внешних шин данных индивидуальных микросхем модуля памяти. Такое «заполнение» шины данных контроллера памяти принято называть составлением физического банка памяти. Таким образом, для составления одного физического банка 64-разрядного модуля памяти SDRAM необходимо и достаточно наличие 16 микросхем x4, 8 микросхем x8 (это наиболее часто встречаемый вариант) или 4 микросхем x16.

Оставшийся параметр — глубина модуля, являющийся характеристикой емкости (вместимости) модуля памяти, выраженной в количестве «слов» определенной ширины, вычисляется, как нетрудно догадаться, простым делением полного объема модуля (выраженного в битах) на его ширину (разрядность внешней шины данных, также выраженную в битах). Так, типичный 512-МБ модуль памяти SDR/DDR/DDR2 SDRAM имеет глубину, равную 512МБайт * 8 (бит/байт) / 64 бита = 64М. Соответственно, произведение ширины на глубину дает полную емкость модуля и определяет его организацию, или геометрию, которая в данном примере записывается в виде «64Мx64».

Возвращаясь к физическим банкам модуля памяти, заметим, что при использовании достаточно «широких» микросхем x8 или x16 ничего не мешает поместить и большее их количество, соответствующее не одному, а двум физическим банкам — 16 микросхем x8 или 8 микросхем x16. Так различают однобанковые (или «одноранковые», single-rank) и двухбанковые («двухранковые», dual-rank) модули. Двухбанковые модули памяти наиболее часто представлены конфигурацией «16 микросхем x8», при этом один из физических банков (первые 8 микросхем) расположен с лицевой стороны модуля, а второй из них (оставшиеся 8 микросхем) — с тыльной. Наличие более одного физического банка в модуле памяти нельзя считать определенным преимуществом, т.к. может потребовать увеличения задержек командного интерфейса, которые рассмотрены в соответствующем разделе.

Модули памяти: Микросхема SPD

Еще до появления первого типа синхронной динамической оперативной памяти SDR SDRAM стандартом JEDEC предусматривается, что на каждом модуле памяти должна присутствовать небольшая специализированная микросхема ПЗУ, именуемая микросхемой «последовательного обнаружения присутствия» (Serial Presence Detect, SPD). Эта микросхема содержит основную информацию о типе и конфигурации модуля, временных задержках (таймингах, см. следующий раздел), которых необходимо придерживаться при выполнении той или иной операции на уровне микросхем памяти, а также прочую информацию, включающую в себя код производителя модуля, его серийный номер, дату изготовления и т.п. Последняя ревизия стандарта SPD модулей памяти DDR2 также включает в себя данные о температурном режиме функционирования модулей, которая может использоваться, например, для поддержания оптимального температурного режима посредством управления синхронизацией (регулированием скважности импульсов синхросигнала) памяти (так называемый «троттлинг памяти», DRAM Throttle).

Постоянные запоминающие устройства (ПЗУ, ROM)

ПЗУ (ROM) содержат нестираемую и неизменяемую информацию. Понятие ROM является сокращением от Read Only Memory.

ПЗУ можно сравнить с книгой. Занесенная в нее информация является доступной в любое время. Однако невозможно заменить или изменить информацию. В ПЗУ сохраняют часто используемые сведения, например команды, программы и таблицы. По мере необходимости могут быть считаны отдельные ячейки таблицы.

Для организации ПЗУ применяют два типа запоминающих элементов. Запоминающие элементы первого типа должны всегда содержать значение 1. Запоминающие элементы второго типа должны всегда содержать значение 0.

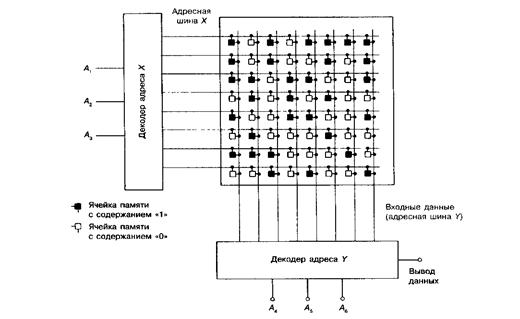

Представление данных в памяти и организация памяти ПЗУ похожи на ОЗУ. Запоминающая матрица состоит из строк и столбцов. Отдельные ячейки памяти выбираются адресацией (рис. 12.29).

Рис 12.29. Схема 64 х 1 битового ПЗУ.

ПЗУ производятся чаще всего в TV-МОП-технике. Возможная степень интеграции велика, а энергопотребление незначительно. Как построен запоминающий элемент, который всегда содержит значение 1? Это можно сделать с помощью отсутствующего TV-МОП-транзистора. Запоминающий элемент, который всегда имеет значение 0, образуется TV-МОП-транзисто-ром (рис. 12.30).

7-адресные шины являются одновременно линиями данных. Если запоминающий элемент считывается, на Г-адресную шину прикладывается 1-сигнал.

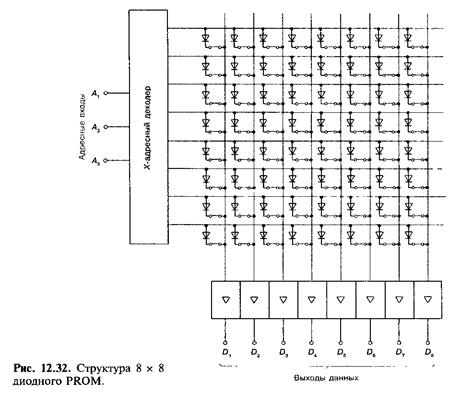

Программируемое постоянное запоминающее устройство (ППЗУ, PROM)

Если выбранный запоминающий элемент является 0-элементом, то на линии данных действует 0-сигнал, транзистор открыт и связывает линию данных с землей.

Если выбранный запоминающий элемент является 1-элементом, то на линии данных действует 1-сигнал. На линии данных не может быть 0-сигнал, так как транзистор отсутствует.

Постоянные запоминающие устройства этого вида называются также масочными ПЗУ. Информация записывается при изготовлении. Покрытием (маскированием) на определенных участках предотвращается изготовление полевых транзисторов. Пользователь должен указать заранее, какая информация должна быть записана и соответственно где должны и где не должны быть размещены полевые транзисторы.

Изготовление ПЗУ является экономически обоснованным только при массовом производстве, так как для каждого информационного наполнения должна быть изготовлена соответствующая маска.

ваемое программатор. Программирование ППЗУ необратимо. В случае ошибки ППЗУ можно выбрасывать. Коррекция возможна только в редких случаях, если можно дополнительно прожечь оставшиеся соединения.

12.6. Перепрограммируемые постоянные запоминающие устройства

Стираемые и программируемые постоянные запоминающие устройства позволяют удалять введенную информацию и перепрограммировать ПЗУ.

Удаление и перепрограммирование может повторяться как угодно часто без повреждения модуля памяти.

Различают две группы перепрограммируемых постоянных запоминающих устройств. В одной группе информация удаляется ультрафиолетовым светом. Постоянные запоминающие устройства этой разновидности называются СППЗУ — стираемое программируемое постоянное запоминающее устройство (EPROM — Erasable Programmable Read Only Memory или REPROM — Re-programmable Read Only Memory).

Стираемые программируемые постоянные запоминающие устройства второй группы перепрограммируются электрическим напряжением. Для них принято сокращение EEROM (Electrically Erasable Read Only Memory = электрически стираемые постоянные запоминающие устройства) и EAROM (Electrically Alterable Read Only Memory — электрически перепрограммируемые постоянные запоминающие устройства).

12.6.1. EPROM и REPROM

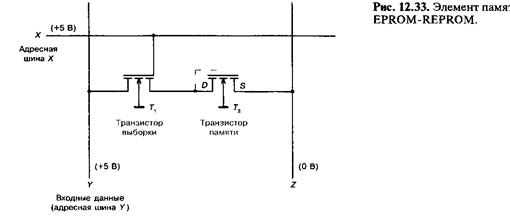

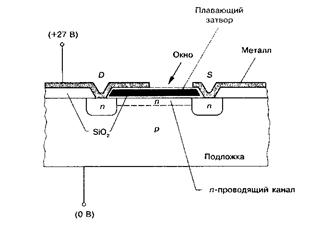

EPROM и REPROM незначительно отличаются друг от друга, в основном технологией изготовления. Они идентичны по структуре и принципу действия и поэтому могут рассматриваться вместе. СППЗУ (стираемое программируемое постоянное запоминающее устройство) и REPROM-запоми-нающий элемент для 1-го бита состоят из двух полевых транзисторов, в основном применяются TV-МОП полевые транзисторы. Структура типичного элемента памяти представлена на рис. 12.33. Транзистор Тх является транзистором выборки, транзистор Т2 — транзистором памяти.

Затвор транзистора памяти Т2 окружен материалом с высоким сопротивлением. Он ни к чему не присоединен. Такой затвор называется плавающим (англ. floating-gate). В стертом состоянии плавающий затвор не заряжен. Транзистор Т2 заперт. Если на адресные шины Хи Yпомещают +5 В, то транзистор Тх откроется. Однако транзистор Т2 заперт, так что 7-шина, которая одновременно является шиной данных, не может сброситься на L = 0. 7-шина остается на уровне 1. В стертой памяти типа EPROM и REPROM все элементы памяти имеют содержание Н = 1.

При вводе данных нужные элементы перепрограммируются на 0. Говорят, что программируются «нули».

Запоминающий элемент имеет содержание памяти 0, если транзистор памяти открыт.

Если адресуется элемент с открытым транзистором памяти Tv т. е. на X-шину и 7-шину подано +5 В, то Тх также открывается. Так как на шине Z действует О В, то шина Y разряжается до уровня приблизительно О В. Как добиться, чтобы транзистор памяти открылся? Нужно зарядить его затвор.

Плавающий затвор А/-МОП-транзистора должен быть заряжен положительно по отношению к подложке, образуя п-проводящий мостик между истоком (Source) и стоком (Drain).

Рассмотрим структуру транзистора памяти (рис. 12.34). Между D и подложкой прикладывается относительно высокое напряжение (+27 В). Так как плавающий затвор и изоляционный слой очень тонкие, то возникает очень сильное электрическое поле. Под влиянием этого сильного поля электроны от плавающего затвора перемещаются к стоку (против линий поля). Изоляционный слой пропускает электроны из-за очень высокой электрической напряженности поля. Можно сказать, что изоляционный слой кратковременно проламывается. На самом деле причиной является туннельный эффект. Этот процесс называется Floating Gate — avalanche-injection (англ. — лавинная зарядка плавающего затвора). МОП-полевой транзистор, заряжающийся по этому принципу, называется FAMOS-транзистор.

Напряжение +27 В называется напряжением программирования. После кратковременного действия этого напряжения затвор заряжается. Материал, окружающий плавающий затвор, является высокоомным. Элект-риче-ский заряд на нем сохраняется. На подложке под плавающим затвором возникает я-проводящий мостик. Полевой транзистор низкоомен между S и D.

Ячейки памяти СППЗУ (стираемое программируемое постоянное запоминающее устройство) или REPROM программируются по очереди после выбора адресными шинами Хж 7 (см. рис. 12.33). К Хи 7прикладываются напряжения выборки +5 В. Вследствие этого открывается Tv Напряжение 7-шины кратковременно повышается до +27 В. Программирование может неоднократно повторяться по соображениям надежности. По данным производителя, заряд на плавающем затворе сохраняется в течение многих лет, то есть данные могут сохраняться от 1 года до 100 лет.

Запрограммированные СППЗУ и REPROM сохраняют введенную информацию.

Известные производители дают гарантию от 10 лет на сохранность данных.

Для удаления информации из СППЗУ или REPROM стираемый участок через окно над плавающим затвором облучается ультрафиолетом.

Высокоомный материал ионизируется облучением и начинает проводить. Затвор медленно разряжается. При мощности излучения примерно 10 Вт • с/см2 затвор разряжается за 20—30 минут. Корпус СППЗУ и REPROM имеет окно, проходящее над всей поверхностью кристаллического чипа (рис. 12.35). Ультрафиолетовый свет облучает все элементы памяти и стирает их все одновременно.

Рис. 12.35. Корпус EPROM-REPROM.

При стирании из СППЗУ и REPROM удаляется вся информация.

После удаления информации модуль должен остыть, так как он заметно нагревается. Прежде всего должна уменьшиться ионизация в изолирующем материале. Материал должен снова стать высокоомным. Только тогда можно снова начинать цикл программирования. Время охлаждения должно составлять по меньшей мере половину от времени программирования, лучше всего час.

Находящиеся на свету СППЗУ и REPROM могут быть случайно стерты.

Лучи солнечного света приводят к стиранию микросхемы в течение примерно 3 дней. Свет люминесцентной лампы удаляет информацию примерно через 3 недели. Чтобы предотвратить случайное стирание, целесообразно заклеить окно темным скотчем.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 2059; Нарушение авторских прав?; Мы поможем в написании вашей работы!