КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекция 11. Последовательный периферийный интерфейс SPI

Последовательный периферийный интерфейс SPI (Serial Peripheral Interface) представляет собой полнодуплексный четырехпроводный интерфейс с шинной конфигурацией подключаемых узлов (устройств). SPI интерфейс позволяет подключать к одному ведущему узлу несколько ведомых узлов через общую шину. Отдельный сигнал NSS (Slave-Select signal) выбора ведомого устройства используется для выбора ведомого устройства при осуществлении с ним обмена данными. Кроме того, возможно также построение системы со многими ведущими узлами. Обнаружение конфликтов при одновременной передаче нескольких ведущих узлов также предусмотрено.

Интерфейс SPI может быть запрограммирован для работы в качестве ведущего или ведомого. Если интерфейс запрограммирован как ведущий, он может работать на максимальной скорости передачи данных (бит/с), равной половине тактовой частоты. Если интерфейс запрограммирован для работы в качестве ведомого, его максимальная скорость в полнодуплексном режиме равняется одной десятой тактовой частоты. Подразумевается, что источником синхронизации в обоих случаях является системный генератор тактовой частоты. Если ведущий интерфейс вырабатывает SCK, NSS и последовательные входные данные асинхронно, максимальная скорость передачи должна быть меньше одной десятой тактовой частоты.

Существует еще один особенный режим, когда ведущий должен только передавать данные ведомому (полудуплексный режим) и не должен принимать данные от ведомого. В этом случае максимальная скорость передачи составляет одну четвертую от системной тактовой частоты при синхронном режиме работы.

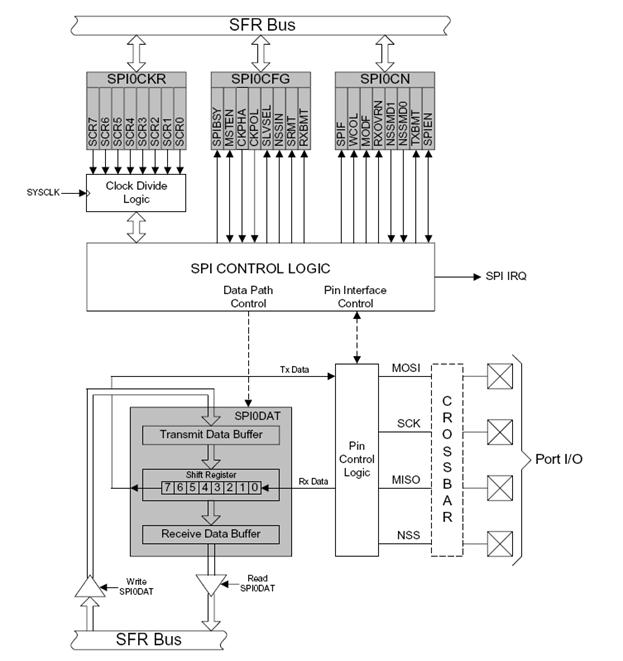

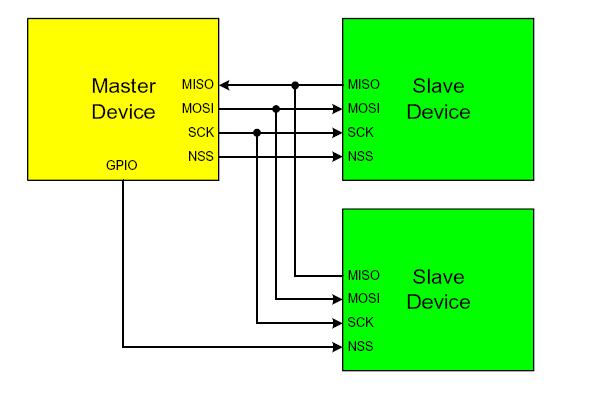

На рис. 11.1 показана функциональная схема работы SPI интерфейса, а на рис. 11.2 — типовая структурная схема SPI сети.

Рис. 11.1. Функциональная схема SPI интерфейса.

Интерфейс SPI имеет четыре сигнальные линии: MOSI, MISO, SCK и NSS.

Линия MOSI (Master-Out, Slave-In) — выходная линия данных ведущего интерфейса и входная линия данных ведомого интерфейса. Из названия следует, что линия предназначена для передачи данных от ведущего (Master) интерфейса (или узла сети) к ведомому (Slave) интерфейсу (или узлу сети).

Рис. 11.2. Типовая структурная схема SPI сети.

Линия MISO (Master-In, Slave-Out) — входная линия данных ведущего интерфейса и выходная линия данных ведомого интерфейса. Линия предназначена для передачи данных от ведомого интерфейса к ведущему. Данные передаются байтами, побитно, начиная со старшего бита. Следует помнить, что вывод MISO ведомого интерфейса находится в высокоимпедансном состоянии, если ведомый интерфейс не выбран по линии NSS.

Линия NSS (Slave Select) — линия выборки ведомого, предназначена для выборки низким логическим потенциалом ведомого интерфейса ведущим.

Линия SCK (Serial Clock) — выходная линия тактовых импульсов ведущего узла и входная линия тактовых импульсов ведомого узла. Линия SCK используется для синхронизации передачи данных между ведущим и ведомым интерфейсами по линиям MOSI и MISO.

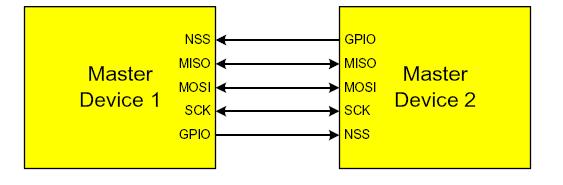

В сети на базе SPI интерфейсов только один интерфейс может быть ведущим. Интерфейс устанавливается в режим ведущего установкой флага MSTEN (Master Enable flag) — бита SPI0CN.1. Если интерфейс установлен в режим ведущего, то запись байта данных в регистр данных SPIODAT приводит к началу передачи. Ведущий интерфейс немедленно побитно сдвигает данные и выдает их на линию MOSI в сопровождении тактовых импульсов на линии SCK. После завершения передачи устанавливается флаг SPIF (SPIOCN.7). Если разрешены прерывания, выдается соответствующее прерывание. Кроме того, интерфейс может быть запрограммирован на выдачу от одного до восьми битов для осуществления связи с SPI приборами, имеющими различную длину слова. Длина передачи (количество передаваемых битов) может быть задана битами SPIFRS в регистре конфигурации SPI0CFG.[2:0] (SPI Configuration Register). Соединение двух интерфейсов SPI (ведущего и ведомого) показано на рис. 11.3.

Рис. 11.3. Соединение двух интерфейсов SPI.

Выше уже отмечалось, что интерфейс может работать в полнодуплексном режиме, это означает, что возможна одновременная передача данных по линиям MOSI от ведущего к ведомому и MISO от ведомого к ведущему. Данные, полученные от ведомого интерфейса, заменяют данные в регистре данных ведущего интерфейса. Этот регистр дважды буферизирован на ввод, но не на вывод. Таким образом, если в регистр данных SPI0DAT производится попытка записи данных во время передачи предыдущего байта, устанавливается флаг WCOL (SPIOCN.6), и попытка записи игнорируется. Таким образом, текущая передача данных продолжается непрерывно. Чтение из регистра данных SPI0DAT приводит к чтению приемного буфера. Если прием не закончен, устанавливается флаг RXOVRN (SPIOCN.4). Новые данные не передаются в регистр чтения, пока предыдущий принятый байт не будет прочитан. Очевидно, что при задержке чтения принятых байтов может произойти потеря данных. Если SPI интерфейс не настроен, как ведущий, он будет работать в режиме ведомого.

Кроме того, поддерживается режим сети с многими ведущими. Флаг MODF SPI0CN.5 (Mode Fault flag) устанавливается в лог. 1, если интерфейс определен как ведущий (MSTEN=1) и вывод NSS переведен в низкий логический уровень, т.е. если SPI интерфейс пытаются использовать в качестве ведомого. Если при этом установлен флаг MODF, биты MSTEN и SPIEN в регистре управления SPI стираются автоматически аппаратно, переводя интерфейс в автономное состояние. Таким образом, в системе с многими ведущими ядро может определить, свободна ли шина путем опроса флага SLVSEL (SPI0CN.2) перед тем, как установить MSTEN флаг (т. е. определить интерфейсу режим ведущего) и инициализировать обмен.

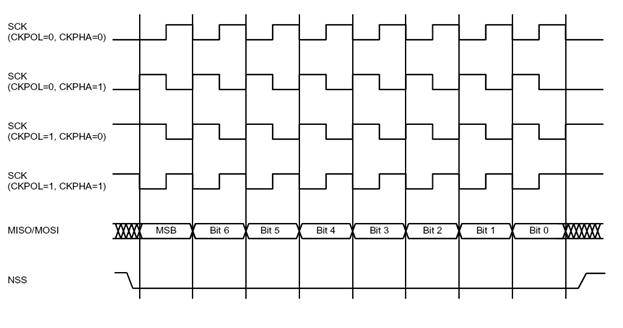

На рис. 11.4 показаны временные диаграммы работы SPI интерфейса. Возможны четыре комбинации фаз тактовых импульсов и их полярности в зависимости от комбинации управляющих битов в регистре конфигурации SPIOCFG (SPI Configuration Register). Бит СКРНА (SPIOCFG.7) выбирает одну

Рис. 11.4. Временные диаграммы работы SPI интерфейса.

из двух фаз тактовых импульсов, т. е. фронт, по которому осуществляется запись данных. Другой бит CKPOL (SPI0CFG.6) определяет активную полярность (высокий или низкий уровень). Очевидно, что и ведущий, и ведомый узлы должны иметь одинаковые настройки фазы и полярности. Еще одна важная особенность настройки заключается в том, что интерфейс SPI должен быть запрещен путем обнуления бита SPIEN (SPI0CN.0) на время настройки фазы и полярности тактовых импульсов.

Кроме описанных SFR регистров при настройке SPI интерфейса используются регистр настройки скорости передачи (SPI0CKR).

|

Дата добавления: 2014-01-07; Просмотров: 2014; Нарушение авторских прав?; Мы поможем в написании вашей работы!