КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Производительность

|

|

|

|

Для оценки производительности ПЛИС Virtex-5 воспользуемся тем же набором синтетических тестов, который был приведен автором в одной из предыдущих публикаций [1] для оценки производительности ПЛИС Virtex предыдущих семейств.

Набор тестов состоит из простого 16-разрядного счетчика, 16-разрядного АЛУ, выполняющего элементарные арифметические и логические операции над двумя операндами, и блока цифровой обработки, выполняющего перемножение 18-разрядных операндов с накоплением в 48-разрядном аккумуляторе. Результаты работы САПР приведены после этапа Translate, который дает верхнюю оценку тактовой частоты без учета задержек на трассировочных линиях. ПЛИС Virtex-5, как и прочие FPGA Xilinx, имеют так называемую speed grade, которая представляет собой интегральную оценку скорости микросхемы. ПЛИС с большим классом допускает большие тактовые частоты.

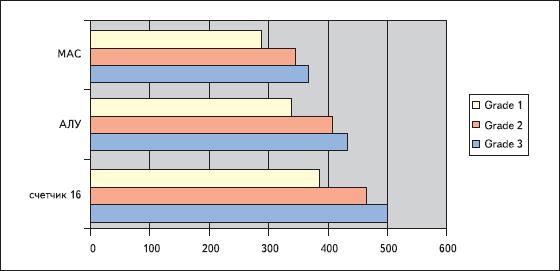

Можно отметить, что счетчик на Virtex-5 перешагнул барьер в 500 МГц (хотя и всего на 1 МГц), а операции «умножение с накоплением» можно выполнять на частотах 300–400 МГц. В данном тесте использовалась схема синхронного сброса аккумулятора, которая несколько снизила тактовую частоту по сравнению с заявленной производителем частотой 550 МГц, теоретически достижимой на выделенных умножителях (рис. 8).

Рис. 8. Тактовая частота проектов в ПЛИС семейства Virtex-5 (МГц) для различных классов скорости

При практической работе с высокопроизводительными ПЛИС имеет смысл уделять серьезное внимание алгоритмам трассировки и соответствующему размещению отдельных блоков на кристалле. Хорошие результаты получаются при использовании САПР PlanAhead, которая представляет собой один из новых продуктов Xilinx.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 284; Нарушение авторских прав?; Мы поможем в написании вашей работы!